# Novel Extended-Pi Shaped Silicon-Germanium (eΠ-SiGe) Source/Drain Stressors for Strain and Performance Enhancement in P-Channel FinFETs

Kian-Ming Tan,<sup>1</sup> Tsung-Yang Liow,<sup>1,2</sup> Rinus T. P. Lee<sup>1</sup>, Ming Zhu<sup>1</sup>, Keat Mun Hoe<sup>2</sup>, Chih-Hang Tung<sup>2</sup>, N. Balasubramanian,<sup>2</sup> Ganesh S. Samudra,<sup>1</sup> Yee-Chia Yeo.<sup>1</sup>

<sup>1</sup>Silicon Nano Device Lab., Dept of Electrical and Computer Engineering, National University of Singapore, 117576 Singapore. <sup>2</sup>Institute of Microelectronics, 11 Science Park Road, 117685 Singapore.

Phone: +65 6516-2298, Fax: +65 6779-1103, E-mail: yeo@ieee.org

# 1. INTRODUCTION

Mulitple-gate transistors or FinFETs offer excellent scalability beyond the 32 nm technology node. Strain engineering in FinFETs [1]-[3] is required to realize high performance levels commensurate with those of advanced planar FETs. Strained p-channel FinFETs with Si<sub>0.8</sub>Ge<sub>0.2</sub> source/drain (S/D) stressors formed on the top surface of the Si fin have been reported [3]. To better exploit the strain effects, the SiGe S/D stressor has to be grown on the fin sidewalls as well, forming a  $\Pi$ -shaped S/D stressor [1]-[2]. Nevertheless, even for fins stressed by the  $\Pi$ -shaped S/D, the stress distribution in the Si fin still shows lower stress at the foot of the fin due to limited SiGe growth (geometrical effects on epitaxial growth) or stressor volume, and the non-compliance of the buried oxide (BOX).

In this work, we report a novel extended-Pi SiGe ( $e\Pi$ -SiGe) S/D stressor with significantly enhanced strain effects to boost the performance of p-channel FinFETs. Compared to FinFETs with  $\Pi$ -shaped SiGe S/D, FinFETs with the  $e\Pi$ -SiGe S/D have higher strain in the fin channel, leading to further performance improvement without any additional cost or process complexity.

#### 2. DEVICE FABRICATION

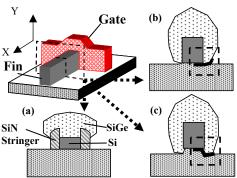

The process flow for the fabrication of p-channel FinFETs with  $e\Pi$ -SiGe S/D is detailed in Fig. 1. 8" silicon-on-insulator (SOI) substrates with 30 nm thick Si were used. After threshold voltage  $V_t$  adjust implant, 248 nm lithography with phase-shift mask, resist trimming, and reactive ion etching were used to define Si fins with fin widths  $W_{fin}$  down to 60 nm. SiO<sub>2</sub> gate dielectric (~3 nm) was then thermally grown, followed by poly-Si gate deposition, gate pre-doping, gate definition, and etch. S/D extension implantation was performed. In the spacer formation process, SiN stringers at the base of the fins were removed to enable epitaxial growth of SiGe on the fin sidewalls. If the SiN stringers were not removed, SiGe S/D can only grow on the top surface of the fin [Fig. 2(a)] [3] and severely limit strain effects which is undesirable.

An extended pre-epitaxy clean was performed for the device in which FinFETs with  $e\Pi$ -SiGe S/D will be formed. The extended HF clean formed a recess in the buried oxide prior to the epitaxy step, exposing a portion of the bottom surface of the fin. Selective epitaxial growth of Si<sub>0.75</sub>Ge<sub>0.25</sub> was then performed on all wafers. Fig. 2(b) shows the cross-sectional profile of a fin (without SiN stringer) with SiGe S/D grown on the fin sidewalls, forming a  $\Pi$ shaped SiGe S/D. Fig. 2(c) shows the  $e\Pi$ -SiGe S/D which extends into the buried oxide and encroaches under the Si fin (without SiN stringer) to give a more highly strained Si fin. S/D formation, oxide passivation, and metallization were performed to complete the devices. We shall compare the performances of FinFETs with  $\Pi$ -SiGe S/D [Fig. 2(b)] and  $e\Pi$ -SiGe S/D [Fig. 2(c)].

# 3. RESULTS AND DISCUSSION

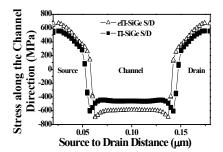

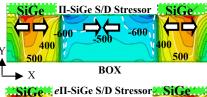

Fig. 3 shows the results of a 3D stress simulation for a FinFET having  $e\Pi$ -SiGe S/D stressors. The recess in the BOX is 6 nm. A 2D cross-sectional view was taken close to the fin sidewalls so that SiGe regions of the  $e\Pi$ -SiGe stressor appear on the top and bottom of the Si fin in the S/D regions. The Si fin in the S/D region is under tensile stress (indicated by arrows in Fig. 3). This tensile

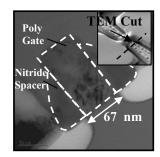

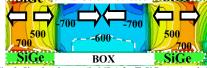

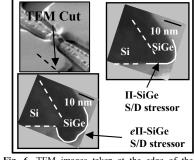

stress in the S/D is larger in the device with  $e\Pi$ -SiGe S/D (Fig. 3 & 4). Consequently, the channel stress is more compressive for the FinFET with  $e\Pi$ -SiGe S/D stressors, as portrayed in Fig. 4. A TEM image of the gate stack (Fig. 5) shows a gate length  $L_g$  of 67 nm. For the  $e\Pi$ -SiGe structure, the recess in the BOX is clearly seen. This recess allows the growth of SiGe below the base of the Si fin (Fig. 6, bottom). This is not observed for the  $\Pi$ -SiGe structure where the BOX is not recessed (Fig. 6, right). The additional SiGe growth enhances the channel strain contribution from the SiGe S/D stressors.

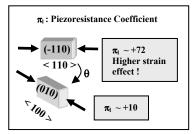

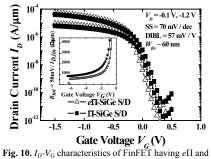

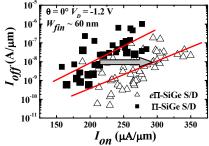

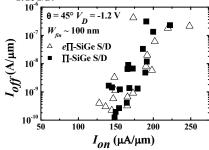

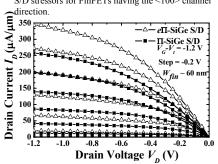

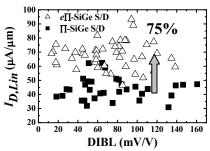

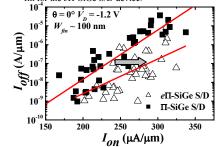

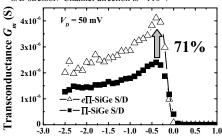

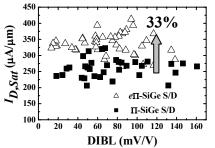

FinFETs with 2 orientations (Fig. 7) are examined:  $\theta = 0^{\circ}$  and 45°, having strong and weak piezoresistance coefficients, respectively. Fig. 8 plots the  $I_{off}$ - $I_{on}$  data for <100>-oriented ( $\theta$  = 45°) FinFETs with Π-SiGe and eΠ-SiGe S/D, showing little difference due to the negligible piezoresistance effect for that orientation. Fig. 9 reveals that if the channel orientation is <110>  $(\theta = 0^{\circ})$ , FinFETs with eII-SiGe S/D give a 21% larger  $I_{on}$  at an  $I_{off}$ of 100 nA/μm over FinFETs with Π-SiGe S/D. Devices in Fig. 8 & 9 have  $W_{fin} = 100$  nm. Fig. 10 shows the  $I_D$ - $V_G$  characteristics of two closely matched FinFETs having  $W_{fin} = 60$  nm, with similar series resistance, subthreshold swing and DIBL. Fig. 11 compares their  $I_D$ - $V_D$  characteristics, showing the significant  $I_{on}$  enhancement achieved/contributed by the  $e\Pi$ -SiGe S/D stressor over a  $\Pi$ -SiGe S/D. This enhancement is largely attributed to the increase in hole mobility as suggested by the transconductance  $G_m$  gain in Fig. 12. A significant 71% increase in the peak  $G_m$  value is observed. Fig. 13 shows the  $I_{off}$ - $I_{on}$  plots for FinFET with  $\Pi$ - and  $e\Pi$ - SiGe S/D stressors having  $W_{fin} = 60$  nm. When  $W_{fin}$  is reduced from 100 to 60 nm, a significantly larger enhancement in  $I_{on}$  (50%) can be observed due to a larger strain effect and also a larger  $I_{on}$ contribution by the sidewalls which benefits more from the  $e\Pi$ -SiGe S/D. Fig. 14 and 15 show the enhancement in both I<sub>D,Lin</sub> and  $I_{D,Sat}$  for FinFETs with eII-SiGe S/D over FinFETs with II-SiGe S/D. The enhancement in  $I_{D,Lin}$  (~75%) is about 2× higher than that of  $I_{Dsat}$  or  $I_{on}$  (33%) for a given DIBL.

### 4. CONCLUSION

P-channel FinFETs with  $e\Pi$ -SiGe S/D stressors were demonstrated for the first time, showing a further  $I_{on}$  enhancement of up to 33% over FinFETs already strained by  $\Pi$ -shaped SiGe S/D stressors.  $I_{on}$  enhancement increases with reduced fin width.  $e\Pi$ -SiGe S/D stressors offer the highest compressive strain for hole mobility enhancement among the SiGe S/D stressor configurations explored to-date. This is made possible by a recessed buried oxide prior to selective epi-growth of SiGe. The integration scheme for  $e\Pi$ -SiGe S/D is very attractive as no additional process complexity is introduced. The  $e\Pi$ -SiGe S/D is promising for performance enhancement in aggressively scaled FinFET devices.

Acknowledgment. This work was supported by the Nanoelectronics Research Program, Agency for Science, Technology, & Research, Singapore.

#### REFERENCES

[1] J. Kavalieros et.al., Symp. VLSI Tech. 2006, pp. 50-51.

- [2] T.-Y. Liow et al., Symp. VLSI Tech. 2006, pp. 68-69.

- [3] P. Verheyen et.al., Symp. VLSI Tech. 2005, pp. 194-195.

- Fin definition

- Gate Stack formation and Gate implant

- SDE implantation

- Spacer formation

- Removal of Spacer Stringer

- Pre-Epi HF Dip:

- П SiGe S/D stressor : 30 sec

- еП SiGe S/D stressor: 120sec

- Si<sub>0.75</sub>Ge<sub>0.25</sub>-Epi Growth

- S/D Implantation and Activation

- Metallization

Fig. 1. Process flow for the fabrication of FinFETs with eII SiGe S/D stressor formed by introducing a longer pre-epi HF clean.

Fig. 4. Simulated stress along the channel direction taken near the bottom of the fin.  $e\Pi$ -SiGe S/D stressor has a larger tensile stress near to the BOX at the S/D region which result in a higher compressive stress in the channel.

Fig. 7. Schematic showing the fin sidewall surface orientation and transport direction with the respective longitudinal piezoresistance coefficient.

Π-SiGe S/D stressors shows similar subthreshold swing and DIBL value. Inset shows that both devices have matched S/D resistance.

Fig. 13.  $I_{off}(V_G = 0.15 \text{ V})$  versus  $I_{on}(V_G = -1.05 \text{ V})_2$ showing larger enhancement [~50% at  $I_{off} = 1 \times 10^{-8}$ (A/µm)] for W<sub>fin</sub> of 60 nm over 100 nm.

Fig. 2. (a) SiGe S/D stressor from ref 3. This work realizes (b)  $\Pi$ -SiGe S/D stressor. (c)  $e\Pi$ -SiGe S/D stressor with SiGe growth below the BOX.

Fig. 5. TEM image of the gate profile taken along the S/D direction shows a gate length of sub 67nm. SEM image in the inset shows the FinFET having a raised SiGe S/D

**Fig. 8.**  $I_{off} (V_G = 0.15 \text{ V}) - I_{on} (V_G = -1.05 \text{ V})$  comparison showing not much difference between  $e\Pi$  and  $\Pi$ -SiGe S/D stressors for FinFETs having the <100> channel

Fig. 11.  $I_D$ - $V_D$  characteristics of both types of devices showing a higher drive current for FinFET having eII-SiGe S/D stressors.

Fig. 14.  $I_{D,Lin}$  obtained at  $V_G$ - $V_t$  = -1.2 V and  $V_D$  = -0.1 V 75% enhancement in linear drain current is observed for a given DIBL.

Fig. 3. Simulated stress (in MPa) for  $\Pi$ -SiGe (top) and  $e\Pi$ -SiGe S/D stressor (bottom) stressors. Contour interval is 100MPa.  $L_g = 40$  nm,  $W_{fin} = 20$  nm. Si at S/D and channel region is under tensile and compressive strain respectively.

Fig. 6. TEM images taken at the edge of the FinFET device near the S/D region. SiGe is observed to have grown below the bottom of the fin for the eII-SiGe S/D device.

**Fig. 9.**  $I_{off}(V_G = 0.15 \text{ V}) - I_{on}(V_G = -1.05 \text{ V})$  comparison shows an  $I_{on}$  enhancement of 21% at  $I_{off} = 1 \times 10^{-7} \text{ A}/\mu\text{m}$  for FinFET having eΠ-SiGe S/D stressor over Π-SiGe S/D stressor. Channel direction is <110>

**Gate Voltage**  $V_{G}(\mathbf{V})$ **Fig. 12.** FinFET with  $e\Pi$ -SiGe SD shows a 71% transconductance enhancement.

**Fig. 15.**  $I_{D,Sat}$  obtained at  $V_G - V_t = V_D = -1.2$  V. 33% enhancement in drive current can be observed at a fixed DIBL.