# Fully Analytical Modeling of Cu Interconnects Up to 110 GHz

Jun-De Jin<sup>1</sup>, Shawn S. H. Hsu<sup>1</sup>, Tzu-Jin Yeh<sup>2</sup>, Ming-Ta Yang<sup>2</sup>, and Sally Liu<sup>2</sup>

<sup>1</sup>Dept. of Electrical Engineering and Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan 300, R.O.C.

<sup>2</sup>Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan 300-77, R.O.C. Tel: 886-3-5731278; Fax: 886-3-5752120; E-mail: shhsu@ee.nthu.edu.tw

## 1. Introduction

The operation frequency of the integrated-circuits using advanced CMOS technology has been exceeded 100 GHz [1]. One important role is the copper (Cu) interconnects because the impact on circuit characteristics can no longer be neglected. However, the modeling and the characteristics of the Cu interconnects up to such a high frequency has not been reported.

Various interconnects modeling approaches has been reported [2]-[5]. An analytical approach has been used by considering only part of the high-frequency effects and is verified up to relative low frequencies [2]. In addition, semi-empirical models were employed for better agreement between the measured and modeled results [3]-[5]. In this study, a simple approach with multi-section *RLGC* elements, but fully physical-based and scalable, is proposed and verified up to 110 GHz. Additionally, the Cu interconnects with and without Si-substrate shielding are studied. Compared with the shielded cases, unshielded interconnect model needs to take into account the effects introduced by the lossy Si substrate.

### 2. Modeling of Interconnects

The Cu interconnects are fabricated using a standard 0.13-µm CMOS process which provides eight metal layers for a flexible interconnect design. The signal line is realized by metal eight (M8), with a width and a thickness of 2.5 µm ( $w_s$ ) and 3.3 µm ( $t_s$ ), respectively. The Si substrate shielding is realized by M1 with a thickness of 0.28 µm ( $t_g$ ). A silicon dioxide (SiO<sub>2</sub>) layer with a thickness of 6.3 µm ( $t_{ox}$ ) and an equivalent dielectric constant ( $\varepsilon_r$ ) of 4.04 is used between M8 and M1, while a thickness of 7.07 µm ( $t_{oxl}$ ) and an equivalent  $\varepsilon_r$  of 4.05 is employed between M8 and the Si substrate.

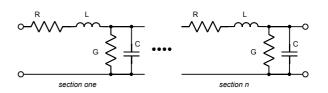

Modeling of the Cu interconnects is based on the distributed *RLGC* circuit model, due to the advantages of a simple yet physical-based circuit topology, as shown in Fig. 1. Each component in the model, as shown in the following, is calculated based on their physical characteristics. In addition, it was found that the interconnects with a length of 1000 µm can be modeled precisely by only 20 *RLGC* sections. The calculation of each component in the distributed interconnect model for both with (denoted as  $R_{W-5}$ ,  $L_{W-5}$ ,  $G_{W-5}$ , and  $C_{W-5}$ ) and without (denoted as  $R_{W0-5}$ ,  $L_{W0-5}$ ,  $G_{W0-5}$ , and  $C_{W0-5}$ ) substrate shielding are described as follows. *Cu Interconnects with Substrate Shielding*

In this case,  $R_{w-s}$  is the sum of DC resistance and the

Fig. 1 A typical distributed RLGC equivalent circuit with n sections for interconnects.

AC resistance originated from the skin effect in the finite metal width and thickness of both the signal and ground lines [2]. The proximity effect was not taken into account since the skin effect dominates the reduction in current loop area at high frequencies. On the other hand, the calculation of  $L_{w-s}$  considers both the skin and proximity effects, which can be described by a frequency-dependent internal inductance ( $L_{int}$ ) and a frequency-independent external inductance ( $L_{ext}$ ) [6]:

$$L_{\rm int} = \frac{\mu_0}{2\pi} \frac{3}{8} \tanh\left(\frac{2\pi\delta_s}{w_s + t_s}\right) \tag{1}$$

$$L_{ext} = (\mu_0 / 2\pi) (2 \ln[R_{12}] - \ln[r_1] - \ln[r_2])$$

(2)

where

$$\ln[R_{12}] = \ln\left[100\left(\frac{2t_{ox} + t_s + t_g}{2}\right)\right] + k_1$$

(3)

$$r_1 = 100 \times e^{-3/2} (w_s + t_s) \tag{4}$$

$$r_2 = 100 \times e^{-3/2} \left( w_g + t_g \right) \tag{5}$$

and where  $\delta_s$  is the skin depth of the signal line and  $w_g$  is the ground line width. The  $G_{w-s}$  and  $C_{w-s}$  can be easily estimated by a parallel plate structure. With a frequency-dependent conductive loss,  $G_{w-s}$  can be represented as:

$$G_{w-s} = \omega \varepsilon_r'' \varepsilon_0 w_s / t_{ox}$$

(6)

where  $\varepsilon_r$  is the imaginary part of the dielectric constant of SiO<sub>2</sub>. To calculate  $C_{w-s}$ , a geometry-dependent effective dielectric constant [2] and a fringing capacitance are both taken into account [7].

Cu Interconnects without Substrate Shielding

For the Cu interconnects without substrate shielding, the electromagnetic wave can penetrate into the lossy Si substrate, which is referred to as the substrate skin effect [8]. As a result, the series impedance ( $Z_{Si}$ ) of the interconnects can be calculated as:

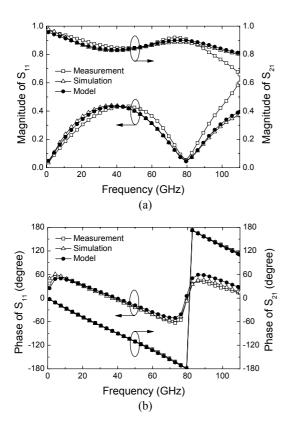

Fig. 2 (a) Magnitude and (b) phase of the measured, simulated, and modeled S-parameters of the Cu interconnect with substrate shielding. The length of the line is  $1000 \mu m$ , and *n* is 20.

$$Z_{Si} = \frac{1}{\sigma_s w_s t_{ss}} + j\omega \frac{\mu_0}{2\pi} \ln \left[ \frac{2t_{eq} + \delta_{Si} - j\delta_{Si}}{r_{eq}} \right]$$

(7)

where

$$t_{eq} = t_{ox1} + (t_{ss} - w_s)/4$$

(8)

$$r_{eq} = (t_{ss} - w_s)/4$$

(9)

$$t_{ss} = t_s \delta_s / (t_s + \delta_s) \tag{10}$$

and where  $\sigma_s$  is the conductivity of the signal line,  $\delta_{Si}$  is the skin depth of the Si substrate.

In this case,  $R_{wo-s}$  can be obtained from the real part of  $Z_{Si}$ , and  $L_{wo-s}$  is the imaginary part of  $Z_{Si}$  divided by  $\omega$ . As can be seen,  $R_{wo-s}$  is determined not only by the metal signal line but also by the Si substrate. In addition, as a function of  $\delta_{Si}$ ,  $L_{wo-s}$  presents a frequency-dependent characteristic. The  $G_{wo-s}$  and  $C_{wo-s}$  can be determined by a Si conductance and a Si capacitance first in a parallel connection, and then in series with a SiO<sub>2</sub> capacitance. These three are obtained based on the physical structure, and considered the geometry-dependent effective dielectric constants in a parallel plate structure.

# 3. Measured Results

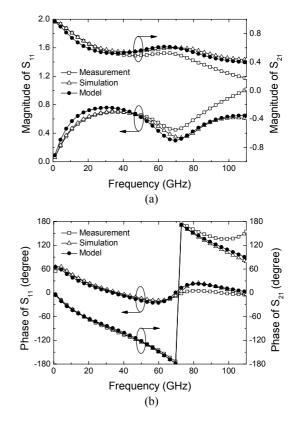

The Cu interconnects were measured on-wafer from 1 to 110 GHz. Fig. 2 and Fig. 3 show the measured and modeled results for the interconnects with and without the sub-

Fig. 3 (a) Magnitude and (b) phase of the measured, simulated, and modeled S-parameters of the Cu interconnect without substrate shielding.

strate shielding, respectively. The simulated results from SONNET are also shown for comparison. For both types of Cu interconnects, as can be seen, the modeled S-parameters are in excellent agreement with the simulated and measured results in a wide frequency range.

### 4. Conclusions

A fully analytical approach with scalability for the Cu interconnects in a standard CMOS process was developed and verified up to 110 GHz. By carefully considering the frequency-dependent effects of each *RLGC* component, excellent agreement was observed between measured, modeled, and simulated S-parameters. The proposed simple approach is not only provided the physical insight but also showed excellent modeling accuracy for both shielded- and unshielded-type interconnects over a wide frequency range without any optimization procedure.

### References

- [1] P.-C. Huang, and et al., ISSCC. (2005).

- [2] Y. Eo, and et al., IEEE CHMT. (1993).

- [3] D. Goren, and et al., DAC. (2003).

- [4] S.-P. Sim, and et al., IEEE TED. (2003).

- [5] J.-K. Wee, and et al., IEEE MTT. (1998).

- [6] F. W. Grover, (1946).

- [7] C. P. Yuan, and et al., IEEE EDL. (1982).

- [8] H. Ymeri, and et al., PLA. (2002).