# Improvement of Adhesion at the Interface between Low-k Spin-on Dielectric and underlying SiCO Barrier by Plasma Treatments

Y. Takigawa, S. Nakao, M. Shiohara, N. Oda, and S. Ogawa

Semiconductor Leading Edge Technologies, Inc.,

16-1 Onogawa, Tsukuba-shi, Ibaraki, 305-8569, Japan Tel: +81-29-849-1484, Fax.: +81-29-849-1452, E-mail: takigawa.yukio@selete.co.jp

## 1. Introduction

As CMOS devices are scaled-down, chip-level performance is limited by interconnect parameters, such as wiring capacitance and resistance [1-2]. Using porous low-k dielectric as inter-metal dielectric (IMD) and inter-level dielectric (ILD) materials, we can obtain reduced signal propagation delay time and low power dissipation matching to the state-of-the-art CMOS generation. In hp45nm generation, effective dielectric constant keff of 2.7-3.0 is necessary and k<2.4 is indispensable for realizing the appropriate performance [3]. Spin-on-dielectric (SOD) films are popularly examined as porous low-k material [4] as well as CVD films. In low-k materials, there are some issues such as peeling in Cu CMP process [5] and wire-bonding failure caused by the fragility of the material and low adhesion strength. There are some papers concerning such problems mentioning that some key parameters should be controlled, i.e. 1) preparing materials with higher elastic modulus, and 2) introducing plasma treatment to obtain higher adhesion strength to the underlying materials [5]. However, the key parameters were treated individually and it has not been reported the mechanism of enhancing adhesion strength using plasma treatment. In this paper, combination of material properties and adhesion strength are investigated. And the mechanism for obtaining higher adhesion strength is also investigated by analytical study. The appropriate pre-treatment condition for fragile material is also derived.

## 2. Experimental

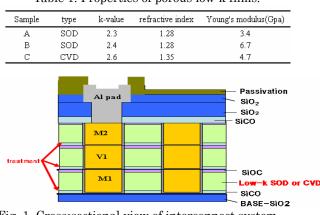

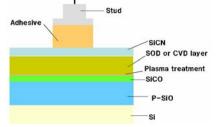

Two types of porous MSQ as SOD materials are investigated. A mature porous SiOC deposited by plasma-enhanced CVD (PE-SiOCH: k=2.6) is prepared as a reference. The film properties are listed in Table 1. The SOD materials were prepared by spin coating on underlying SiCO film, followed by curing or annealing at around 400 deg. C. The Young's modulus for sample B is higher than sample A, which is tradeoff against dielectric constant. 2-layers of Cu interconnect combined with porous low-k IMD and ILD were prepared, as shown in Fig. 1. We tried three kinds of plasma treatment to the surface of the underlying etching stopper SiCO layer, i.e., ammonia, helium, and argon plasma ambiances. Adhesion strength between low-k SOD and the etching stopper layer of blanket films were evaluated by stud-pull testing, illustrated in Fig. 2. Peeling by CMP process was checked using an optical microscope. Chemical properties of the surface of SiCO were evaluated using Fourier-transformed Infrared (FT-IR) with attenuated total reflection (ATR) method. Electrical properties of Cu/low-k interconnect with 200 nm pitch are also evaluated over the whole wafer with 300 mm in diameter.

## 3. Results and Discussion

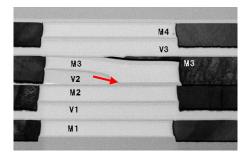

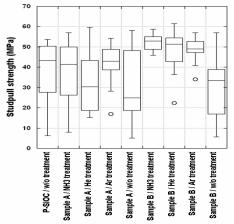

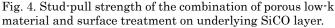

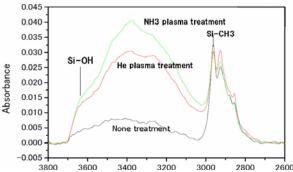

Without any plasma treatment, multilevel interconnect structure using samples A and B showed some peeling occurred at Cu CMP process, as shown in Fig. 3. Adapting any plasma treatment, we confirmed that there is no peeling at Cu CMP process. Figure 4 shows the stud-pull strength in comparison with each plasma treatment between low-k SOD and underlying SiCO. In sample B, surface treatment is more effective to enhance the adhesion strength than sample A. This result might be caused by the combination effect of higher elastic modulus and improved interface adhesion strength. In case of sample A, the effect of plasma treatment is more susceptible. The argon plasma treatment shows the highest strength, but the thickness of SiCO is decreased. Therefore we selected ammonia plasma and helium plasma for the treatment of SiCO surface. The FT-IR spectra after each treatment condition of SiCO is shown in Fig. 5. The methyl (-CH3) group is decreased and the hydroxyl (-OH) group is increased by plasma treatments. The quantity of the hydroxyl group of ammonia plasma is more increasing and that of methyl group is more decreasing than helium plasma. The increase of Si-OH absorption is considered to be caused by natural coating under atmospheric conditions before FT-IR evaluation, which suggests that the SiCO surface becomes more reactive with any materials. From these results, the absence of methyl group plays an important role to enhance the adhesion strength, which also shows more reactive with SOD materials. This is probably the reason why the stud-pull strength after

ammonia plasma is more than helium plasma.

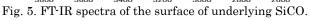

Wiring capacitance for each condition is shown in Fig. 6. There are no effect to the increasing in capacitance. The capacitance for each low-k SOD decreased by more than 5 % compared with PE-SiOCH, which is acceptable advantage from the previous generation. In this experimental set, it was confirmed that ammonia plasma treatment is the best solution to avoid delamination by CMP and to obtain good leakage characteristics.

#### 4. Conclusion

We found that the ammonia plasma treatment for underlying SiCO is appropriate for improving the adhesion between low-k SOD and SiCO. The absence of methyl group enhances the reactivity between underlying SiCO and low-k SOD. It was confirmed that there are no affect to electrical characteristics by ammonia treatment.

## Acknowledgement

We thank Dr. S. Saito for useful discussions.

#### References

[1] N. Oda et al., IEDM 41.2 (2005) 1045.

[2] N. Oda et al., IEICE Trans. Electron., E90-C, 4 (2007) 848.[3] Inter. Semiconductor Roadmap for Semiconductors 2006 Edition.

[4] T. Ono et al., Jpn. J. Appl. Phys., 45, 10A (2006) 8873.

[5] S. Kondo et al., Proc. Inter. Interconnect Tech. Conf., 5.2 (2003) 86.

Table 1. Properties of porous low-k films.

Fig. 2. Schematic diagram of stud-pull testing.

Fig. 3. Cross-sectional TEM view of 4-level interconnect. V2 layer is peeling by CMP.

Fig. 6. Wiring capacitance for each low-k and treatment.