# D-5-1 (Invited)

## **RF CMOS Circuits–Overview and Perspective**

Tsuneo Tsukahara

The Univ. of Aizu, Dept. of Computer Hardware Tsuruga, Ikki-machi, Aizu-Wakamatsu City, Fukushima 965-8580, Japan Phone: +81-242-37-2518, E-mail: tsuka@u-aizu.ac.jp

## 1. Introduction

Wireless communications by cellular telephony has first-generation advanced through analog. second-generation digital, and third-generation wideband systems, and the direction of research at present is toward high-speed transmission and high-speed mobility in order to realize fourth-generation systems. Recently, there has been significant activity in the development of short-range wireless communications systems such as Bluetooth in the 2.4-GHz band and wireless LAN in the 2.4- and 5-GHz bands. We can therefore see the evolution of a foundation for ubiquitous communications. Regarding semiconductor devices, silicon devices, among other semiconductors, are becoming viable in the main wireless bands from 800 MHz to 5 GHz. CMOS devices are found in a comparable range as CMOS transistors have attained high-frequency capability through fine-processing technology.

In recent years, research on CMOS radio frequency (RF) transceivers and circuits has been very active [1–4]. Furthermore, several transceiver architectures such as direct-conversion, wideband intermediate frequency (IF), and low-IF configurations have been exploited for single-chip integration [1–3]. The alleviation of RF specs in Bluetooth has prompted the development of single-chip RF transceivers.

Section 2 describes the architectures of single-chip transceivers. Section 3 presents an example of a low-voltage CMOS RF receiver. Section 4 discusses the basics of sampling techniques for frequency conversion in RF applications.

### 2. Trends in Single-Chip Transceiver Architectures

Traditionally, superheterodyne receivers (SHRs) are used in wireless transceivers. For channel selection, SHRs require external IF filters with fixed center and cutoff frequencies, depending on the system. The IF filters, being bulky, add to the cost of the transceivers. The demand for smaller and cheaper transceivers has stimulated the exploitation of new architectures suitable for single-chip radios. Furthermore, the demand for multi-standard transceivers that use flexible filtering for channel selection has increased recently, implying that SHRs are not suitable for this application.

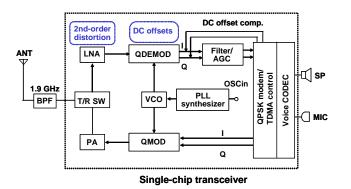

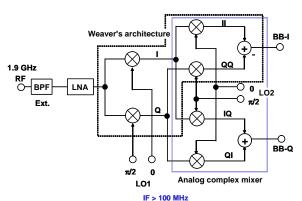

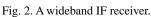

Most transceivers suitable for single-chip integration have direct-conversion, wideband IF, or low-IF configurations. In all of these configurations, channel selection can be accomplished with on-chip active filters. A generic direct-conversion transceiver is shown in Fig. 1. This is also termed as the zero-IF architecture, and as the name which implies, that an image response does not exist, while DC offset and second-order distortion become new problems [1]. Therefore, DC offset cancellation and high-linearity receiver front-end circuits are indispensable. Potentially, direct-conversion configuration the is applicable to any wireless system. Figure 2 shows the block diagram of a wide-band IF receiver [2], that has a high IF ranging from 100 to 200 MHz. The image signals are rejected using an external RF bandpass filter and image-rejection mixers based on Weaver's architecture [5]. However, because this combination can result in high image-rejection, wideband IF receivers may also be applied to any wireless system. Figure 3 shows a block diagram of a low-IF receiver [3]. Image rejection is performed exclusively by image-rejection mixers because image signals are in-band signals. The principle of the image-rejection mixer is the same as that of the wideband IF receiver. However, image signal cancellation can be accomplished in the digital domain because of the low IF. The low-IF configuration is applicable only when the image-rejection specifications are set to low values, for example, in Bluetooth or GSM with IF = 100 kHz [3], where the adjacent signal is the image signal. Low power consumption is the key to expanding the use of CMOS single-chip transceivers because more active circuits are necessary for IF and baseband analog signal-processing in the complex signal domain.

### 3. Example of a 1-V Low-IF Receiver Using CMOS/SOI

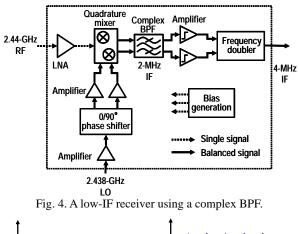

By combining low-voltage circuit techniques and CMOS/SOI device technologies, we developed a 1-V, 2.4-GHz operation receiver using a complex bandpass filter (BPF) [6]. Figure 4 shows a block diagram of the receiver. The channel-select complex BPF is a fifth-order Butterworth filter with a 1-MHz bandwidth. The complex BPF characteristic is realized using a frequency shift of 2 MHz of two real low-pass filters with a 500-kHz bandwidth using in-phase and quadrature-phase signals, as shown in Reference 7. The receiver dissipates 23 mW at a 1-V supply and shows a -76.5 dBm sensitivity at a BER of 0.1%.

#### 4. Sampling Techniques for Frequency Conversion

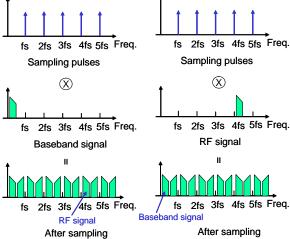

Sampling techniques can now be applied to frequency conversion between RF/IF and baseband signals [8] because transistor switching speeds have been significantly increased by using deep sub-micron devices. Sampling a baseband signal produces multiple frequency spectra around  $n_s$ , as shown in the left of Fig. 5, where n is an integer and  $f_s$  is the sampling frequency. In this case, the sampling performs a kind of frequency up-conversion, which can be used in a transmitter. On the other hand, sampling RF/IF signals provides a baseband signal around DC even if the sampling frequency is less than the RF/IF frequencies, as shown in the right of Fig. 5. This process is called under-sampling or sub-sampling and is suitable for a receiver. Therefore, sampling or discrete-time signal processing is a strong candidate for RF signal processors in the near future.

#### 5. Conclusions

The current trends in CMOS RF transceiver architectures are first discussed. Subsequently, a low-voltage-operation low-IF receiver using CMOS/SOI is described. Finally, the potentials of sampling techniques for RF signal processing are reviewed.

#### References

[1] A. A. Abidi, "Direct-Conversion Radio Transceiver for Digital Communications," *IEEE J. Solid-State Circuits*, vol. 30, no. 12, pp. 1399-1410, Dec., 1995.

[2] J. C. Rudell, J.-J. Ou, T. B. Cho, G. Chien, F. Brianti, J. A. Weldon, and P. Gray, "A 1.9-GHz Wide-Band IF Double Conversion CMOS Receiver for Cordless Telephone Applications," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2071-2088, Dec, 1997.

[3] M. Steyaert, J. Janssens, B. De Muer, M. Borremans, and N. Itoh, "A 2V CMOS Cellular Transceiver Front-End," 2000 IEEE Int'l Solid-State Circuits Conference, 8.3, pp. 142-143, Feb., 2000.

[4] D. Su, M. Zargari, P. Yue, S. Rabii, D. Weber, B. Kaczynski, S. Mehta, K. Singh, S. Mendis, and B. Wooley, "A 5-GHz CMOS Transceiver for IEEE 802.11a Wireless LAN," 2002 IEEE Int'l Solid-State Circuits Conference, 5.4, pp. 92-93, Feb., 2002.

[5] D. K. Weaver, "A Third Method of Generation and Detection of Single-Sideband Signals," *Proceedings of IRE*, vol. 44, pp.1703-1705, Dec., 1956.

[6] M. Ugajin and T. Tsukahara, "A 1-V 2.4-GHz FSK Receiver with a Complex BPF and a Frequency Doubler in CMOS/SOI," *IEEE Custom Integrated Circuits Conference (CICC)*, pp. 151-154, 2003.

[7] P. Andreani, S. Mattisson, and B. Essik, "A CMOS gmC Polypahse Filter with High Image Band Rejection," 26<sup>th</sup> European Solid-State Circuits Conference, pp. 244-247, Sept. 2000.

[8] K. Muhammad, D. Leipold, and B. Staszewski, Y.-C. Ho, C. M. Hung, K. Maggio, C. Fernando, T. Jung, J. Wallberg, J.-S. Koh, S. John, I. Deng, O. Moreira, R. Staszewski, R. Katz, and O. Friedman, "A Discrete-Time Bluetooth Receiver in a 0.13 um Digital CMOS Process," 2004 IEEE Int'l Solid-State Circuits Conference, 15.1, pp. 268-269, Feb., 2004.

Fig. 1. A direct-conversion transceiver.

Total NF = 8.2 dB, Image rejection = 32.2 dB

Fig. 3. A low-IF receiver.

Fig. 5. Sampling techniques for frequency conversion.