# An Optimized Silicidation Technique for Source and Drain of FINFET

Kiyoshi Okuyama, Atsushi Sugimura, and Hideo Sunami

Research Center for Nanodevice and Systems, Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima 739-8527, Japan Phone: +81-82-424-6265, Fax: +81-82-424-3499, E-mail: okuyama@sxsys.hiroshima-u.ac.jp

# 1. Introduction

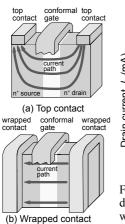

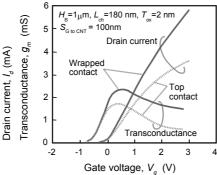

Three-dimensional (3-D) devices e.g. FinFET [1, 2], have been extensively developed for further scaled devices. Suppression of short-channel effects can be realized on these device structures, but, drive-current decrease by parasitic resistance is caused. Figure 1 shows simulated  $I_D$ - $V_G$ characteristics of devices with different two contact structures [3]. This result shows that parasitic resistance of source and drain, S/D causes driving-current decrease for top-contact structure device. To overcome this problem, it is needed to form low-resistive S/D. From this viewpoint, a Ni-silicidation technique for vertical S/D is investigated.

### 2. Experimental

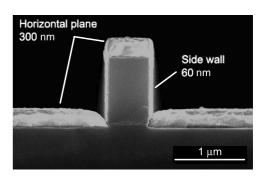

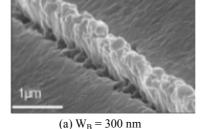

For the case of 3-D structure devices, there are some issues on silicidation process. Figure 2 shows a cross-sectional view of Ni film deposited by sputtering method at 200 °C. Directionality of the sputtering causes deposition-rate difference between horizontal and vertical surfaces. As a result, there is surplus metal on horizontal surfaces. After silicidation annealing in deposition chamber at 450 °C in situ, deformation of Si patterns is observed as shown in Fig. 3. It is noted that the degree of these deformation depends on its pattern width [4]. These results show that each amount of Si and Ni influences silicide formation. To avoid these phenomena, deposition of appropriate amount of Ni and sensitive control of annealing conditions are needed.

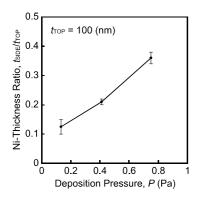

Pressure dependence of deposited Ni thickness on vertical sidewall is shown in Fig. 4. Its thickness uniformity is improved as the deposition pressure becomes larger. The thickness ratio,  $t_{side/top}$  achieves 0.38 at 0.75 Pa when the thickness on horizontal surface is 100 nm. This condition is adopted in this work. When thicker Ni film is needed on the sidewall, a chemical-vapor deposition, CVD has much better potential to obtain conformal deposition [5]. To exclude the influence of the temperature change when a sample is heating, silicidation annealing is carried out during deposition.

# 3. Results and discussion

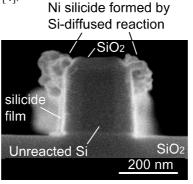

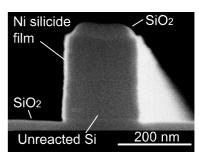

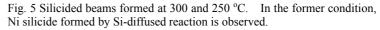

Figure 5(a) shows an SEM image of a Si beam silicided by in-situ annealing at 300 °C. 55-nm-thick Ni-silicide film is uniformly formed on the sidewall, but silicide formed by Si-diffused reaction is observed at the edge of patterns. This result shows that the shape of Ni silicide changes sensitively in each part of vertical structure. For the case of 250 °C annealing shown in Fig. 5(b), deformation caused by Si diffution is suppressed and 30-nm-thick silicide film is formed. XRD spectra for these samples are shown in Fig. 6.  $Ni_3Si_2$  phase is observed as a dominant peak at 300 °C-annealing case, but deformation of Si beam is occurred in this case. For 250 °C-annealing case, Ni richer film, Ni<sub>2</sub>Si phase is detected, and Si-beam deformation caused by Si-diffused reaction is not observed. After annealing at 250 °C and unreacted Ni removal by SPM, NiSi film is obtained by rapid thermal anneling at 450 or 500 °C avoiding Si-beam deformation.

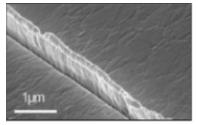

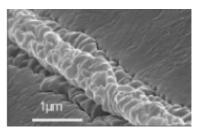

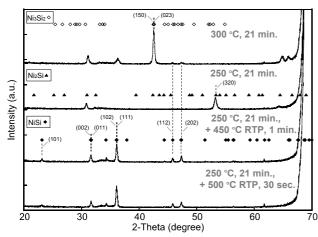

Figure 7 shows an SEM image of a Si beam silicided by two-step annealing process. 60-nm-thick NiSi film is uniformly formed on the sidewall without abnormal deformation of Si-beams.

#### 4. Summary

A Ni-silicidation technique of source and drain for FIN-FET has been discussed. For devices with 3-D structure, it is important to provide appropriate amount of Ni and to control annealing conditions for avoiding abnormal deformation of Si beams. In this work, surplus Ni deposition on the horizontal surface is decreased by deposition-pressure control. In addition, a silicidation annealing carried out during deposition is adopted to exclude the influence of the temperature change when a sample is heating.

Si-diffused reaction causes deformation of Si-patterns in cases of annealing at 300 °C or higher. A two-step annealing process prevents this phenomenon and NiSi film is uniformly formed on vertical walls without abnormal deformation.

#### Acknowledgements

This work has been supported in part by a Grant-in-Aid for the 21st Century COE program "Nanoelectronics for Tera-bit Information Processing" from the Ministry of Education, Science, Sports and Culture of Japan.

#### References

- Y-K. Cho, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Andersen, T-J. King, J. Bokor, and C. Hu, IEDM Tech. Dig., pp. 421-424, 2001.

- [2] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, Symposium on VLSI Technology Digest of Technical Paper, 2003.

- [3] DESSIS, ISE TCAD, release 9.5, Synopsys Co., Ltd

- [4] S. Matsumura, A. Sugimura, K. Okuyama, and H. Sunami, Advanced Metallization Conference 2006: 16th Asian Session Sept. 25-27, 2006.

- [5] Y. Ohshita, M. Ishikawa, T. Kada, H. Machida, and A. Ogura, Jpn. J. Appl. Phys. Vol. 44, L315 (2005).

Fig. 1 Simulated  $I_{\rm D}$ - $V_{\rm G}$  characteristics of devices with usual top contact, (a) and wrapped contact, (b).

Fig. 2 An SEM image of deposited Ni film on vertical Si wall by sputtering method.

# (a) $W_B = 150 \text{ nm}$

Fig. 3 Bird's eye views of Si beams silicided in deposition chamber at 450 °C. The degree of these undesirable deformations depends on its pattern width [4].

Fig. 4 Pressure dependence of Ni thickness deposited on the sidewall when the thickness on horizontal surface is 100 nm.

(a)300 °C

(a)  $W_B = 500 \text{ nm}$

(b) 250 °C

Fig. 6 XRD spectra of silicided samples annealing at 300, 250 °C and two-step annealing.

Fig. 7 A cross-sectional view of Ni-silicided beam formed by two-step annealing process.