G-5-1

# A 7.6-ps Pulse Generator Using 0.13-µm InP-based HEMTs for Ultra Wide-Band Impulse Radio Systems

Yasuhiro Nakasha<sup>1</sup>, Yoichi Kawano<sup>1</sup>, Toshihide Suzuki<sup>1</sup>, Toshihiro Ohki<sup>2</sup>, Tsuyoshi Takahashi<sup>1</sup>, Kozo Makiyama<sup>1</sup>, Tatsuya Hirose<sup>2</sup>, and Naoki Hara<sup>1</sup>

<sup>1</sup>FUJITSU LIMITED <sup>2</sup>FUJITSU LABORATORIES LTD. <sup>1,2</sup>10-1 Morinosato-Wakamiya, Atsugi 243-0197, Japan Phone: +81-46-250-8244 E-mail: nakasha-y@jp.fujitsu.com

#### 1. Introduction

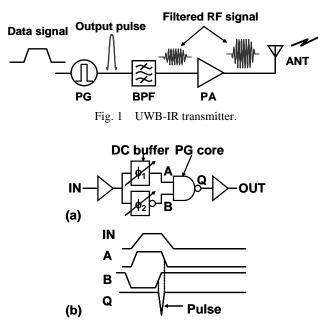

In this paper, we report a pulse generator (PG) having the shortest pulse duration ever reported using semiconductor transistor technology. Pulse generators are useful for various systems such as multi-gigabit communication, high-resolution radar, and ultra high-speed signal capturing. As for wireless systems, in particular, ultra wide-band impulse radio (UWB-IR) [1-4], a PG having pulses with sub-10-ps duration is very attractive since it covers a wide frequency spectrum from DC to millimeter wave (e.g., 100 GHz). As shown in Fig. 1, a UWB-IR transmitter has a very simple configuration, consisting of a PG, a bandpass filter (BPF), and an amplifier (PA). No local oscillators or mixers are needed. The transmitter generates pulses and then filters a wide frequency spectrum of the pulses to match the spectrum mask. Therefore, if the UWB-IR system has an ultra-short pulse generator, a broadband radio system operating in a millimeter wave band is realized with very simple RF blocks. We have already demonstrated an RF chipset for a 24-29 GHz UWB-IR radar system using a 13.5-ps PG [4] and already developed a 9-ps PG for up to 75-GHz UWB-IR systems [5]. This paper presents a PG with much shorter pulses that was developed to realize UWB-IR systems operating in much higher millimeter wave bands.

## 2. Circuit Design

As shown in Fig. 2 (a), the PG we designed has a very simple digital-based architecture, which is the same as one previously reported [5]. It consists of input and output buffers, delay control buffers (DC buffers), and a PG core. By adjusting delay times of the DC buffers, an overlap time between two signals A and B is created at the inputs of the PG core, as shown in the time chart of Fig. 2 (b). The PG core works as a logical NAND circuit and generates a pulse whose width is nearly equal to the overlap time.

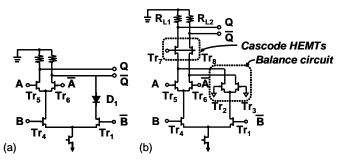

In order to obtain shorter pulses, enhancing the response speed of the PG core, or the NAND circuit is essential. Schematic diagrams of the conventional PG core and the one developed for this work are shown in Fig. 3. In the previous work [5], we replaced a diode for level shifting,

$D_1$  with a balance circuit to decrease Miller capacitance of  $Tr_1$  in the conventional circuit and to improve the switching time of the differential pair,  $Tr_1$  and  $Tr_4$ . In addition, in this work, we deployed cascode transistors,  $Tr_7$  and  $Tr_8$ , below load resistors,  $R_{L1}$  and  $R_{L2}$ , as shown in Fig. 3 (b). This circuit configuration reduces Miller capacitances of  $Tr_5$  and  $Tr_6$  and boosts switching performance of the differential pair,  $Tr_5$  and  $Tr_6$ . The approach in this work reduces rising time of the pulses, while the one in the previous work shortens falling time. A SPICE-based simulation showed that the pulse width of the developed PG is 20% shorter than that of the previous PG and 45% shorter than that of the conventional one.

#### 3. IC Fabrication

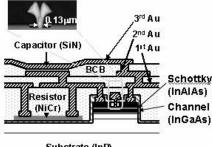

A schematic cross-section of our InP-based HEMT is illustrated in Fig.4. The Y-shaped gate ensures that more than 1000 transistors can be integrated uniformly [6]. The gate opening is formed by electron-beam lithography and the gate metal Ti/Pt/Au is evaporated. Typical gate length is 0.13  $\mu$ m. Triple-layer Au-plated interconnections and low-k benzocyclobutene (BCB) dielectric films are employed. Metal-insulator-metal (MIM) capacitors and NiCr thin-film resistors are also formed on the InP substrate. Thinning a Schottky barrier layer enhances device performance effectively [7] and the maximum transconductance  $g_m$  of 1.5 S/mm and the cutoff frequency  $f_T$  of 220 GHz are achieved.

#### 4. Circuit Performance

A micrograph of the PG chip is shown in Fig. 5. The chip measures  $2.2 \times 1.7$  mm. A data stream is input from the top, while the differential pulses corresponding to the data stream are output from the bottom. The chip contains 184 HEMTs.

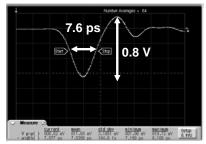

Fig. 6 shows an output pulse waveform observed using an oscilloscope with a 70-GHz sampling head. An ultra-sharp pulse was obtained. The full width at half maximum (FWHM) was as small as 7.6 ps, which is 1.4 ps higher than that of our previous work. The amplitude of the pulse was 0.8  $V_{pp}$ . To the best of our knowledge, this result, which includes the degradation of cable loss and the lack of bandwidth of the sampling head, is a record for pulse generators using any semiconductor transistors. The chip consumes 0.79 W.

# 5. Summary

Using a 0.13-µm-gate-length InP-based HEMT technology, we developed a simple PG circuit with a logical NAND-based core. The core has cascode transistors and a balance circuit, minimizing the Miller effect and maximizing the switching performance. The PG created an extremely short pulse whose FWHM was a record and only 7.6 ps. The performance of the PG makes it possible to realize various UWB-IR systems operating at over 90 GHz.

#### Acknowledgments

We would like to thank N. Kajihara, K. Joshin, and E. Yano for their encouragement.

# This work was supported in part by the Ministry of Internal Affairs and Communications.

Fig. 2 Block diagram of PG (a) and time chart (b).

Fig. 3 Conventional (a) and developed (b) PG core circuits.

## References

- Chia-Hsiang Yang, Kuan-Hung Chen, and Tzi-Dar Chiueh, *Tech. Dig. ISSCC 2005*, pp. 442, 2005

- [2] H. Ogawa, K. Hamaguchi, Y. Yamamoto, T. Hirose, T. Kobayashi, and R. Kohno, *Proc. of IEEE Joint UWBST and IWUWBS 2004*, pp. 351, 2004.

- [3] R. J. Fontana, IEEE *Trans. Micro. Theory Tech.*, Vol. 52, No. 9, pp.2087, 2004

- [4] Y. Kawano, Y. Nakasha, K. Yokoo, S. Masuda, T. Takahashi, T. Hirose, Y. Oishi, and K. Hamaguchi, *Proc. of IEEE MTT-s IMS 2006*, pp. 316, 2006

- [5] Y. Kawano, Y. Nakasha, T. Suzuki, T. Ohki, T. Takahashi, K. Makiyama, T. Hirose, and K. Joshin, *Proc. of the 36<sup>th</sup> EuMC*, pp. 1821, 2006.

- [6] N. Hara, K. Makiyama, T. Takahashi, K. Sawada, T. Arai, T. Ohki, M. Nihei, T. Suzuki, Y. Nakasha, and M. Nishi, *IEEE Trans. Semiconductor Manufacturing*, Vol. 16, No. 3, pp. 370, 2003.

- [7] T. Takahashi, M. Sato, K. Makiyama, T. Hirose, and N. Hara, *IEEE IPRM Dig.*, 2007

Substrate (InP)

Fig. 4 Cross-section of InP-based HEMT.

Fig. 5 Chip die of InP-based PG (2.2 x 1.7 mm).

Fig. 6 Output pulse from InP-based PG.