# Crystalline and electrical properties of mictamict TiSiN gate MOS capacitors

Kouhei Furumai<sup>1</sup>, Hiroki Kondo<sup>1†</sup>, Mitsuo Sakashita<sup>1</sup>, Akira Sakai<sup>1\*</sup>, Masaki Ogawa<sup>2</sup>, and Shigeaki Zaima<sup>1</sup>

<sup>1</sup> Graduate School of Engineering, Nagoya University, Furo-cho, Chikusa-ku, Nagoya 464-8603, Japan Phone: +81-52-789-3819 †E-mail: hkondo@alice.xtal.nagoya-u.ac.jp

<sup>2</sup> Nagoya University, Ecotopia Science Institute,

\* Present address : Graduate School of Engineering Science, Osaka University, Toyonaka, Osaka 560-8531, Japan

## 1. Introduction

For ultra-large scale integrated circuit (ULSI) technology node of half-pitch (hp) 32 nm and beyond, fluctuation of threshold voltages is required to be less than 10 mV [1]. However, it is well known that workfunction (WF) values of gate metals such as W, Mo, and so forth vary more than 1 eV depending on crystalline plane directions [2]. Additionally, since the fluctuation of crystalline phases in a fully-silicided (FUSI) gate was recently reported, it would induce the WF fluctuation [3]. Therefore, as long as commonly used polycrystalline metals, such as metal nitrides, alloys, silicides, germanides, are applied as gate electrodes, it would be extremely difficult to suspend the WF fluctuation to less than 10 meV. Amorphous alloys are expected to be a crystallographically-uniform material, but most of amorphous alloys easily crystallize during high temperature annealing in ULSI processes. In this study, we focus attention on a "mictamict" transition metal (TM)-silicon (Si)-Nitrogen (N) gates. "Mictamict" is a comprehensive including both entirely-amorphous term and near-amorphous states [4]. Sputtered amorphous TM-Si-N films may become near-amorphous, in which amorphous films and nanocrystallites are mixed, by post deposition annealing (PDA) treatments. However, if nanocrystatllites are sufficiently small and dense compared to the gate size, the mictamict gate can be regarded as an uniform gate material. In addition, TM-Si-N films have been studied as barrier metals in Cu interconnects, and can be formed by reactive co-sputtering systems conventionally used in the ULSI processes [5]. In this study, we formed Ti-Si-N gate metal-oxide-semiconductor (MOS) capacitors and investigated their crystalline and electric properties, in order to clarify its availability as a gate metal.

## 2. Experimental

MOS capacitors which have Ti-Si-N gate electrodes with various N compositions were fabricated. A p-type Si (100) wafer was used as the substrate. After diluted-HF treatment, gate SiO<sub>2</sub> films (10 nm) were grown by thermal oxidation. Ti-Si-N films were deposited on the SiO<sub>2</sub>/Si substrates by reactive sputtering using a Ti<sub>5</sub>Si<sub>3</sub> target in a N<sub>2</sub>/Ar gas mixture gas at room temperature. The N<sub>2</sub>/Ar mixture ratio was changed from 0 to 40%. Thicknesses of the deposited films were about 100 nm. Ti-Si-N/SiO<sub>2</sub>/Si samples were then subjected to rapid thermal annealing (RTA) treatments in an N<sub>2</sub> ambient at 500-1100°C for 30 s. Finally, after deposition of aluminum back gates, the MOS capacitors were annealed in a  $H_2$  ambient at 450°C for 30 min.

## 3. Results and Discussion

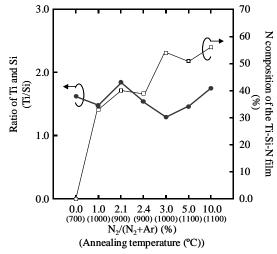

Figure 1 shows elemental composition ratio Ti/Si and N composition of the Ti-Si-N films obtained by Rutherford backscattering (RBS) measurements. Since the Ti<sub>5</sub>Si<sub>3</sub> target was used in this study, the ratio of Ti and Si was almost 1.66 regardless of the deposition and annealing conditions. However, the N composition of Ti-Si-N films drastically changed at a N<sub>2</sub> concentration of the deposition ambient N<sub>2</sub>/N<sub>2</sub>+Ar of 3%. Above a N<sub>2</sub> concentration of 3%, the N composition of films was almost constant to be about 53%, which indicates that all Ti and Si atoms deposited in the form of TiN and Si<sub>3</sub>N<sub>4</sub>, respectively.

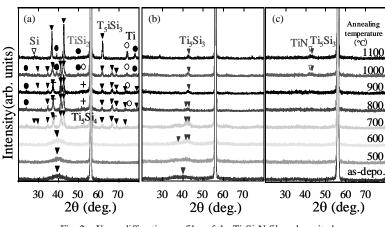

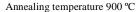

Figure 2 shows the X-ray diffraction profiles of Ti-Si-N films deposited at a (a) 1.0%, (b) 2.4%, (c) 5.0% N<sub>2</sub> ambient, respectively. While many sharp peaks were found after the RTA above 700°C in the case of the Ti-Si-N films sputtered in the 1.0% N<sub>2</sub> ambient, only a few and broad peaks were slightly detected for the case of the N<sub>2</sub> ambient larger than 2.4%. Diffraction peaks were hardly found for the Ti-Si-N film deposited in the 5.0% N<sub>2</sub> ambient, as shown in Fig. 2(c). These results reveal that an increase in the N content results in a suppression of the crystallization of Ti-Si-N films during RTA. Figures 3(a) and 3(b) show cross-sectional TEM images of the Ti-Si-N gate electrodes, in which the Ti-Si-N films were sputtered in a 2.4% and 5.0% N<sub>2</sub> ambient, respectively. The Ti-Si-N film sputtered in the 2.4% N<sub>2</sub> ambient was wholly-crystallized with the crystalline grain size of 6-8 nm. However, 2-3 nm-sized nanocrystalline grains and amorphous layers were mixed in the film sputtered in the 5.0% N<sub>2</sub> ambient. Since these nanocrystallites are sufficiently smaller than the gate length and width of MOS transistors, they can be regarded as the uniform gate material.

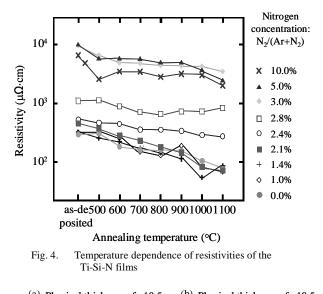

Figure 4 shows the temperature dependence of Ti-Si-N film resistivities. As the N<sub>2</sub> concentration of the sputtering ambient increases, the film resistivity increases, which is related to the increase in the N content of deposited films. Furthermore, the resistivity of the films deposited in the N<sub>2</sub> ambient less than 2.1% reduced by about one order of magnitude with increasing the RTA temperature and, on the other hand, the changes in that of the films deposited in ambient with N<sub>2</sub> concentration more than 3.0% are small in the temperature rage from 500°C to 900°C. The fact that the growth of crystallites does not develop for the high N content films is considered to be a reason for this small resistivity changes.

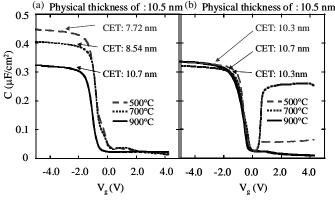

Capacitance-voltage (C-V) characteristics of MOS capacitors with Ti-Si-N gate electrodes are shown in Fig. 5. The measurement frequency was 1 kHz. The N concentrations of the sputtering ambient were (a) 2.4% and (b) 5.0%, respectively. In the case of the 2.4% N<sub>2</sub> ambient, the capacitance equivalent thickness (CET) decreases as the RTA temperature increases, which is due to an interface reaction between the TiSiN and SiO<sub>2</sub>. On the other hand, the CET is not changed in the case of the 5.0% N<sub>2</sub> ambient. Since there is no un-nitrided Ti atom at the interface, an interfacial reaction rarely occurred.

#### 4. Conclusions

We investigated the structural and electrical properties in the mictamict Ti-Si-N gate electrode systems. The Ti-Si-N gates sputtered in the high-nitrogen ambient had near-amorphous states, in which 2-3 nm-sized nanocrystallites and amorphous layers were mixed, and the changes in their resistivity is small after the RTA at temperatures below 900°C. Furthermore, the C-V characteristics of MOS capacitors with the near-amorphous Ti-Si-N gates are also stable against the RTA at 900°C. according to these experimental results, the mictamict Ti-Si-N are promising as a uniform and thermally-stable gate material achieving an extremely-small fluctuation of the workfunction.

Fig. 1. Composition ratio of the Ti/Si and N composition of the Ti-Si-N films

Fig. 2 X-ray diffraction profiles of the Ti-Si-N films deposited in (a) 1.0%, (b) 2.4%, (c) 5.0%, N<sub>2</sub> ambient

#### References

- [1] The International Technology Roadmap for Semiconductors 2005

- [2] R. W. Strayer *et al.*, Surface Science: 34, (1973) p. 225

S. berger. *et al.*, Surface Science: 43, (1974) p.25

- [3] J. A. Kittl et al., Dig. Symp. VLSI Tech; (2005) p. 72

- [4] M-A Nicolet *et al.*, Microelectronic Engineer. **55**, (2001) 357-367.

- [5] M-A Nicolet et al., J. Appl. Phys: 81, No. 2

Fig. 3. Cross-sectional TEM images of the Ti-Si-N gate electrodes formed in (a) 2.4%, (b) 5.0%, N<sub>2</sub> ambient

Fig. 5. Capacitance-voltage (C-V) characteristics of MOS capacitors with Ti-Si-N gate electrodes sputtered in (a) 2.4% and (b) 5.0%, N<sub>2</sub> ambient, respectively