# Top-view imaging of 65nm gate length metal-oxide-semiconductor field effect transistors by scanning capacitance microscopy

Y. Naitou<sup>1a)</sup>, A. Ando<sup>1</sup>, H. Ogiso<sup>1</sup>, S. Kamohara<sup>2</sup>, F. Yano<sup>2</sup>, and A. Nishida<sup>2</sup>

National Institute of Advanced Industrial Science and Technology (AIST)<sup>1</sup>, MIRAI-Selete<sup>2</sup> Phone: +81-29-861-8887 <sup>a)</sup> E-mail address: yu-naitou@aist.go.jp

### 1. Introduction

Nowadays, it is essential for the remarkably miniaturized metal-oxide-semiconductor field effect transistors (MOSFETs) to achieve the expected performance by optimizing the two-dimensional (2-D) carrier profiles. The cross-sectional analysis of device structure by scanning capacitance microscopy (SCM) [1] with their advanced variations [2] and conductive atomic force microscopy [3] are widely used for the carrier concentration diagnostics with high-spatial resolution. The cross-sectional measurements of MOSFET, however, yields only the limited information of device parameters such as channel length  $(L_{met})$  or extension-gate overlap length  $(L_{ov})$  of specific section. Therefore, some prier works have tried to clarify the carrier profiles along the device-width direction [4,5]. In this work, we have demonstrated our SCM application to evaluate the channel structure of MOSFET through the "top-view" imaging.

### 2. Experiment

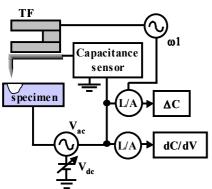

Figure 1 illustrates the schematic diagram of our SCM measurement. To avoid the photoperturbation effect arising from the optical deflection setup [6], a quartz resonator (TF) was employed as a force senser and sharpened bulk tungsten for a conductive probe [7,8]. An AC modulation bias  $(V_{ac})$  and DC offset bias  $(V_{dc})$  was supplied to the sample, while the SCM probe was grounded through the capacitance sensor. Our SCM simultaneously yields three kinds of images of the topography, conventional bias modulated capacitance (dC/dV), and differential static capacitance ( $\Delta C$ ) [9]. For the semiconductor sample measurement, the dC/dV signal was from the modulation of the carrier depletion layer just beneath the SCM probe tip. On the other hand, the  $\Delta C$  signal directly senses the static capacitance between probe tip and the sample hence it can apply for the dielectric film measurement as well as the semiconductor samples. With the use of  $\Delta C$  imaging, a single electron trap within high-k film was successfully observed [10].

MOSFET samples with 65nm gate length were fabricated by the standard production process with source/drain extension (SDE) implantation. HF etching was used to remove the gate structures so that the channel surface was exposed. Before the measurements, samples were air-baked, and illuminated by vacuum ultra-violet (VUV) light to make a thin, uniform oxide layer on the surface. All of the experiments were performed in high vacuum ( $\sim 10^{-4}$  Pa) environment at room temperature.

#### 3. Results and Discussion

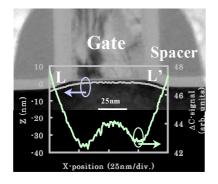

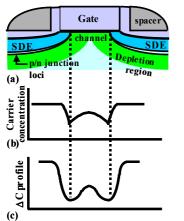

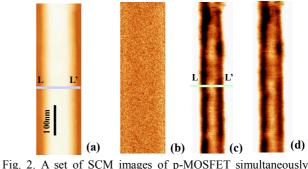

Figures 2(a), (b), and (c) are a set of simultaneously obtained images of p-MOSFET under bias conditions  $V_{ac}=0.4V_{P-P}$  at a frequency of 500 kHz and  $V_{dc}=0V$ . The topography image of Fig. 2(a) shows the convex surface, and there seems no obvious contrast in the dC/dV image of Fig. 2(b). On the other hand, the  $\Delta C$  image of Fig. 2(c) shows dark strips on the both side of channel region. Figure 2(d) is the  $\Delta C$  image from the 2nd scanning from the reverse direction on the same area as in (a)-(c). The observed strips have practically the same contours as that of Fig. 2(c). Therefore, these observed strips in Figs. 2(c) or (d) are not caused by artifacts from the measurement setup. Figure 3 indicates the cross-sectional line profiles along the line L-L' in Figs. 2(a) and (c), together with the cross-sectional TEM image of gate structure with same scale. As shown in Fig. 3, the slow hillock in the topography profile denotes the trace of gate structure, and two dents seen in the  $\Delta C$  profile correspond to the dark strips of Fig. 2(c). Figures 4(a)~(c) present an intuitive explanation of the  $\Delta C$  profile. Fig. 4(a) shows schematic view of device structure and (b) illustrates the distribution of carrier concentration of the active region in a substrate. Carrier concentration varies from SDE to channel region, and reaches its minimum at the locus of the p-n junction. And Fig. 4(c) indicates the corresponding  $\Delta C$  profile. By the nature of its means of detection, the  $\Delta C$  signal detects the depletion capacitance  $(C_{dep})$  within the Si substrate [10]. Together with the former results of bias dependence [4.5], the dent in the  $\Delta C$  profile is considered to correspond to the locus of the p-n junction. Therefore the distance between two minimum of the dents in the  $\Delta C$  profile corresponds to  $L_{met}$ , and the strips in the  $\Delta C$  image can be assessed to the width of carrier depletion region within the channel. The channel region is expected to be entirely depleted, because simultaneously obtained dC/dV image of Fig. 2(b) shows only slight contrast. This suggests that the carrier density of channel region is too low to yield the enough dC/dV signal sensitivity [11][12].

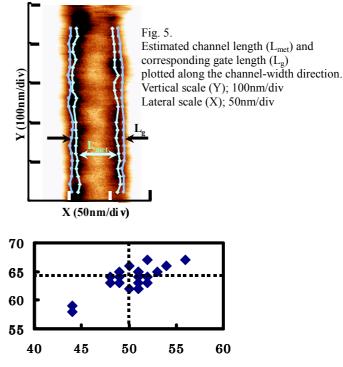

Fig. 5 shows the estimated gate length ( $L_g$ ) and  $L_{met}$  from Figs. 2(a) and (c) for 20 points plotted along the channel-width direction. And Fig. 6 summarizes the correlation diagram between  $L_{met}$  and corresponding  $L_g$ . It can be said from Figs. 5 and 6 that each value of  $L_{met}$  is moderately related to  $L_g$ , however, the spatial fluctuation of  $L_{met}$  is not entirely consistent with that of  $L_g$ . These results suggest that the fluctuation of  $L_{met}$  might be determined not only by the line edge roughness of gate electrode but also by the dopant diffusion.

## 4. Conclusion

We have applied our SCM to visualize the channel structure of 65 nm gate length p-MOSFET through the "top-view" imaging. The spatial variation of obtained  $L_{met}$  is not entirely consistent with line edge roughness of gate electrode, which suggests that the fluctuation of  $L_{met}$  might be determined not only by the line edge roughness of gate electrode but also by the diffusion length fluctuation of dopant.

# Acknowledgements

Part of this work was supported by the NEDO Project.

Fig. 1. Schematic diagram of measurement setup of our SCM.

Fig. 3. Topography and  $\Delta C$  profiles along L-L' in Fig. 2(a) and (c), together with the cross-sectional TEM micrograph of device.

Fig. 4. Schematic illustraton of the relation between device structure, carrier profile, and resultant  $\Delta C$  profile.

#### References

- [1] P. A. Rosenthal, et al., Appl. Phys. Lett. 81, 3993 (2002).

- [2] K. Honda, et al., Appl. Phys. Lett. 86, 063515 (2005).

- [3] P. Eyben, et al., J. Vac. Sci. Technol. B 22, 364 (2004).

- [4] H. Edwards, et al., J. Appl. Phys. 87, 1485 (2000).

- [5] T. Matsukawa, et al., J. Vac. Sci. Technol. B 24, 237 (2006).

- [6] G. H. Buh, et al., J. Appl. Phys. 94, 2680 (2003).

- [7] Y. Naitou, et al., Appl. Phys. Lett. 85, 2131 (2004).

- [8] Y. Naitou, et al., Appl. Phys. Lett. 87, 207551 (2005).

- [9] J. J. Kopanski, et al., Appl. Phys. Lett. 72, 2469 (1998).

- [10] Y. Naitou, et al., J. Appl. Phys. 101, 083704 (2007).

- [11] J. Smoliner, et al., Appl. Phys. Lett. 79, 3182 (2001).

- [12] M. Duane. AIP Conf. Proc. 449 (1998) 715

Fig. 2. A set of SCM images of p-MOSFET simultaneously obtained (a) Topography, (b) dC/dV image, (c)  $\Delta$ C image, and (d)  $\Delta$ C image obtained from the reverse direction scanning. Showing areas are 150 nm x 500 nm in each images.

Lmet (nm)

Fig. 6. Correlation diagram between  $L_{met}$  and corresponding  $L_g.$  The dotted line denotes average value of  $L_{met}$  (50nm) and  $L_g$  (64nm).

Ls (nm)