# Improvement of Electrical Characteristics for Novel Fluorine-Incorporated Poly-Si TFTs with TiN Gate Electrode and Pr<sub>2</sub>O<sub>3</sub> Gate Dielectric

Chia-Wen Chang<sup>1</sup>, Jiun-Jia Huang<sup>1</sup>, Hong-Ren Chang<sup>1</sup>, Jam-Wem Lee<sup>2</sup>, and Tan-Fu Lei<sup>1</sup> <sup>1</sup>Institute of Electronics, National Chiao-Tung University, 1001 Ta-Hsueh Rd., Hsinchu 30010, Taiwan, R.O.C.

Phone: +886-3-5712121-54219 Fax: +886-3-5724361 E-mail: jiawen.ee92g@nctu.edu.tw

<sup>2</sup>Taiwan Semiconductor Manufacturing Company, Hsinchu, 30010, Taiwan, R.O.C.

## Introduction

In recent years low-temperature polycrystalline silicon thin-film transistors (poly-Si TFTs) have been widely used in active-matrix liquid crystal displays (AMLCDs) [1]. The major application of poly-Si TFTs in AMLCDs lies in integrating the peripheral driving ICs, and the pixel switching elements on the glass substrate to realize system-onpanel (SOP) purpose [2]. The peripheral driving ICs have the electrical characteristics requirement of low operation voltage, low threshold voltage, and high driving current, however conventional solid-phase crystallization (SPC) poly-Si TFT with SiO<sub>2</sub> as gate dielectric can not satisfy the needs. In order to address this issue, several high- $\kappa$  gate dielectrics including  $HfO_2$  and  $LaAlO_3$  were proposed to increase the gate capacitance density for better gate controllability with keeping physical gate dielectric thickness [3], [4]. However, unfavorable gate-leakage was introduced from the crystalline high-k material [5]. Recently, Praseodymium oxide  $(Pr_2O_3)$  becomes a promising high- $\kappa$  material with high  $\kappa$  value, low gate-leakage, and superior thermal stability [6]. On the other hand, the detrimental GIDL current from the grain boundaries trap states was observed in the unhydrogenated poly-Si TFT [7]. Hence, fluorine ion implantation was utilized to passivate the trap states to improve the device performance [9],[10]. But it may not be suitable for glass application due to unfeasible large area implantation and high dopant activation annealing.

In this paper, an effective, low-cost, and processcompatible fluorine-based plasma treatment on poly-Si was proposed. We integrated TiN gate, high- $\kappa$  Pr<sub>2</sub>O<sub>3</sub> gate dielectric, and CF<sub>4</sub> plasma treatment with TFTs for the first time.

# 2. Experimental

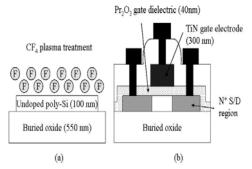

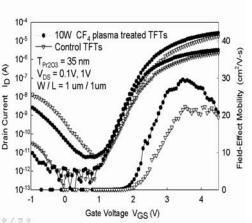

The cross-sectional schematic diagram and the transmission electron microscopy (TEM) micrograph of the proposed metal gate, high- $\kappa$  dielectric TFT are shown in Figs. 1, and 2. Briefly, the fabrication begins by depositing a 100-nm undoped amorphous silicon ( $\alpha$ -Si) layer on a thermally oxidized Si wafers, followed by the SPC process. After the definition of active region, a CF<sub>4</sub> plasma was performed at 350 °C for 15 s with pressure of 200 mtorr and power of 10 W in PECVD chanber. Next, a 35-nm Pr<sub>2</sub>O<sub>3</sub> film was deposited by e-gun evaporation system, followed by a furnace annealing at 600 °C for 30 min in O<sub>2</sub> ambient to improve the gate dielectric quality. A 300-nm TiN film was sequentially deposited, and then patterned to form

gate electrode. Next, a self-aligned source/drain implantation, dopant activation, passivation oxide, contact hole, metal pads, and  $N_2/H_2$  sintering were successively performed. For comparison, the control TFT without the CF<sub>4</sub> plasma treatment was prepared with the same process flow.

### 3. Results and Discussion

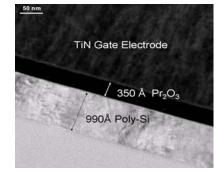

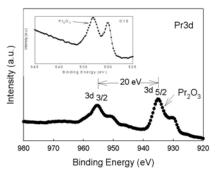

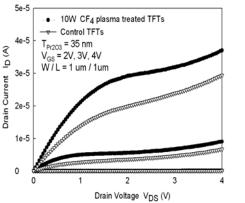

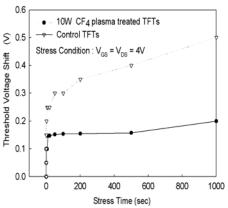

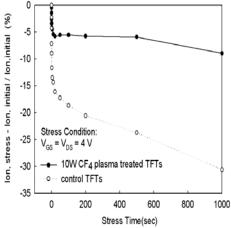

As shown in Fig. 3, the measured XPS spectra of the Pr 3d and O 1s core levels for Pr<sub>2</sub>O<sub>3</sub> are in good agreement with previous data to well confirm the chemical composition of  $Pr_2O_3$ . Typical  $I_{DS}$ -V<sub>GS</sub> and  $I_{DS}$ - $V_{DS}$  of the integrated TiN gate and high- $\kappa$  Pr<sub>2</sub>O<sub>3</sub> TFTs with and without CF<sub>4</sub> plasma treatment are shown in Figs. 4, and 5; moreover, the key parameters were summarized in the table. 1. As CF<sub>4</sub> plasma is performed prior high- $\kappa$  deposition, Vth decreased from 2.55 V to 2.28 V, S.S. decreased from 648 mV/dec to 575 mV/dec,  $I_{ON}/I_{OFF}$  increased from 0.92 x 10<sup>7</sup> to1.34 x 10<sup>7</sup>, and trap density decreased from 5.23 x 10<sup>12</sup> cm<sup>-2</sup> to 2.89 x 10<sup>12</sup> cm<sup>-2</sup>. This excellent performance is desirable for high-speed display IC's application resulted from the high gate capacitance density of 5.68 x  $10^{-7}$  F/cm<sup>2</sup> from C-V measurements, which gives a small equivalent-oxide thickness (EOT) of 6.07 nm. Furthermore, the effective  $\kappa$  value of  $Pr_2O_3$  is extracted to be 22.5 from the physical thickness of  $Pr_2O_3$  films, equal to 35nm, as shown in Fig. 2. Additionally, hot-carrier stress was applied at  $V_D$  =  $V_G = 4 V$  for 1000 s to examine the electrical reliability. The threshold voltage variations and the on-current degradation that resulted from the broken Si-Si and Si-H bonds during hot-carrier stress [11] are shown in Figs. 6, and 7. It was found that the CF<sub>4</sub> plasma treated TFTs have high immunity against the hot carrier stress as compared to control TFTs. Hence, the significant improvement in the electrical reliability can be attributed to the formation of stronger Si-F bonds in place of weaker Si-Si and Si-H bonds in the poly-Si.

#### 4. Conclusion

A low cost, effective and process-compatible fluorine-incorporated technique is proposed. We have successfully combined TiN gate,  $Pr_2O_3$  gate dielectric, and  $CF_4$  plasma to fabricate high-performance poly-Si TFTs.

#### Acknowledgements:

The authors thank the apparatus support from National Nano Device Laboratories (NDL) and the financial support by the National Science Council (NSC) under contact no. NSC 95-2221-E-009-279.

Fig. 1. Schematic diagram of the combined TiN gate and Pr<sub>2</sub>O<sub>3</sub> gate TFT dielectric with CF<sub>4</sub> plasma treatment, (a)  $CF_4$  plasma treatment on active region. Cross-sectional diagram of the proposed TFT structure.

Fig. 4. Comparison of  $I_D - V_G$ characteristics for control TFTs and  $CF_4$  plasma treated TFTs (W/L = 1  $\mu m / 1 \mu m$ ).

Fig. 2. Cross-sectional TEM image of the proposed high-k Pr2O3 gate dielectric TFT structure.

Fig. 3. Pr 3d photoelectron spectrum for Pr<sub>2</sub>O<sub>3</sub>. The inset also shows the O 1s photoelectron Spectrum which clearly indicates the presence of Pr<sub>2</sub>O<sub>3</sub>.

Fig. 5. Comparison of  $I_D - V_D$ characteristics for control TFTs and CF4 plasma treated TFTs (W/L = 1  $\mu$ m / 1 μm).

Fig. 6. Threshold voltage variation versus stress time for the control and CF<sub>4</sub> plasma treated TFTs.

Table 1. Key device characteristics for the CF<sub>4</sub> plasma treated TFTs and control TFTs

| Control<br>TFT | CF <sub>4</sub> plasma<br>treated TFT |

|----------------|---------------------------------------|

| 2.55           | 2.28                                  |

| 648            | 575                                   |

| 22.33          | 29.57                                 |

| 5.23           | 2.89                                  |

| 0.92           | 1.34                                  |

|                | TFT<br>2.55<br>648<br>22.33<br>5.23   |

Fig. 7. On-current degradation versus stress time for the control and CF4 plasma treated TFTs.

#### **References:**

- [1] T. Nishibe, in Proc. Mater. Res. Soc. Symp. (2001) 685E.

- [2] B. D. Choi, H.-S. Jang, O.-K. Kwon, H.-G. Kim, and M. J. Soh, IEEE Trans. Consum. Electron. 100 (2000) 21.

- Chia-Pin Lin, Bing-Yue Tsui, Ming-Jui Yang, [3] Ruei-Hao Huang, and Chao-Hsin Chien, IEEE

- Electron Device Lett. 27 (2006).

[4] B. F. Hung, K. C. Chiang, C. C. Huang, Albert Chin, and S. P. McAlister, IEEE Electron Device Lett. 26 (2005).

- [5] Dim-Lee Kwong, in Proceedings of 11th IPFA, IEEE, Taiwan, invited paper (2004) 16 [6] H. J. Osten, J. P. Liu, P. Gaworzewski, E. Bugiel,

- and P. Zaumseil, in IEDM Tech. Dig. (2000) 653. I. W. Wu, A. G. Lewis, T. Y. Huang, and A. Chiang, IEEE Electron Device Lett. 10 (1993) [7] 2061.

- [9] H. N. Chern, C. L. Lee, and T. F. Lei, IEEE Trans. Electron Devices, 41 (1994) 698.

- [10] S. Maegawa, T. Ipposhi, S. Maeda, H. Nishimura, Ichiki, M. Ashida, O. Tanina, Y. Inoue, T. shimura, and N. Tsubouchi, IEEE Trans. Т Nishimura, and N. Tsubouchi, Electron Devices, 42 (1995) 1106.

- [11] S. Banerjee, R. Sundaresan, H. Shichijo, and S. Malhi, IEEE Trans. Electron Devices 35 (1988) 152.