## P-4-3

# Electronic characteristics of charge trapping memory using Al<sub>2</sub>O<sub>3</sub> dielectric

Y. J. Seo<sup>1</sup>, K. C. Kim<sup>1</sup>, H. D. Kim<sup>1</sup>, M. S. Joo<sup>2</sup>, Y. T. Kim<sup>2</sup>, S. H. Pyi<sup>2</sup>, H. Y. Cho<sup>3</sup> and T. G. Kim<sup>1</sup> <sup>1</sup>Dept. of Electronics Eng., Korea Univ., Seoul 136-701, Korea

<sup>2</sup>Advanced Process division, Hynix Semiconductor Inc., Gyeonggi-do 407-701, Korea <sup>3</sup>Dept. of Physics, Dongguk Univ., Seoul 100-715, Korea

Dept. of Physics, Dongguk Univ., Seour 100-715, Korea

Phone: +82-2-924-5119, Fax: +82-2-924-5119, E-mail: tgkim1@korea.ac.kr

### 1. Introduction

The SONOS structure has become an appealing alternative for the next-generation flash memory applications because of its numerous advantages such as film scalability, process simplicity, and power economy. However, as the nitride thickness and the gate size are reduced in nano scale, charges are trapped close to the gate electrode and most of them are lost through the gate electrode, resulting in data loss. In order to improve the scaling properties of the devices for the sub 100nm flash technology node, high- $\kappa$  materials such as Al<sub>2</sub>O<sub>3</sub> are interesting alternatives to the standard dielectrics such as silicon dioxide and silicon nitride. Al<sub>2</sub>O<sub>3</sub> has a large energy band gap value of 8.9eV, a large conduction band offset of 2.8eV with respect to silicon, and a dielectric constant value of 9, making it an attractive candidate as a blocking oxide. Furthermore, this structure can be achieved longer data retention and realized lower voltage programming than the conventional ONO structure. In this study, we compare SiO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> as a blocking dielectric in a metal-insulators-semiconductor (MONOS, MANOS) type capacitors similar to the well known SONOS and SANOS devices [1].

### 2. Experiments

Four samples of ONO, ONA,  $Si_3N_4$  and  $SiO_2$  on n-type Si substrates were prepared as shown in Table 1. The tunneling oxide was grown by thermal oxidation while the blocking oxide and the nitride layer were deposited by low pressure chemical vapor deposition (LPCVD). Rapid thermal annealing is performed in N<sub>2</sub> gas at 900 °C for 1 min.

Table 1. Thickness of the structures

|                                | Tunneling  | Trapping   | Blocking |

|--------------------------------|------------|------------|----------|

|                                | layer( Å ) | layer( Å ) | layer(Å) |

| ONO                            | 20         | 60         | 65       |

| ONA                            | 20         | 60         | 150      |

| Si <sub>3</sub> N <sub>4</sub> | 0          | 150        | 0        |

| SiO <sub>2</sub>               | 150        | 0          | 0        |

Then, either metal-oxide-semiconductor (MOS) or MIS type capacitors was fabricated for capacitance-voltage (C-V) and deep level transient spectroscopy (DLTS) measurements. Al gates with a diameter of 0.3mm were formed on the blocking layer by thermal evaporator while In contact was made on the substrate for Ohmic contacts.

#### 3. Results

In order to investigate memory effect, C-V measurement was performed, respectively [2].

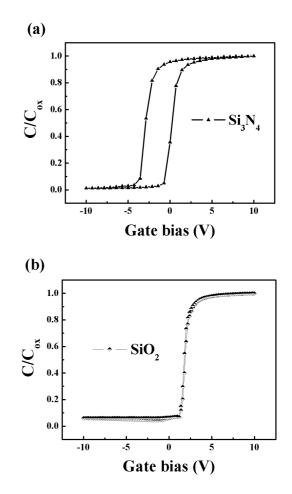

Fig. 1 CV hysteresis (a) Si<sub>3</sub>N<sub>4</sub> (b) SiO<sub>2</sub> on n-type Si substrate

Figure 1 exhibits C-V hysteresis after bi-directional voltage sweeping. The voltage was swept between 10 and -10V. The erasing and programming voltages were fixed at -10V and 10V, respectively. The difference between the charging and discharging point, which is referred to as the "memory window", was ~3.0V for the Si<sub>3</sub>N<sub>4</sub>/Si (MIS) capacitor, and 0V for the SiO<sub>2</sub>/Si (MOS) capacitor. The memory effect was not observed for the oxide layer fabricated on n-type Si substrates. Figure 2 shows C-V hysteresis curves for the ONO and ONA structures.

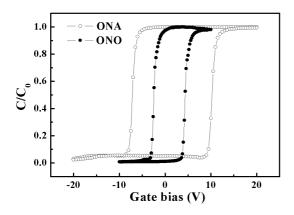

Fig. 2 CV hysteresis of ONO and ONA on n-type Si substrate

We found that leakage current was produced in the ONO and ONA capacitor at more than 10V and 20V bias sweeping condition. This bias condition is referred to as the "critical bias point". At critical bias point, structure has the maximum memory window. The maximum memory window were  $\sim$ 5.5V for the ONO capacitor and  $\sim$ 18V for the ONA capacitor

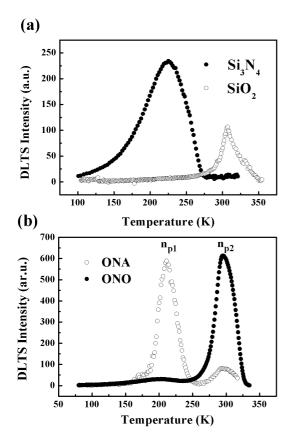

Fig. 3 DLTS signal of (a)  $Si_3N_4$ ,  $SiO_2$  (b) ONO and ONA on n-type Si substrate

The DLTS study was then performed to get more detailed information on the spatial distribution of the memory traps available in the ONO and ONA structure. Figure 3 shows the DLTS spectra measured from the Si<sub>3</sub>N<sub>4</sub> (MIS), SiO<sub>2</sub> (MOS), ONO and ONA capacitors fabricated on the n-type Si substrates. The MIS and MOS structures were prepared as the reference for identifying the origin of the trap present in the ONO and ONA structure. In both ONO and ONA capacitor, two DLTS peaks were observed at around 200K (n<sub>p1</sub>) and 300K (n<sub>p2</sub>), respectively. We attributed n<sub>p1</sub> and n<sub>p2</sub> to the nitride traps (traps related to the nitride layer) and interfacial traps (traps related to the interface between Si and SiO<sub>2</sub>), respectively, by comparison with the DLTS signals of the MIS and MOS capacitor.

For the ONO and ONA structures, they showed a reverse relation in its peak intensity. That is,  $n_{p2}$  representing the interface trap density was dominantly observed in the ONO structure while  $n_{p1}$  representing the nitride trap density was dominant in the ONA structure. Since the interface traps between Si and SiO<sub>2</sub> could be a factor that can degrade device reliability (or retention), they should be reduced This is also accounted for why the memory window of ONO is always observed to be narrower than that of the ONA structure. In this work, we carefully conclude that the ONA structure holds benefits inherently for the application to charge-trap memory device over the ONO structure. The trap activation energy (E<sub>a</sub>) and trap concentration (N<sub>T</sub>) of the ONO and ONA structures are listed in Table 2.

Table 2. E<sub>a</sub> and N<sub>T</sub> of the ONO and ONA structure

|                 | ONO                 |                             | ONA                 |                             |

|-----------------|---------------------|-----------------------------|---------------------|-----------------------------|

|                 | E <sub>a</sub> (eV) | $N_{T}$ (cm <sup>-3</sup> ) | E <sub>a</sub> (eV) | $N_{T}$ (cm <sup>-3</sup> ) |

| n <sub>p1</sub> | 0.27                | $2.45 \times 10^{13}$       | 0.27                | $2.00 \mathrm{x} 10^{14}$   |

| n <sub>p2</sub> | 0.54                | $3.93 \mathrm{x} 10^{14}$   | 0.55                | $4.00 \mathrm{x} 10^{13}$   |

More details on the experiment will be presented at the conference

#### 4. Conclusions

The C-V and DLTS analyses were made for both ONO and ONA capacitors to have information on the memory effect and the origin of charge traps. The memory window and the DLTS signals related to the nitride traps were always dominantly observed for the ONA structure, compared with those of the ONO structure. Reduction in the memory window observed by C-V for the ONO structure is thought to be due to the interface traps dominant between Si and SiO<sub>2</sub>. These results directly show that the ONA structure is more suitable than ONO for the application to charge-trap memory devices.

#### Acknowledgements

This work was financially supported by the Hynix Company as well as the MOST/KOSEF through the Quantum Photonic Science Research Center, Korea.

#### References

- [1] M.Specht, H.Reisinger, M.Stadele et al, *IEEE 33<sup>rd</sup> conference* on. ESSDERC (2003) 155

- [2] J. S. Oh, C. J. Park, and H. Y. Cho, ECS Trans., 1, 5(2006)