# P-4-4

# Low temperature Poly-Si TFT nonvolatile memory devices with In<sub>2</sub>O<sub>3</sub> nano-particles embedded in polyimide

Hyun-Mo Koo, <sup>1</sup>Dong Uk Lee, <sup>1</sup>Seon Pil Kim, <sup>1</sup>Eun Kyu Kim, <sup>2</sup>Jongwan Jung and Won-Ju Cho

Department of Electronic Materials Engineering, Kwangwoon University, Seoul 139-701, Korea

<sup>1</sup>Quantum-Function Spinics Lab., Department of Physics, Hanyang University, Seoul 133-791, Korea

<sup>2</sup>Department of Nano Science and Technology, Sejong University, Gwangjin-gu, Seoul 143-747, Korea *Phone:* +82-2-940-5163, *E-mail: chowj@kw.ac.kr*

#### 1. Introduction

The polycrystalline silicon thin-film transistor (poly-Si TFT) has been applied in the active matrix liquid crystal display applications due to high electric field-effect-mobility and large drivability [1]. Especially, the low temperature poly-Si (LTPS) TFT is also expected to be a key devices to the development of system-on-glass (SoG) at flat panel display since it makes compact, and low power TFT LCD for mobile terminal devices [2]. In this paper, we report the electrical performance of low temperature poly-Si TFT nano-crystal floating gate memory (NFGM) with  $In_2O_3$  nano-particles embedded in polyimide insulating layer and compares the performance of the TFT NFGM with that of silicon-on-insulator (SOI) NFGM.

#### 2. Experimental

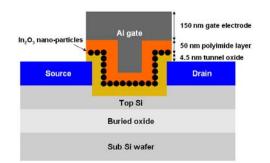

We fabricated the floating gate memory devices with In<sub>2</sub>O<sub>3</sub> nano-particles on the poly-Si films crystallized by ELA (excimer laser annealing) method. The same type control sample was also fabricated on the SOI wafers for comparison. Source/drain regions were defined before the formation of gate stacks (tunnel oxide/In2O3 nanoparticle/polyimide blocking insulator) to avoid the thermal damages of polyimide insulating layers by using the in-situ phosphorous doped poly-Si films. Then, the phosphorus in-situ doped poly-Si layer was partially removed to form the channel region. After formation of tunneling gate oxide with a thickness of 4.5 nm, the thermal evaporation of indium layer of 5 nm and the spin coating of polyamic acid (PAA) with a 50 nm thickness were sequentially followed. Then, the chemical reactions between indium ion and PAA for the formation of the In<sub>2</sub>O<sub>3</sub> nano-particles inside the polyimide matrix occurred by the curing process. The aluminum was deposited by thermal evaporation and the gate electrode was formed. Finally, the fabricated devices were annealed in 3% diluted hydrogen (H<sub>2</sub>/N<sub>2</sub>) ambient at 400°C for 30 minutes to improve the electrical characteristics.

### 3. Results and discussions

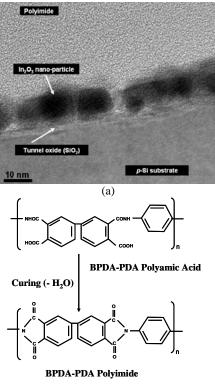

Fig. 1 shows the cross-section TEM image of  $In_2O_3$  nano-particles embedded in polyimide layer after curing process of 400°C for 1 hour. The  $In_2O_3$  nano-particles

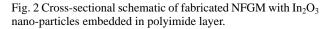

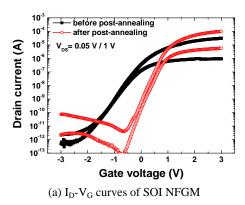

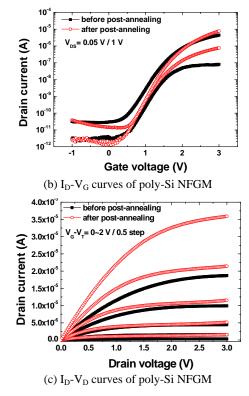

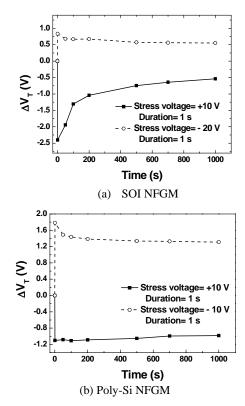

shows the spherical shape with an average diameter of 7 nm and the particle density is about  $6 \times 10^{11}$  cm<sup>-2</sup>. Fig. 2 shows the cross-sectional schematic of a fabricated device. The channel length and width are 10 µm and 20 µm, respectively. Fig. 3 shows the subthreshold characteristics and the output current characteristics of the fabricated TFT NFGM and the controlled SOI NFGM with both In<sub>2</sub>O<sub>3</sub> nano-particles in polyimide. It is found that the electrical characteristics are considerably improved after annealing of 3% diluted hydrogen (H<sub>2</sub>/N<sub>2</sub>) ambient at 400°C for 30 m. The decrease of subthreshold swing and the increases of drain current are observed in both NFGM devices fabricated on poly-Si film and SOI wafer. Fig. 4 shows the retention characteristics of the fabricated NFGM devices. Although the memory window of NFGM without  $In_2O_3$  nano-particles is less than 0.2 V, the window increases to 3.0 V by inserting the In<sub>2</sub>O<sub>3</sub> nanoparticles in polyimide layer. Additionally the charge retention characteristics were significantly improved by post annealing in 3% diluted hydrogen (H<sub>2</sub>/N<sub>2</sub>) ambient. It is considered that these improved electrical characteristics are associated with the reduction of interface traps at the tunnel oxide/polyimide interface as well as bulk traps in polyimide layer. Furthermore, the retention characteristics of poly-Si NFGM are comparable to that of SOI NFGM.

#### 4. Conclusions

The NFGM devices with  $In_2O_3$  nano-particles were fabricated on the SOI wafers and poly-Si films. The  $In_2O_3$ nano-particles have spherical shape with an average diameter of 7 nm and the particle density was about  $6 \times 10^{11}$  cm<sup>-2</sup>. Thin SiO<sub>2</sub> as a tunnel oxide,  $In_2O_3$  nanoparticles as nano storages and polyimide layer as a blocking insulator were sequentially stacked on the SOI or poly-Si channel. The post-annealing in 3% diluted hydrogen (H<sub>2</sub>/N<sub>2</sub>) ambient at 450°C for 30 m significantly improved the electrical characteristics of  $In_2O_3$  nanoparticles embedded NFGM. The retention characteristics of poly-Si NFGM are comparable to that of SOI NFGM. Therefore, we can conclude that the NFGM device using low temperature processes fabricated on the poly-Si film can be applied to the SoG in flat panel display.

## References

- [1] H. Oshima et al. IEDM Tech. Dig., 1989, pp. 157-160

- [2] Y Nakajima et al. SID 04 Dig.m 2004, pp. 864-867.

(b)

Fig. 1 Cross-sectional TEM image of  $In_2O_3$  nano-particles embedded in polyimide layer (a) and molecular structure of polyimide layer (b).

Fig. 3 Subthreshold characteristics and output current characteristics of fabricated NFGM with  $In_2O_3$  nano-particles embedded in polyimide layer and effects of 3% diluted hydrogen  $(H_2/N_2)$  post-annealing.

Fig. 4 Retention time characteristics of fabricated NFGM with  $In_2O_3$  nano-particles embedded in polyimide layer.