# Capability of Electro-thermal simulation for Automotive Power Application Using Novel LDMOS Model

Takashi Kojima<sup>1</sup>, Takahiro Kajiwara<sup>2</sup>, Masataka Miyake<sup>2</sup>, Uwe Feldmann<sup>2</sup> and Mitiko Miura-Mattausch<sup>2</sup>

<sup>1</sup>Toyota Central R&D Labs., Inc., Electronic Circuit Lab. Nagakute, Aichi 480-1192, Japan Phone: +81-561-71-7205 E-mail: t-kojima@mosk.tytlabs.co.jp <sup>2</sup>Hiroshima Univ., Graduate School of Advanced Sciences of Matter 1-3-1 Kagamiyama, Higashi-Hiroshima, Hiroshima 739-8530, Japan

## 1. Introduction

Temperature rises of Si power devices are the most important issue for design of automotive electrical components. Thermal simulations by FEMs are widely used for temperature prediction. However, electrical characteristics of Si devices are strongly depend on these temperature, electrothermal coupling simulation techniques are therefore required to estimate the thermal behavior. The table look-up methods were proposed for reducing calculation time[1][2]. However, replacement of the look-up tables are necessary when circuit parameters are changed. On the other hand, fast and accurate MOSFET compact models are beginning to be applied to power electronics simulations. We have implemented self-heating effect in HiSIM HV model, and realized electro-thermal coupling simulations without look-up tables because of its stable and fast-speed performance. This paper describes practical use of thermal simulation in SPICE3 for power module structure with water cooling.

## 2. Electro-thermal Coupling Simulation

Components of Electro-thermal Coupling Simulation

Device temperature is calculated by following procedure in electro-thermal coupling simulations;

- 1. An instantaneous device power loss is generated by applied current and voltage into the power device.

- 2. The device power loss is applied to the thermal model, and the instantaneous device temperature is generated.

- 3. The temperature dependent device model parameters are determined using the device temperature.

These calculations are performed simultaneously using a circuit simulator. The device models and the thermal models are essential components of electro-thermal simulations. *LDMOS Model*

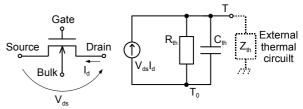

HiSIM\_HV is a novel LDMOS compact model whose key feature is the accurate and consistent modeling of the resistance effect in the drift region[3]. Both internal and external thermal network consisted of electrical resistances and/or electrical capacitances are available in the model. The device temperature is obtained at the temperature node T as a voltage (Fig. 1).

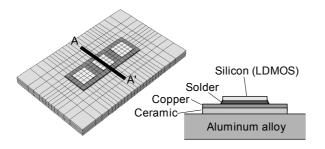

*Thermal Model and Its Implementation approach to SPICE3* Fig. 2 shows the structure of virtual power module that

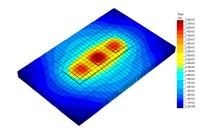

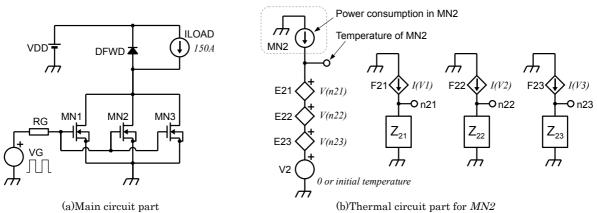

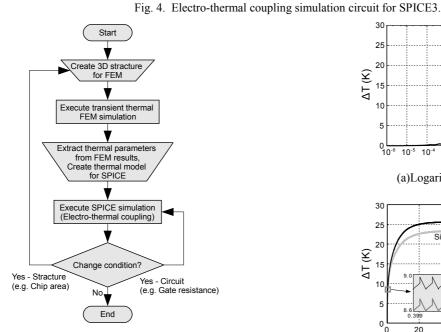

rig. 2 shows the structure of virtual power module that we evaluated HiSIM\_HV and simulation method. Thermal interference occurs among three devices in this structure (Fig. 3). The RC compact thermal model is required for carrying out the electro-thermal coupling simulation, because the model can be implemented using a circuit simulator easily. We chose the Foster network as the thermal model. Although the Foster network is a behavior model, it has advantages of easiness of RC parameter extraction and high accuracy with a small number of nodes[1]. We configured the circuit shown in Fig. 4 to represent the thermal interference in SPICE3. The whole procedure for electro-thermal coupling simulations is shown in Fig. 5. Replacements of the look-up table which are required for the table look-up methods are no longer necessary for the procedure using HiSIM\_HV because of its stable and fast-speed performance.

# 3. Simulation Results and Discussion

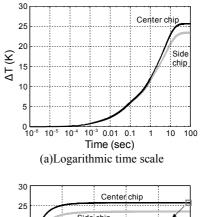

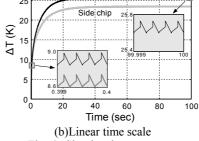

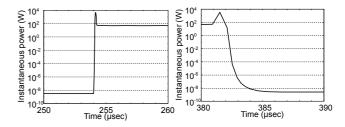

We executed the circuit simulation shown in Fig. 4 under the condition listed in Table I. The final time was determined by thermal saturation time of the power module. Figure 6 shows the simulation results. Switching behaviors of the LDMOSs shown in Fig. 7 were calculated with duration of 100 seconds. It took six hours which would be a very short time to complete the simulation. We performed same simulation based on commercially available simulator using a Power MOSFET model which is similar to MOS level 3 model. Although node number of the thermal network was reduced to 1/50 in comparison with SPICE3 based simulation, it took three times calculation time more than SPICE3 based one. These results shows that stable and fast simulation is available using HiSIM\_HV model. The reasons why the simulation has completed in such a short time are;

- 1. A consistent device temperature can be obtained from the temperature node of HiSIM HV.

- 2. This surface potential distribution based model is stable by itself.

### 4. Conclusions

We have developed a methodology, which enables to simulate electro-thermal coupling simulations in a consistent way by using HiSIM\_HV. The result verifies that methodology provides stable and fast simulation for real automotive applications with power devices within 1/3 of simulation time by a widely used conventional simulator.

### References

- T. Kojima, Y. Yamada, Y. Nishibe and K. Torii, Proc. 4th Power Conversion Conference (2007) 1025.

- [2] Z. Zhou, M. S. Khanniche, P. Igic, S. T. Kong and P. A. Mawby, Proc. Int. Power Electronic Conf. (2005) 1101.

- [3] M. Yokomichi, M. Miyake, T. Kajiwara, N. Sadachika, A. Yumisaki, H.J. Mattausch and M. Miura-Mattausch, *Proc. Int. Conf. on Solid State Devices and Materials* (2007) 738.

Fig. 1. LDMOS model which includes self-heating effect.

Fig. 2 Structure of power module.

Fig. 3. Difference of temperature between center chip and side chip because of thermal interference.

(a)Main circuit part

Fig. 5. Procedures for electro-thermal coupling simulation.

| Simulator                               | SPICE3F5 (HiSIM_HV is implemented)         |

|-----------------------------------------|--------------------------------------------|

| CPU                                     | Intel Xeon 5160 3 GHz (Core™ architecture) |

| Used memory                             | 2GB                                        |

| Calculation time                        | 6 hours                                    |

| Carrier frequency<br>(Switching period) | 4 kHz (250 μs)                             |

| Final time<br>(TSTOP)                   | 100 seconds                                |

| Maximum time step<br>(TMAX)             | 200 µs                                     |

| Simulator variables (.OPTIONS)          | none                                       |

Fig. 6. Simulated temperature.

Fig. 7. Power loss waveforms during electro-thermal coupling simulation