## H-8-4

# Silicon based Technology for Single Dopant Orbital Transistor

R.Wacquez<sup>1,2</sup>, M.Sanquer<sup>1</sup>, M.Vinet<sup>2</sup>, X.Jehl<sup>1</sup>, M.Pierre<sup>1</sup>, S.Pauliac-Vaujour<sup>2</sup>, G.Molas<sup>2</sup>, T.Poiroux<sup>2</sup>, G.Guegan<sup>2</sup>, S.Deleonibus<sup>2</sup>, D. Kern<sup>3</sup>

<sup>1</sup>INAC and <sup>2</sup> LETI/MINATEC, CEA-Grenoble 17 rue des Martyrs, 38054 Grenoble cedex 9, France

<sup>3</sup> Institut für Angewandte Physik, Universität Tübingen, Auf der Morgenstelle 10, 72076 Tübingen, Germany

Contact : romain.wacquez@cea.fr

## Introduction

Standard CMOS technology is reaching some limits with next technological nodes. Alternative architectures are proposed in order to continue scaling down to 11 nm node [1-5]. Nevertheless variability issue, caused by process dispersion, becomes critical, even for 45 nm node. And solutions, like designing circuits at the worst case rules, lead to an increase in power consumption.

One major issue for variability is channel doping. Efforts for atomic control of dopants are pursued worldwide [6-8] and the detection of single dopant is possible by transport [9, 20] or charge sensing methods [10]. Atomic control will improve FET performance for devices above the 45 nm node [6] but will also allow new operating modes for more aggressive devices, based on the convergence between the FET and the SET [11].

By analogy with transport through atomic orbitals from bottom-up approaches (break junctions [12], molecular transport [21]), the

European project AFSID (Atomic Functionalities on Silicon Device) will consider a top-down technique. It combines a competitive silicon technology with single ion implantation to compare switches based on single dopant atomic orbitals and those based on artificial silicon atoms.

#### **1.** Single atomic orbital transistors (SAT)

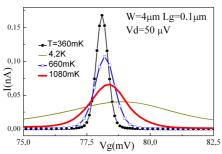

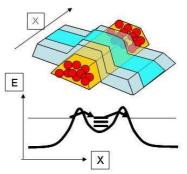

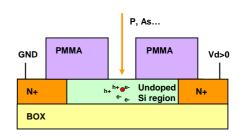

The source drain current of devices containing numerous dopants could be dominated by resonant transport through a single dopant [7]. The advanced CMOS developed within the microelectronics platforms permits to reach the limit where in average one single dopant is implanted below the gate (see fig 1). The top gate which protects the channel during source-drain implantation allows the transmission through the single dopant to be tuned. A further step could be accomplished by detecting in-situ the implantation of a single dopant thanks to the IBIC technique [8] or thanks to the modification of the drain current [7]. Although variability in the 10nm range on the dopant could be determined afterwards by transport spectroscopy measurements performed at low temperature. The resulting SAT will be a switch of very good electrostatic intregrity, and low power consumption.

### 2. Silicon artificial atoms (ultimate MOS-SET)

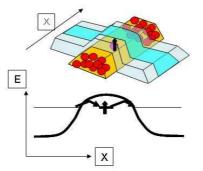

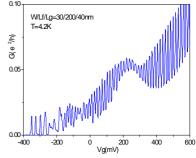

Recent works show that controllable Silicon SET using a single gate, self aligned spacers and doping modulation have size in the 30 nm range and charging energy of few meV [13]. Recent advances in silicon technology also suggest that such devices can be made even smaller, forming artificial atoms from undoped silicon channel. Because of the proximity in terms of architecture and design for the SAT and the ultimate MOS-SET (fig 2)- the main difference relying in the channel and LDD doping level (see figures 3 and 4)- the comparison of their performances will be very fruitful to evaluate the advantages of silicon SET, resonant tunnelling devices and FET as electrical switches.

## 3. Silicon based technology.

## Transistor fabrication

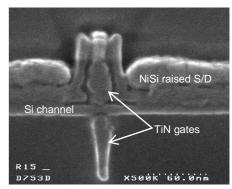

The starting substrate is SOI. After having thinned down the silicon film to the desired value, we perform channel implantation. A MESA isolation is used to define active area. Then 4 nm gate oxide is grown and N+ doped polysilicon is deposited as a gate metal. Nitride spacer is realized and its thickness can be tuned leading to either overlapped or underlapped device. Then raised S/D are performed. Next step is HDD implantation, and we end the S/D module definition by Ni silicide. Standard encapsulation finishes the fabrication of the device.

## Channel implantation

For the single atomic orbital transistor, the objective is to obtain a single dopant in the silicon wire defining the channel. Two solutions are proposed.

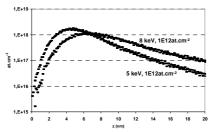

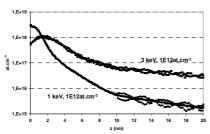

First, a dose implant of 1E12 at.cm<sup>-2</sup> corresponds to an average of a single atom per 10\*10 nm<sup>2</sup>, which is our objective in terms of channel dimension. Energy is then adapted in function of the thickness of the channel. Fig 5 & Fig 6 shows doping profiles in Si, based on CTRIM simulation for two species: Se and P, shallow impurity and deeper one (for higher temperature functionality), through 2 nm of SiO<sub>2</sub>. For each ion, optimal energy is chosen so that R<sub>p</sub> is in the middle of the channel and the maximum dose corresponds to an average of an atom in a box of 10\*10\*10 nm<sup>3</sup>(1E18 at.cm<sup>-3</sup>). Then measurements and statistical studies will enable localisation of dopants in Si layer thanks to a large amount of samples fabricated in LETI clean room.

Second technique will use a skill developed by the University of Melbourne and based on IBIC (Ion Beam Induced Charge) [8]. Indeed a Phosphorus ion implanted at 14 keV leads to the creation of about 1000 electron holes pairs. So the technique consists in detecting the formation of these pairs by collecting electrons in the drain of the device thanks to a transverse field (fig 7). Alternatively implantation could be detected by induced variation of channel conductance in our very small structures.

#### Lithographic performance

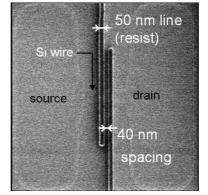

On one side, Si structures in the 10 nm range are required for quantization energy in the 10 meV regime and coulomb charging energies around 50 meV, above  $k_BT=25$  meV at room temperature. On the other side, to achieve complex functionalities SET and SAT need to be efficiently capacitively coupled to each others [14-15]. Thus lithography is asked at the same time to have high resolution in terms of minimal size and spacing and good overlay performance.

Usual trimming process is not adapted at this aim, because reducing the size of patterns it also increases the spacing between them. Therefore lithographic process is critical.

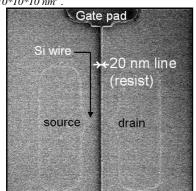

High resolution Gaussian electron beam lithographic tool will enable this ultimate resolution. Combined with NEB35 resist [16], 20 nm line width is obtained (fig 8) and spacing down to 40 nm (fig 9). Alignment strategy is also well controlled. It ensures precision of alignment between two levels below 10 nm (fig 10). Thin film process

#### The most ultimate resolution must be obtained along x and y axis, but also in the thickness of the devices. So we take advantage of the experience of the LETL in processing thin films devices [17]

the experience of the LETI in processing thin films devices [17]. It is helped by successful epitaxial process on thin films [18], below 10 nm. It enables the salicidation of S/D and the optimization of the resistance.

#### Conclusion

The combination of CMOS platform facilities with controlled single dopant implantation enables fabrication of switches based on tunable single dopant orbital. SET-FET convergence will be tested by comparing single dopant FET and undoped SET of the same size.

## Aknowledgements

The research leading to these results has received funding from the European Community's seventh Framework (FP7 2007/2013) under the Grant Agreement nr:214989. The samples subject of this publication have been designed and made by the AFSID Project Partners. [1] International Technology Roadmap for Semiconductor (2007)

[2] S.Harrison et al., IEDM Tech Dig, 2003, p449

- [3] S.Y Lee, Symp VLSI tech 2004, p. 200

- [4] J.Kedzierski et al, IEDM 2002, proc. p247

- [5] SD.Suk et al. IEDM 2005 proc. p217

- [6] T. Shinada, S. Okamoto, T. Kobayashi, and I. Ohdomari, Nature **437**, 1128 (2005).

- [7] A. Batra et al. APL 91, 193502 (2007)

- [8] D.N. Jamieson et al. APL 86 202101 (2005)

- [9] H.Sellier et al. PRL **97** 206805 (2006)

[10] Hofheinz et al. European Physical Journal B54, 299, (2006).

[11] X. Jehl, et al. IEEE Trans. on Nanotechnology, 2,308 (2003).

[12] N. Agrait et al. Physics Reports 377 (2003) 81–279

- [13] Hofheinz et al APL.89, 143504, (2006).

- [14] C.Single et al. APL **78**, no 10 (2001)

[15] J.Gorman et al. PRL **95**, 090502 (2005)

[16] S.Pauliac-Vaujour et al. JVSTb vol 25, issue 6, pp2030-2003 (2007).

[17] V.Barral et al. IEDM 2007 proc., p61-64

[18] C.Jahan et al., Journal of Crystal Growth 280 (2005), 530-538

[19] M. Sanquer et al. Phys. Rev. B 61, 7269 (2000).

[20] M.A. H. Khalafalla et al. SSDM 2007 proc. p210-211.

[21] J. Park et al. Nature 417, 722 (2002)

[22] M.Vinet et al. IEEE Elec. Dev. Lett., 26, pp. 317-319, 2005

[23] J.Widiez et al. SOI conference 2004, proc.p185-186.

.Fig 5: Selenium doping profiles in Si layer. Optimal energy for 10 nm is 5 keV. For thicker film around 20 nm, 8 keV shows Rp in the middle of the film. Rp concentration is 1E18 at.cm-3, corresponding to 1 atom in a cube of 10\*10\*10 nm<sup>3</sup>.

Fig 8:20 nm line obtained thanks to Gaussian beam and NEB35 resist.

*.Fig 1 : Schematic view of an atomic orbital transistor and its potential profile along the wire a single dopant is localized in the channel*

Fig 3: Resonant drain current versus gate voltage in the subthreshold regime of a MOSFET. At low temperature the drain current is dominated by resonant tunnelling through centered dopants in wide [19], as in narrow [9] channels.

Fig 2 : Schematic view of an ultimate MOS-SET and its potential along the wire. The spacers will mask the island and barrier region during source/drain implantation [13] ( no channel and LDD implantation)

Fig 4 Periodic Coulomb Blockade Oscillation obtained at T=4.2K in a ultimate MOS-SET [13]

Fig 6: Phosphorus doping profiles in Si layer. Optimal energy for 10 nm is 1 keV. For thicker film around 20 nm, 3 keV shows Rp in the middle of the film. Rp concentration is 1E18 at.cm-3, corresponding to 1 atom in a cube of 10\*10\*10 nm<sup>3</sup>.

Fig 9: Two 50 nm lines with 40 nm spacing are obtained and enable very accurate coupling between dots

.Fig 7: Single dopant implantation through a mask in a thin film. The detection can either be performed via IBIC (large Vd bias) or by channel conductance variation.

Fig:10: Double Gate MOS transistor fabricated thanks to two gate successive lithographies. The targeted positions of the two gates were reached within a 10 nm accuracy.