# On the Reliability of and Self-Compensation in Strained Transistors

M. A. Alam and A. E. Islam

Purdue University, School of Electrical and Computer Engineering 465 Northwestern Avenue, West Lafayette, Indiana 47907, USA Phone: 765-494-5988 E-mail: alam@purdue.edu

### 1. Introduction

Since the early days of semiconductor industry, the counterbalancing requirements of performance and reliability have defined the specifications of each successive CMOS technology nodes. In recent years, it has been difficult to scale the gate oxide thickness below 1nm due to gate leakage and off-state power-dissipation. Therefore, there has been a broad consensus in the industry that performance of the transistors can only be improved by using strained substrates or high-k dielectrics or a combination thereof. Many groups have studied the implications of this change in the substrate and the gate oxide regarding the classical reliability issues involving Negative Bias Temperature Instability (NBTI), Positive Bias Temperature Instability (PBTI), Hot Carrier Degradation (HCI), Gate Dielectric Breakdown (TDDB), *etc*.

Of these degradation mechanisms, the influence of strained substrate on NBTI performance has been most interesting, because there has been no broad consensus regarding the matter [1-7]. Moreover, there have been experiments demonstrating the counterintuitive notion that strain engineering may actually lead to self-compensating transistors that can not only reduce/eliminate the influence of NBTI degradation [8], but also suppress the V<sub>T</sub> fluctuation arising from PBTI, distribution in gate oxide thickness as well as work-function differences. In this paper, we summarize our recent results regarding this topic.

#### 2. NBTI Considerations in Strained Transistors

The classical theory of NBTI degradation attributes the time-dependent shift in threshold voltage  $(\Delta V_T)$  to the depassivation of Si-H bonds at the Si/SiO<sub>2</sub> interface and subsequent diffusion of H/H<sub>2</sub> into the oxide/poly region [9]. Early ESR results by Stesmans et al. [10] suggested that the nature of defects does not change with strain, however, the number of bonds available for defect generation (N<sub>0</sub>) increases (decreases) with compressive (tensile) strain. This increase in N<sub>0</sub> may reflect in poorer NBTI performance for compressively strained PMOS transistors, currently being used in CMOS technology. Subsequent experiments showed that the activation and field acceleration remain unchanged with strain [1-3, 11], but the NBTI degradation is often found to *decrease* with compressive strain [2, 5, 11], contradicting the ESR-based previous suggestions.

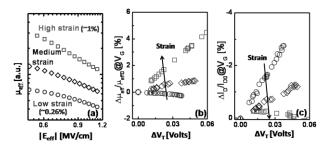

The puzzle of the NBTI degradation is resolved if one systematically explores the fundamentals of Si-H bond dissociation process via the R-D model (Fig. 1a), which suggest that the defects generated due to NBTI is given by:  $N_{IT} \sim [N_0 P_T exp(\gamma E_{ox})]^{2/3} t^n$ ; where,  $P_T$  is field-independent pre-factor for hole tunneling probability,  $\gamma$  is the field acceleration factor,  $E_{ox} \sim (V_G - V_T)$  is the oxide electric field, and  $n \sim 1/6$  is the field/temperature independent time exponent. Here, P<sub>T</sub> depends - among other things - on the effective barrier height for hole tunneling ( $\phi_{bh}$ ) [11]. Our measurements show - and this is the key to the puzzle that while  $\gamma$  does not change with strain, but at given E<sub>ox</sub> the pre-factor  $P_T$  decreases (increases) with compressive (tensile) strain (Fig. 1b,c). This presumption of P<sub>T</sub> reduction as being the source of NBTI improvement in compressively strained transistors is also supported by corresponding reduction in the leakage current (see [3, 11]), both of which are correlated via the increase in  $\varphi_{bh}$  (Fig. 1b). The interpretation of  $P_T$ -dictated change in  $\Delta V_T$  is also consistent with increased NBTI degradation with bi-axial tensile strain (Fig. 1c). Once again, the field acceleration factors remains essentially unchanged with biaxial strain [1, 3].

Fig. 1: (a) Universal view of Si-H bond dissociation under NBTI stress [9]. (b) Compressive strain decreases  $P_T$  due to increase in  $\phi_{bh}$  (inset) and thus decreases  $N_{IT}@E_{ox}$  [11]. (c) Tensile strain increases  $\phi_{bh}$  and  $P_T$  (inset) and thus increases  $N_{IT}@E_{ox}$ .

#### 3. On the Possibility of Degradation Free Transistors

It is well known that since  $I_{D,lin} \sim \mu C_{ox}(V_G-V_T)$ , the enhanced mobility ( $\mu$ ) of the strained channel would improve the drive-current (and therefore the performance) of a transistor. Less well appreciated is the implication of enhanced slope of the mobility-field ( $\mu$ -E<sub>eff</sub>) universal curve of the strained transistors in ameliorating the effects of charge trapping/trap-generation at the Si/SiO2 interface. It is easy to see that any change in  $I_{D,lin}$  must be due to changes in

mobility and the inversion charge, i.e.,  $\Delta I_{D,lin}/I_{D,lin0} = \Delta \mu/\mu$  - $\Delta V_T/(V_G-V_{T0})$ ; where the parameters with 0 subscripts indicate pre-NBTI stress values. When V<sub>T</sub> changes by NBTI or PBTI degradation, so does the  $\boldsymbol{\mu}.$  For strained transistors having steep µ-E<sub>eff</sub> characteristics, BTI degradation at constant  $V_G$  increases  $\mu$  (Fig. 2) [8]. This is because at constant  $V_G$ ,  $E_{eff}$  reduces due to BTI; and thus the increase in  $\mu$  due to  $E_{eff}$  reduction can compensate the decrease in  $\mu$  originating from additional coulomb scattering (mainly due to N<sub>IT</sub> generation [12] during NBTI). Historically, however, the slope of the  $\mu$ -E<sub>eff</sub> curve for unstrained transistors was so shallow that,  $\Delta \mu_{eff}$  was either negative or very small; hence could be neglected and researchers focused exclusively on  $\Delta V_T$  as the source of  $\Delta I_{D,\text{lin}}.$  With the enhanced slope of µ-E<sub>eff</sub> characteristics in strained transistors, however, the mobility enhancement may partially, if not completely (the effect is smaller in I<sub>D,sat</sub> compared to I<sub>D,lin</sub> [8]), cancel the effect of  $\Delta V_T$  to keep constant I<sub>D</sub>. In other words, after degradation fewer electrons move at faster velocity to keep the current the same. In sum, strain engineering can create a transistor that shows no I<sub>D</sub> degradation, although the transistor is certainly not defect-free. The importance of such degradation-free transistor for logic circuits is obvious, although the transistors in SRAM cell may not directly benefit from such degradation-free characteristics.

Fig. 2: (a) Presence of compressive strain increases the steepness of the  $\mu$ -E<sub>eff</sub> characteristics [8]. (b) Transistor with higher  $\mu$ -E<sub>eff</sub> steepness has more positive  $\Delta \mu_{eff} @V_G$  due to NBTI stress, compared to the one having smaller  $\mu$ -E<sub>eff</sub> steepness. (c) Positive  $\Delta \mu_{eff}$  $@V_G$  in transistors having higher  $\mu$ -E<sub>eff</sub> steepness compensates the effect from  $\Delta V_T$  and results negligible  $\Delta I_D$  [8].

## 4. Strain and Self-Compensation of V<sub>T</sub> Fluctuation

The SRAM transistors however would benefit from another aspect of strain-engineered self compensation that would improve the matching of the cells against thickness and work-function fluctuations. As is well known that the  $V_T$  of a transistor is given by –

$$V_{T} = \Phi_{MS} + \frac{T_{ox}}{\varepsilon_{ox}} \sqrt{4k_{B}T\varepsilon_{Si}N_{D}\ln\frac{N_{D}}{n_{i}}} + \frac{2k_{B}T}{q}\ln\frac{N_{D}}{n_{i}} + q\frac{\Delta N_{T}(t)}{C_{ox}}$$

(1)

where,  $\Phi_{MS}$  is the metal-substrate work-function difference, T<sub>ox</sub> is the dielectric thickness (referred to SiO<sub>2</sub>), and  $\Delta N_T(t)$ are concentration of charged defects (referred at the Si/SiO<sub>2</sub> interface). Once again, thicker oxides increase V<sub>T</sub>, but reduce E<sub>eff</sub>. As such, although the induced charge is reduced, the mobility is actually enhanced. Given an optimized strain-engineered channel, the two counterbalancing factors would keep  $I_D$  roughly the same independent of  $T_{ox}$ . It is easy to see that such self-compensation would apply to fluctuation in gate work-function as well. However,  $I_D$  fluctuation due to channel length variation (small for well designed DIBL-free transistors) and  $V_T$  fluctuation due to random-dopants (irrelevant for fully depleted structures) are not compensated and remain sources of  $I_D$  fluctuation.

An interesting consequence and external manifestation of the self-compensation between  $\mu$  and  $V_T$  is the flatness of the  $I_D$ - $V_G$  characteristics. Such flat characteristics may open up opportunities to eliminate guard-band voltages and reduce supply voltage (and power-dissipation) in the process. There are indications that various research groups have made substantial progress in this direction.

## 5. Conclusion

The importance of strain-engineering for high performance circuits is well known and broadly appreciated. In this paper, we highlight the additional opportunities of strain engineering in creating a technology that is inherently self-compensating against various reliability and  $V_T$ -fluctuation issues. The use of such degradation free technology would not only simplify IC design, but also help reduce the supply voltage (and power dissipation) by significantly curtailing the guard-band necessary to account for device-to-device parameter fluctuation.

### Acknowledgements

We gratefully acknowledge NCN for computational resources, BNC for experimental facilities, and TSMC, AMAT, NCN for financial support for this work.

### References

[1] J. R. Shih and K. Wu, in Int. Reliability Phys. Symp., p. 403 (2005).

[2] A. Shickova, B. Kaczer, P. Verheyen, G. Enernan, E. S. Andres, M. Jurczak, P. Absil, H. Maes and G. Groeseneken, *IEEE Elec. Dev. Lett.*, **28**, 242 (2007).

[3] T. Irisawa, T. Numata, E. Toyoda, N. Hirashita, T. Tezuka, N. Sugiyama and S. Takagi, *Symp. on VLSI Technology*, 36 (2007).

[4] H. S. Rhee, H. Lee, T. Ueno, D. S. Shin, S. H. Lee, Y. Kim, A. Samoilov, P.-O. Hansson, M. Kim, H. S. Kim and N.-I. Lee, in *Int. Elec. Dev. Meeting (IEDM)*, p. 692 (2005).

[5] G. Giusi, F. Crupi, E. Simoen, G. Eneman and M. Jurczak, *IEEE Trans. on Elec. Dev.*, **54**, 78 (2007).

[6] C. H. Liu and T. M. Pan, *IEEE Trans. on Elec. Dev.*, **54**, 1799 (2007).

[7] C. Y. Lu, H. C. Lin, Y. F. Chang and T. Y. Huang, *Jpn J Appl Phys 1*, **45**, 3064 (2006).

[8] A. E. Islam and M. A. Alam, Appl. Phys. Lett., 92 (173504) (2008).

[9] A. E. Islam, H. Kufluoglu, D. Varghese, S. Mahapatra and M. A. Alam, *IEEE Trans. on Elec. Dev.*, **54**, 2143 (2007).

[10] A. Stesmans, D. Pierreux, R. J. Jaccodine, M. T. Lin and T. J. Delph, *Appl. Phys. Lett.*, **82**, 3038 (2003).

[11] A. E. Islam, J. H. Lee, W. H. Wu, A. Oates and M. A. Alam, in *Int. Elec. Dev. Meeting (IEDM)*, p. 107 (2008).

[12] S. Takagi, A. Toriumi, M. Iwase and H. Tango, *IEEE Trans.* on Elec. Dev., **41**, 2357 (1994).