# Impact of adequate selection of channel direction on (001) and (110) wafer orientation for strained nanowire transistors

Aya Seike<sup>1</sup>, Hajime Takai<sup>1</sup>, Ikushin Tsuchida<sup>1</sup>, Junichi Masuda<sup>2</sup>, Daisuke Kosemura<sup>2</sup>, Atsushi Ogura<sup>2</sup>, Takanobu Watanabe<sup>1</sup> and Iwao Ohdomari<sup>1</sup>

<sup>1</sup>Waseda University, Faculty of Science and Engineering 3-4-1 Ohkubo, Shinjuku, Tokyo 169-8555, Japan Phone: +81-5286-1621 E-mail: seike@aoni.waseda.jp

<sup>2</sup>Meiji University, School of Science and Technology 1-1-1 Higashimita, Tama, Kawasaki, 214-8571, Japan

## 1. Introduction

Nanowire transistor, promising alternative for planar bulk MOSFETs, has been studied intensively to implement in ultra high-performance ULSI and SoC due to their strong immunity against SCE and high drivability.<sup>1-3</sup> Introduction of strain technology to nanowire yields additional mobility enhancement but with a limited and incomplete under-pinning by a validated science knowledge-base. Building the science knowledge of transporting mechanism of nanowire with influence of strain in formats that is consistent with technology growth is very significant for implementing nanowire in the next generation ULSI technology. We have studied electrical characterization of strained nanowire FETs (s-nwFETs) to demonstrate impact of i) wafer orientation dependence using (001) and (110) plane and ii) adequate channel directions for transconductance enhancement based on and to reveal the carrier transport mechanism in nwFETs.

# 2. Experiments

We used *p*-type SOI wafers, (001) and (110) planes as substrates. The fabrication process is described elsewhere.<sup>4,5</sup> Figure 1 shows (a) the top-view schematic of fabricated strained nanowire transistor (s-nwFET), (b) (c) layouts of

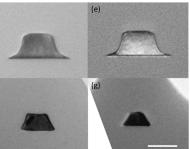

Fig. 1 Fabricated s-nwFET; (a) top view, (b) layout on (001) plane, (c) layout on (110) plane. Cross-sectional TEM images of each nanowire; (d) <100> direction on (110) plane, (e)  $<\sqrt{2}\sqrt{21}>$  direction on (110) plane, (f) <100> direction on (001) plane, and (g) <110> direction on (001) plane. Scale bar denotes 50nm.

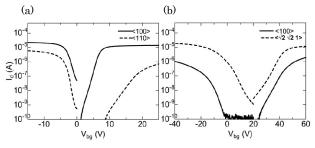

Fig. 2  $I_{ds}$ -V<sub>bg</sub> curves for (a) (001) plane and (b) (110) plane. Solid lines denote <100> direction for both plane, and dashed lines denotes <110> direction for (001) plane and < $\sqrt{2}\sqrt{21}$ > direction for (110) plane.

s-nwFETs, and (d) (e) (f) (g) the cross-sectional TEM images of each nanowire. Si nanowires are fabricated in (d) <100> direction on (110) plane, (e) < $\sqrt{2}\sqrt{21}$ > direction on (110) plane, (f) <100> direction on (001) plane and (g) <110> direction on (001) plane. Scale bar denotes 50nm. The channel lengths are 2, 3, and 5µm, and nanowire lithography width (W<sub>1</sub>) is 80~500nm.

## 3. Results and Discussion

I-V measurement is carried out for electrical characterization of s-nwFETs, with the backgate voltage ( $V_{bg}$ ) applied to the *p* substrate. Figure 2 shows I<sub>ds</sub>- $V_{bg}$  curves for both (001) and (110) planes. Subthreshold slopes for *n*-type and *p*-type <100> direction nwFETs are 3180mV/dec, 2860mV/dec on (001) plane, and 568mV/dec and 650mV/dec on (110) plane. Devices on (001) plane shows improved subthreshold slopes.

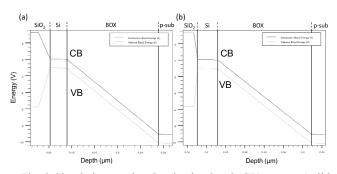

The conduction and valance band energy of s-nwFETs are evaluated by *T-CAD* tool, and the simulation results are shown in figure 3 for (a) (001) plane and (b) (110) plane. Device profiles are recreated from the cross-sectional TEM images as shown in fig.1.  $V_{bg}$  is set at 10V, and  $V_d$  is set at 0.1V. Band vending is consistent among both devices even the nanowire cross-sectional profiles are different (fig. 1). Electrical potentials are also calculated, and they are also consistent (not shown in this paper).

Transconductance  $(g_m)$ , the slope of  $I_{ds}$ - $V_{bg}$  curves in

Fig. 3 Simulation results. Conduction band (CB) energy (solid line) and valence band (VB) energy (gray line) against (a) (001) plane and (b) (110) plane s-nwFETs.

the linear region,  $g_m \equiv (\partial I_{ds}/\partial V_{bg}) = (W/L_g)(\epsilon/t_{OX})\mu V_{ds}$ , is normalized by W and  $t_{OX}$ , determined from the cross-sectional TEM images of nanowires (fig. 1) and the defined value of the gate length (L<sub>g</sub>) to give  $g_m^* = g_m (L_g/W) t_{OX} = \mu \epsilon V_{ds}$ .

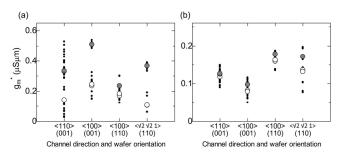

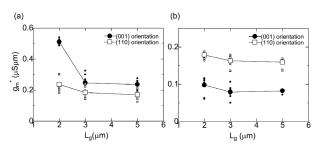

$g_m^* = g_m(L_g/W)t_{OX} = \mu \varepsilon V_{ds}$ . Figure 4 shows  $g_m^*$  for (a) *n*-type and (b) *p*-type s-nwFETs with channel direction and wafer orientation of <110> direction on (001), <100> direction on (001), <100> direction on (110) and < $\sqrt{2}\sqrt{21}$ > direction on (110). Solid circles denote raw data for each condition, gray circles denote  $g_m^*$  with  $L_g=2\mu m$ , and open circles denote  $g_m^*$  with  $L_g=3,5\mu m$ . For *n*-type, the device with <100> channel on (001) yields the highest  $g_m$  enhancement, and for *p*-type, that with <100> channel on (110) yields the highest enhancement.  $g_m^*$  with  $L_g=2\mu m$  shows the highest values in all conditions. This indicates the strong dependence of  $g_m^*$ on  $L_g$  since the  $g_m$  is normalized by  $L_g$  to yield  $g_m^*$ .

Figure 5 shows  $g_m^*$  for (a) *n*-type and (b) *p*-type <100> direction strained nwFETs. Solid circles denote  $g_m^*$  for (001) plane, and open squares denote  $g_m^*$  for (110) plane. Big solid circles and big open squares with solid lines denote average values for each condition. For *n*-type,  $g_m^*$  is enhanced in (001) plane compared to (110) plane. The average value of  $g_m^*$  for (001) plane at L<sub>g</sub>=2µm, for example, is improved by a factor of 2.2. This is due to the lighter effective mass of electron on (001) plane than (110) plane

Fig. 4  $g_m^*$  for (a) *n*-type and (b) *p*-type strained nwFETs. Closed circle denote  $g_m^*$  for each channel direction and wafer plane. Gray circles in bigger size denote the average values of  $g_m^*$  with L<sub>g</sub>=2µm, and open circle in bigger size denote the average values of  $g_m^*$  with L<sub>g</sub>=3,5µm

Fig. 5  $g_m^*$  for (a) *n*-type and (b) *p*-type <100> direction s-nwFETs. Circles denote (001) plane and squares denote (110) orientation. Bigger circles and squares with solid lines denote average values for each condition.

in <100> direction.<sup>7</sup> For *p*-type, on the contrary,  $g_m^*$  is enhanced in (110) plane compared to (001) plane. The average value of  $g_m^*$  for (110) at L<sub>g</sub>=2µm is enhanced by a factor of 1.8 compared to (001) plane. This is due the anisotropy of effective mass of holes.<sup>8</sup> Though  $g_m^*$  is normalized by L<sub>g</sub>, it has L<sub>g</sub> dependence. Fig. 5 clearly shows the dependence of  $g_m^*$  on L<sub>g</sub>. This enhancement may be due to less contribution of phonon scattering because the channel length is approaching to the average mean free path of phonon, which is 300nm at room temperature.<sup>9</sup>

### 4. Conclusions

Enhanced transconductance in s-nwFETs is demonstrated with adequate combination of channel direction and wafer plane.  $g_m^*$  for *n*-type s-nwFETs is enhanced by a factor of 2.2 with <100> direction channel on (001) plane, and that for *p*-type is enhanced by a factor of 1.8 with <100> direction channel on (110) plane. This is due to the lighter effective mass of carriers along the selected direction on the adequate wafer plane.

#### Acknowledgements

This work was supported by Grant for Special Research Projects of the Ministry of Education, Culture, Sports, Science and Technology, Japan, and "Ambient SoC Global COE Program of Waseda University" of the Ministry of Education, Culture, Sports, Science and Technology, Japan

#### References

- [1] J. Xiang et al, Nature, 441, 489 (2006)

- [2] S.D. Suk et al, IEDM, 891 (2007)

- [3] E-H Toh et al, IEDM, 195 (2007)

- [4] A. Seike et al, Appl. Phys. Lett. 91, 062108 (2007)

- [5] A. Seike et al, Appl. Phys. Lett. 91, 202117 (2007)

- [6] A. Seike et al, IEICE Tech. Rep., vol. 108, no. 80,

- SDM2008-48, pp. 35-39, June (2008) [7] T. Sato et al, Phys. Rev. B, **4**, 1950 (1971)

- [8] M. V. Fischeti et al, J. Appl. Phys., 94, 1079 (2003)

- [9] K. E. Yazdani, IEEE Int. Society Conference on Thermal Phenomena, 424 (2004)