## A 1.2V Operation 2.43 Times Higher Power Efficiency Adaptive Charge Pump Circuit with Optimized V<sub>TH</sub> at Each Pump Stage for Ferroelectric (Fe)-NAND Flash Memories

Shinji Noda<sup>1</sup>, Teruyoshi Hatanaka<sup>1</sup>, Mitsue Takahashi<sup>2</sup>, Shigeki Sakai<sup>2</sup> and Ken Takeuchi<sup>1</sup>

<sup>1</sup>University of Tokyo, Dept. of Electrical Engineering and Information Systems, Japan, E-mail: shinji-noda@lsi.t.u-tokyo.ac.jp <sup>2</sup>National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan

#### 1. Introduction

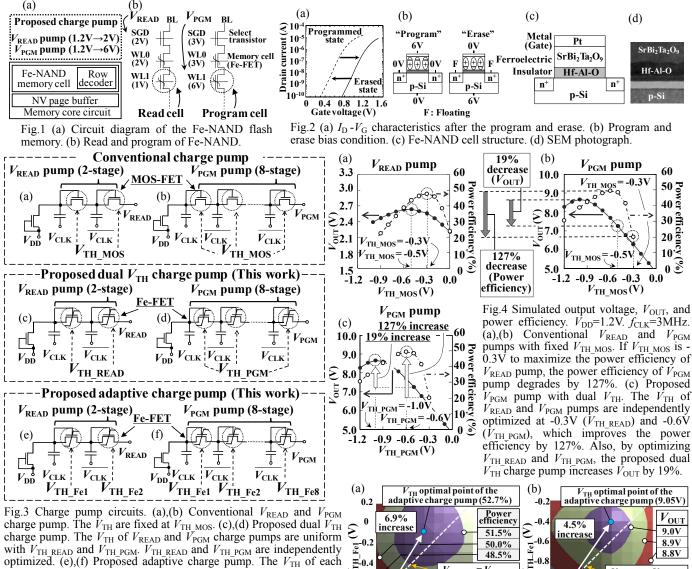

The Ferroelectric (Fe)-NAND flash memory device [1-3] and high-speed highly reliable memory circuits [4] were proposed to decrease the power consumption of data centers (Fig.1,2). Key benefits of Fe-NAND are 1) a high reliability where the program/erase cycles increases from  $10^4$  to  $10^8$  cycles and 2) a low voltage/power consumption where the program/erase voltage decreases from 20V of the floating-gate NAND to 6V. As the feature size decreases below 30nm, the inter bit-line capacitance drastically increases and the power consumption increases by 38% [5]. By decreasing the power supply,  $V_{DD}$ , from 3.3V to 1.2V, the power consumption of the memory core decreases by 87%. However, the power consumption of the conventional charge pump [6] to generate read/program/erase voltage triples [7]. To realize low voltage and low power Fe-NAND flash memories, this paper proposes an adaptive charge pump that increases the power efficiency and the output voltage by 143% and 25% without circuit area and process step penalty. 2. Problems of the Conventional Charge Pump

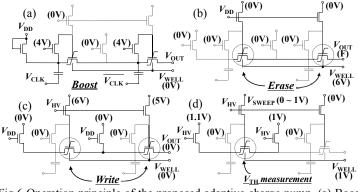

In the proposed 1.2V Fe-NAND flash memory,  $V_{\text{READ}}$  and  $V_{PGM}$  charge pump circuits generate a read voltage, 2V and a program voltage, 6V from V<sub>DD</sub>, 1.2V (Fig.1). Fig.3(a)(b) shows the conventional charge pump. The transistor  $V_{\rm TH}$  of all pump stages is fixed at  $V_{\text{TH}_{\text{MOS}}}$ . As shown in Fig.4(a),(b),  $V_{\text{TH}_{\text{MOS}}}$  has optimal values to maximize the power efficiency or the output voltage,  $V_{\text{OUT}}$ . If  $V_{\text{TH MOS}}$  is too high, the large  $V_{\text{TH}}$  loss of MOS diodes decreases the power efficiency and  $V_{OUT}$ . On the other hand, if  $V_{\text{TH MOS}}$  is too low, the transistor does not function as a rectifier and the output current flows backward from the output to the input. The optimal  $V_{\rm TH MOS}$  of the conventional  $V_{\rm PGM}$ charge pump to maximize the power efficiency is -0.6V (Fig.4(b)) that is lower than the conventional  $V_{\text{READ}}$  charge pump, -0.3V (Fig.4(a)). In the  $V_{PGM}$  charge pump as  $V_{OUT}$  is higher than that of the  $V_{\text{READ}}$  charge pump, the  $V_{\text{TH}}$  increases due to the larger body effect and thus the optimal  $V_{\rm TH_MOS}$ becomes lower. If  $V_{\text{TH}_{MOS}}$  is -0.3V to maximize the power efficiency of the  $V_{\text{READ}}$  charge pump, the power efficiency of the  $V_{PGM}$  charge pump is 127% smaller than the optimal value with  $V_{\text{TH}_{\text{MOS}}}$ =-0.6V. Similarly, if  $V_{\text{TH}_{\text{MOS}}}$  is -0.5V to maximize  $V_{\text{OUT}}$  of the  $V_{\text{READ}}$  charge pump,  $V_{\text{OUT}}$  of the  $V_{\text{PGM}}$  charge pump decreases by 19% from its maximum value with  $V_{\text{TH MOS}}$ =-1.0V. 3. Proposed Dual V<sub>TH</sub> Charge Pump Circuit

# To increase the power efficiency and $V_{OUT}$ of the $V_{PGM}$ charge

pump, this paper proposes a dual  $V_{\text{TH}}$  charge pump (Fig.3(c)(d)). Ferroelectric (Fe)-FETs are used as diodes to change the  $V_{\rm TH}$  by the program/erase. There is no area or process overhead as Fe-FETs in the charge pump are fabricated with the same process steps as memory cells. The  $V_{\text{TH}}$  of  $V_{\text{READ}}$  and  $V_{\text{PGM}}$  charge pumps are uniform with  $V_{\text{TH}_{\text{READ}}}$  and  $V_{\text{TH}_{\text{PGM}}}$ . By changing the  $V_{\text{TH}}$  of Fe-FETs,  $V_{\text{TH}_{\text{READ}}}$  and  $V_{\text{TH}_{\text{PGM}}}$  are independently optimized at -0.3V (Fig.4(a)) and -0.6V (Fig.4(c)). As a result, the power efficiency of the  $V_{PGM}$  charge pump increases by 127%. By selecting  $V_{\text{TH READ}}$  and  $V_{\text{TH PGM}}$  as -0.5V and -1.0V,  $V_{\text{OUT}}$  of both  $V_{\text{READ}}$  and  $V_{\text{PGM}}$  charge pumps are also maximized.  $V_{\text{OUT}}$  of the  $V_{\text{PGM}}$  charge pump increases by 19%.

#### 4. Proposed Adaptive Charge Pump Circuit

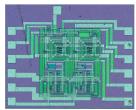

To further increase the power efficiency and  $V_{\text{OUT}}$ , this paper also proposes an adaptive charge pump (Fig.3(e)(f)). The  $V_{\text{TH}}$  of both  $V_{\text{READ}}$  and  $V_{\text{PGM}}$  charge pumps are different with  $V_{\text{TH Fel}}$ .  $_{2...8}$  at each pump stage.  $V_{\text{TH}_{\text{Fel}}, 2...8}$  has a relationship of  $V_{\text{TH}_{\text{Fel}}}$  $> V_{\text{TH Fe2}} > ... > V_{\text{TH Fe8}}$  because at a pump stage closer to the output the source voltage increases and the  $V_{\rm TH}$  shift due to the body effect also increases. Fig.5 shows the simulated power efficiency and  $V_{\text{OUT}}$  of the adaptive charge pump. Compared with the dual  $V_{\rm TH}$  charge pump, the adaptive charge pump increases the power efficiency and  $V_{\text{OUT}}$  by 6.9% and 4.5%. Table 1 summarizes the conventional and proposed charge pumps. The adaptive charge pump is most power efficient and has the highest  $V_{\text{OUT}}$  as the  $V_{\text{TH}}$  at each pump stage is best optimized. Compared with the conventional charge pump, the power efficiency and  $V_{OUT}$  increase by 143% and 25%.

#### 5. Measurement Results

Fig.6 shows the detailed operation of the proposed adaptive charge pump. Fig.6(a) shows the boosting to generate  $V_{\text{READ}}$ , 2V and  $V_{PGM}$ , 6V from  $V_{DD}$ . During the boosting, the well of Fe-FETs is grounded so that the  $V_{\rm TH}$  of Fe-FETs is fixed at the optimal values. Erase, program and the  $V_{\rm TH}$  measurement (Fig.6(b),(c),(d)) are performed only once during the testing to adjust the  $V_{\text{TH}}$ . A high voltage such as program/erase voltage biased to Fe-FETs inputs from the testing equipment. As the first step of the  $V_{\rm TH}$  adjustment, the erase is performed by biasing the well of Fe-FET to 6V (Fig.6(b)).  $V_{\text{TH}_{\text{Fel}, 2...8}}$  all increases to a positive value. Next, the program voltage, 5~6V, is applied to the gate of Fe-FETs and  $V_{\text{TH}_{\text{Fel}, 2...8}}$  decreases (Fig.6(c)). In the  $V_{\rm TH}$  measurement, a negative  $V_{\rm TH}$  is measured by applying 1V to the source, 1.1V to the drain and 0~1V to the gate (Fig.6(d)). Program and the  $V_{\rm TH}$  measurement are repeated until the  $V_{\rm TH}$  at each pump stage reaches the optimal value.

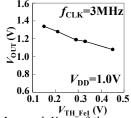

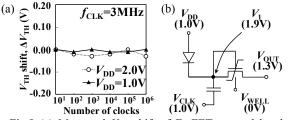

Fig.7 shows a microphotograph of the proposed circuit. Fig.8 shows measured  $V_{\rm OUT}$  versus the  $V_{\rm TH}$ . As the  $V_{\rm TH}$  decreases,  $V_{\rm OUT}$  increases, which is consistent with simulated results. Fig.9 (a) shows the measured  $V_{\rm TH}$  shift of Fe-FETs due to the disturb during the boosting. Fig.9 (b) describes the disturb of Fe-FETs. While a voltage higher than  $V_{DD}$  is biased to Fe-FETs, the  $V_{TH}$ shift of Fe-FET is negligibly small irrespective of the operation cycles and  $V_{\rm DD}$  and a highly reliable operation is realized.

#### 6. Conclusion

A 1.2V adaptive charge pump for low power Fe-NAND is proposed and experimentally demonstrated. The chip is fabricated with the CMOS compatible Fe-FET process [1]. By using Fe-FETs as diodes in the charge pump and optimizing the  $V_{\rm TH}$  at each pump stage, the power efficiency and  $V_{\rm OUT}$  increase by 143% and 25% without circuit area and process step penalty. Fe-FETs in the proposed circuit are immune to the disturb and a highly reliable operation is experimentally demonstrated.

### Acknowledgements

The authors appreciate K. Miyaji, R. Yajima and S. Tanakamaru for their support. This work is partially supported by NEDO. References

- [1] S. Sakai et al., NVSMW, pp.124-125 (2008).

- [2] T. Hatanaka et al., ESSDERC (2009).

- [3] R. Yajima et al., SSDM (2009).

- [4] T. Hatanaka et al., Symp. VLSI Circuits, pp.124-125 (2009).

- [5] K. Takeuchi, Symp. VLSI Circuits, pp.124-125 (2008).

- [6] J. F. Dickson, J.SSC, pp.374-378 (1976).

- [7] K. Ishida et al., ISSCC, pp.238-239 (2009).

-0.6

-0.

-0.8 -0.6

optimized. (e),(f) Proposed adaptive charge pump. The  $V_{\text{TH}}$  of each transistor in  $V_{\text{READ}}$  and  $V_{\text{PGM}}$  charge pumps are different with  $V_{\text{TH}_{\text{FE1}}}$ , 2...8 and are best optimized to maximize the power efficiency of both  $V_{\text{READ}}$  and  $V_{\text{PGM}}$  charge pumps.

Fig.6 Operation principle of the proposed adaptive charge pump. (a) Boost. (b) Erase. (c) Program. (d)  $V_{\rm TH}$  measurement. (b),(c),(d) are performed only once during the testing to adjust the  $V_{\rm TH}$ . High voltage such as write/erase voltage input from the testing equipment.

proposed adaptive V<sub>READ</sub> pump.

Fig.7 Chip microphotograph of the Fig.8 Measured  $V_{OUT}$  of the proposed adaptive charge pump. By reducing the V<sub>TH</sub>, V<sub>OUT</sub> increases.

$V_{TH_Fe2}(V)$ V<sub>TH\_Fe2</sub> (V) Fig.5 Simulated power efficiency and  $V_{OUT}$  of the proposed adaptive charge pump. The  $V_{\rm TH}$  of each transistor is individually optimized. (a),(b) Power efficiency and  $V_{OUT}$  of  $V_{PGM}$  pump vs.  $V_{TH Fe1}$  and  $V_{\text{TH}_{\text{Fe2}}}$ . Compared with the proposed dual  $\hat{V}_{\text{TH}}$  charge pump, the power efficiency and  $V_{\text{OUT}}$  increase by 6.9% and 4.5%.

-1.0

$V_{\text{TH Fe1}} = V_{\text{TH Fe2}}$

V<sub>TH</sub> optimal point of the dual V<sub>TH</sub> charge pump (8.66V)

$V_{\text{TH}_{\text{Fe1}}} = V_{\text{TH}_{\text{Fe2}}}$

V<sub>TH</sub> optimal point of the dual V<sub>TH</sub> charge pump (49.3%)

-0.4 -0.2 0 0.2

Table 1 Comparison of the conventional and the proposed charge pump circuits.  $V_{OUT}$  is the output voltage.

|                        | Conventional | Proposed dual V <sub>TH</sub> | Proposed adaptive |

|------------------------|--------------|-------------------------------|-------------------|

|                        | charge pump  | charge pump                   | charge pump       |

| Power                  | 21.7         | 49.3                          | 52.7              |

| efficiency (%)         | (x1.00)      | (x2.27)                       | (x2.43)           |

| V <sub>OUT</sub> (V)   | 7.26         | 8.66                          | 9.05              |

|                        | (x1.00)      | (x1.19)                       | (x1.25)           |

| Circuit area<br>(a.u.) | 1            | 1                             | 1                 |

Fig.9 (a) Measured  $V_{\rm TH}$  shift of Fe-FETs caused by the disturb during the boosting. (b) Bias condition of the disturb. Since the measured  $V_{\rm TH}$  shift is negligibly small irrespective of the operation cycles and the power supply,  $V_{\rm DD}$ , the proposed circuit is immune to the disturb.