# Experimental Analysis of Anisotropic Impact Ionization in (110) Surface pMOSFETs

Ting-Kuo Kang<sup>1\*</sup>, Chia-Ming Kuo<sup>1</sup>, Chi-Lin Huang<sup>1</sup>, Hsin-Liang Liu<sup>1</sup>, Chung-Yi Wu<sup>1</sup>, San-Lein Wu<sup>1</sup>, Yao-Tsung Huang<sup>2</sup>,

Shoou-Jinn Chang<sup>2</sup>

<sup>1</sup>Department of Electronic Engineering, Cheng Shiu University, Kaohsiung County 833, Taiwan R.O.C Tel: 886-7-7310606 ext. 3215, Fax: 886-7-7331758, \*E-mail: tkkang@csu.edu.tw

<sup>2</sup>Institute of Microelectronics and Department of Electrical Engineering, National Cheng Kung University

## 1. Introduction

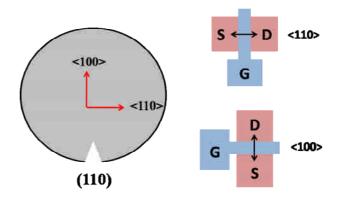

The use of (110) surface orientation has attracted considerable attention for boosting pMOSFETs performance owing to higher hole mobility [1]. However, the (110) surface pMOSFETs have to be located on the same direction, i.e. the layout limitation, due to the anisotropic hole mobility on the (110) surface [2]. This is because the hole mobility shows to be a significant degradation when the channel direction is rotated from <110> to <100> direction on (110) surface pMOSFETs, as shown in Fig. 1. In addition, it has been reported that the substrate current caused by the impact ionization process is dependent on the current flow direction and the impact ionization efficiency (IIE) also appears to be anisotropic [3],[4]. To our knowledge, the physical mechanism of anisotropic IIE in (110) surface pMOSFETs has not yet been fully understood.

The aim of this paper is to focus on the experimental analysis of anisotropic IIE in (110) surface pMOSFETs. From the relationship between the IIE and the electric field in the pinch-off region, the present understanding of anisotropic IIE can be substantially improved.

#### 2. Experimental

The pMOSFETs used in this study were fabricated on a (110) surface Si substrate based on a 90nm CMOS technology. To focus on the effect of the surface orientation on the drain current  $(I_D)$  and the IIE, we have to minimize CMOS process-induced strain into the device channel. For example, the space of the gate edge to shallow trench isolation sidewall is chosen to be 5 um. For comparison, a control-Si device was also fabricated on a (100) surface Si substrate by using the same CMOS process. Here, two gate dimensions (W/L) of 10um/1um and 10um/0.1um are termed as a long-channel and a short-channel pMOSFETs, respectively.

#### 3. Results and Discussion

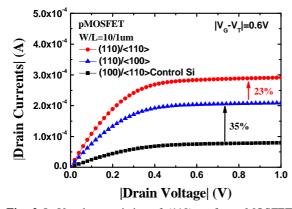

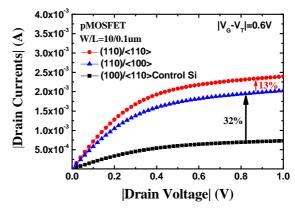

Figure 2 shows the (110) surface orientation induced  $I_D$  enhancement ratio of 58% for <110> and 35% for <100> direction on the long-channel pMOSFETs relative to the (100) surface control-Si. For the short-channel (110) surface pMOSFETs, two  $I_D$  enhancement ratios of 45% for <110> and 32% for <100> direction are shown in Fig. 3. It has been noted that the difference in  $I_D$  enhancement between the <110> and the <100> direction on (110) surface pMOSFETs becomes smaller with reduced the channel length. This result of  $I_D$  enhancement appears to be similar to the value reported in Ref. [5],[6]. In addition, through the source terminal floating technique [7], the excess diode leakage current even at the large drain voltage (V<sub>D</sub>) has markedly smaller effect on the substrate

current (I<sub>B</sub>) caused by impact ionization process (not shown here). Thus, the impact ionization multiplication coefficient M-1 as a function of V<sub>D</sub> is approximately the ratio of the I<sub>B</sub> to I<sub>D</sub>, that is, M-1(V<sub>D</sub>) $\approx$ I<sub>B</sub>/I<sub>D</sub>. Due to the I<sub>B</sub> associated with the maximum electric field E<sub>m</sub> near the drain, it is necessary to translate M-1(V<sub>D</sub>) into M-1(E<sub>m</sub>). According to the lucky electron model [8], M-1(E<sub>m</sub>) is described as

$$M-1 \approx \frac{I_B}{I_D} \propto E_m \exp\left(\frac{-\varphi_i}{q\lambda E_m}\right), \tag{1}$$

where  $\phi_i$  is the threshold energy for impact ionization and  $\lambda$  is the mean free path. Moreover,  $E_m$  can be expressed as

$$E_m = \frac{V_D - V_{dsat}}{l},\tag{2}$$

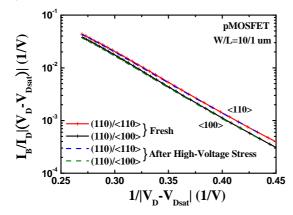

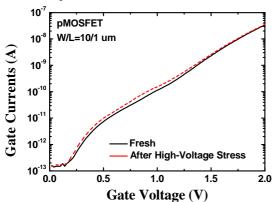

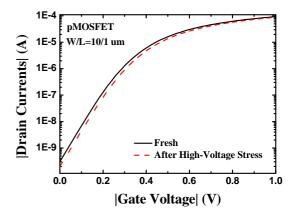

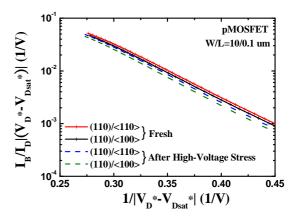

where  $V_{dsat}$  is the voltage at the pinch-off point and l is the effective pinch-off length. Em in Eq. (2) can be indirectly assessed through V<sub>D</sub>-V<sub>dsat</sub>. As predicted by Eqs. (1) and (2), the slope of the  $ln[I_B/I_D(V_D\text{-}V_{dsat})]$  versus  $1/(V_D\text{-}V_{dsat})$  plot is represented by  $-\phi_i l/\lambda$ . To differentiate between the contribution of these components  $(l, \lambda, and \varphi_i)$  to the IIE, a comparison of the slope change between the <110> and <100>directions on (110) surface pMOSFETs is made, as shown in Fig. 4. First, the l contribution to the IIE measured on the same (110) surface pMOSFETs with the long channel L of 1um is reasonably assumed to be negligible. Then, a constant high gate voltage of 3.2V is adopted to stress the gate oxide, with source, drain, and substrate tied to ground. The subthreshold characteristics and the low-voltage tunneling current show an increase in the SiO<sub>2</sub>/Si interface traps density, as shown in Fig. 5 and Fig. 6, and provide another condition for the modulation of the mean free path,  $\lambda$ . Relative to fresh device, the slope of a high-voltage stressing device appears to be consistent as shown in Fig. 4, implying that the surface orientation dependence of IIE can be attributed to the anisotropic threshold energy,  $\varphi_i$ . Similarly, the slope plot is made for the short-channel (110) pMOSFETs taking into account the series resistance of drain region (V<sub>D</sub>\*=V<sub>D</sub>-I<sub>D</sub>R<sub>D</sub>; V<sub>dsat</sub>\*=V<sub>dsat</sub>-I<sub>D</sub>R<sub>D</sub>), as shown in Fig. 7. Finally, the difference in slope change between <110> and <100> directions becomes smaller as decreasing the channel length, and the slope of a high-voltage stressing device appears to be inconsistent with that of fresh device. This result could be explained by the cause of non-stationary transport [9].

#### 4. Conclusions

Experimental analysis of anisotropic IIE in (110) surface pMOSFETs has been presented. From the relationship between the IIE and the  $E_m$ , the surface orientation dependence of IIE can be reasonably attributed to the anisotropic threshold energy,

$\varphi_i$ , regardless of the change of the mean free path,  $\lambda$ . As for the short-channel (110) surface pMOSFETs, the anisotropic IIE becomes smaller and it could be explained by the cause of non-stationary transport.

### Reference

- [1] M. Yang et al., IEEE T-ED, (2006) p.965.

- [2] M. Fischetti et al., J. Appl. Phys., (2003) p.1079.

- [3] N. Sano et al., Phys. Rev. B, (1990) p.12122.

- [4] S. Takagi et al., Semicond. Sci. Technol., (1992) p.601.

- [5] H. Nakamura et al., Jpn. J. Appl. Phys., (2004) p.1723.

- [6] F. M. Bufler et al., IEEE EDL, (2008) p.369.

- [7] T. K. Kang et al., Jpn. J. Appl. Phys., (2008) p.2664.

- [8] T. Y. Chen et al., IEEE EDL, (1984) p.505.

- [9] S. Takagi and A. Toriumi, IEDM Tech. Dig., (1992) p.711.

long channel (L=1um) relative to control-Si device.

<100> direction on a long-channel (110) surface pMOSFETs. The pMOSFETs before and after the high-voltage stress. result of pMOSFETs undergoing the high-voltage stress is also shown for comparison.

Fig. 6 Gate currents of a long-channel (110) surface pMOSFETs measured in accumulation region before and after the high-voltage stress.

Fig. 1 Schematic illustration of (110) surface pMOSFETs with two channel directions, i.e. <110> and <100>.

Fig. 2  $I_D$ -V<sub>D</sub> characteristics of (110) surface pMOSFETs with a Fig. 3  $I_D$ -V<sub>D</sub> characteristics of (110) surface pMOSFETs with a short channel (L=0.1um) relative to control-Si device.

Fig. 4  $1/|V_D-V_{dsat}|$  dependence of  $I_B/I_D$   $|V_D-V_{dsat}|$  for <110> and Fig. 5 Subthreshold characteristics of a long-channel (110) surface

Fig. 7  $1/|V_D\text{-}V_{dsat}|$  dependence of  $I_B/I_D\ |V_D\text{-}V_{dsat}|$  for <110> and <100> direction on a short-channel (110) surface pMOSFETs. The result of pMOSFETs undergoing the high-voltage stress is also shown for comparison.