# Electrical Characteristics of Engineered ZrO<sub>2</sub>/SiO<sub>2</sub> Tunnel Barrier with a High-k HfO<sub>2</sub> Trapping Layer for Non-Volatile Memory

Hee-Wook You<sup>1</sup>, Goon-Ho Park<sup>1</sup>, Jong-Wan Jung<sup>2</sup> and Won-Ju Cho<sup>1</sup>

<sup>1</sup>Department of Electronic Materials Engineering, Kwangwoon University, Seoul 139-701, Korea

<sup>2</sup>Department of Nano Science and Technology, Sejong University, Seoul 143-747, Korea *Phone:* +82-2-940-5163, *E-mail: chowj@kw.ac.kr*

### 1. Introduction

The SONOS-type memory device is very attractive candidates to realize the continuity of vertical scaling on flash memory [1]. However, the SONOS has fundamental problems in the trade-off between erase speed and data retention. Recently, Charge trap flash (CTF) memory devices based on tunnel barrier engineering (TBE) have received considerable attention due to many advantages such as fast programming, good retention, low power operation, high density integration and good reliability. Moreover, further improving of programming/erasing (P/E) characteristics can be achieved by using high-k materials [2], [3].

In this paper, the nonvolatile memory capacitor devices composed of engineered  $ZrO_2/SiO_2$  (ZO) tunnel barrier and HfO<sub>2</sub> trapping layer were fabricated. The electrical characteristics were compared with a conventional single SiO<sub>2</sub> tunnel barrier.

## 2. Experimental

TiN/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/ZrO<sub>2</sub>/SiO<sub>2</sub>/Si (MAHZOS) memory capacitor cell, which composed of 8 nm HfO<sub>2</sub> charge trapping layer and 20 nm Al<sub>2</sub>O<sub>3</sub> blocking oxide layer was fabricated by using atomic layer deposition (ALD) system at 300 °C. After formation of thin ZO tunnel barrier, the forming gas annealing (FGA) process was carried out at 250 °C, 300 °C, and 450 °C in 2 % diluted H<sub>2</sub>/N<sub>2</sub> ambient, respectively. Finally, control sample of single SiO<sub>2</sub> (5.1 nm) tunnel barrier (MAHOS) were fabricated with same process.

#### 3. Results and discussions

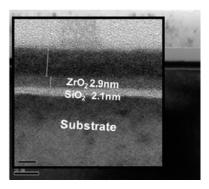

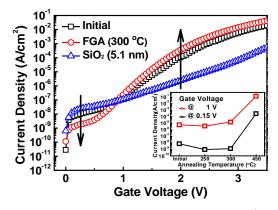

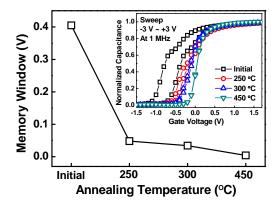

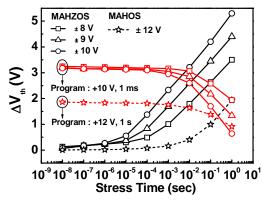

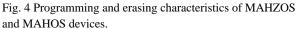

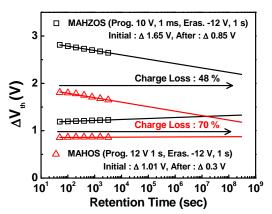

Fig. 1 shows the TEM image of  $ZrO_2/SiO_2$  layers on Si substrate. The thickness of deposited  $ZrO_2$  and  $SiO_2$ films were 2.9 nm and 2.1 nm, respectively. Fig. 2 shows the tunneling current characteristics of MZOS capacitors. The 300 °C annealed sample revealed a lower leakage current at 0.15 V and a higher tunneling current at 1 V than the initial state. Moreover, these characteristics were superior to single SiO<sub>2</sub> film with the same physical oxide thickness (POT). However, the current significantly increased again at 450 °C [inset fig.2]. Fig. 3 shows charge trapping characteristics of ZO tunnel barrier. The memory window  $(\Delta V_{th})$  decreased with increasing FGA temperature. Especially, there is no charge trapping effect  $(\Delta V_{th} 0.004 \text{ V})$  at 450 °C. However, a leakage current significantly increased at this temperature. Meanwhile, a hump in CV curves due to the poor interface was observed from the initial state and FGA at 250 °C [inset fig.3]. From these results, the effective temperature of FGA process was 300 °C. Fig. 4 shows the P/E characteristics of the MAHZOS memory capacitor under  $\pm 8 \text{ V}, \pm 9 \text{ and } \pm 10 \text{ V}$ gate voltage. The MAHZOS memory capacitor has superior programming characteristics than that of the MAHOS memory capacitors. Especially, after programming at +10 V, 1 ms condition, the higher erasing speed was achieved by using the ZO tunnel barrier. These results are attributable to the enhanced tunneling sensitivity of engineered tunnel barrier. Fig. 5 shows the data retention characteristics of the MAHZOS and MAHOS memory capacitors. The charge loss was 48 % and 70 % for MAHZOS and MAHOS, respectively after 10 years. Fig. 6 shows the data endurance characteristics of the MAHZOS and MAHOS memory capacitor. The MAHOZOS has no significant window narrowing after  $10^4$  P/E cycles. While memory window of the MAHOS was reduced with P/E cycle from 1.03 V to 0.34 V. The reason for the better endurance characteristics of the MAHZOS after 10 years is an enhancement of erasing property from engineered tunnel barrier.

## 4. Conclusions

We fabricated the MAHZOS and MAHOS memory capacitors and demonstrated their electrical characteristics. The engineered ZO tunnel barrier has larger field sensitivity than that of single SiO<sub>2</sub> layer. It contributed to the higher programming and erasing speed of HfO2 CTF memory devices. Also these features led to enhance the retention and endurance characteristics. Moreover, further improvement of tunneling sensitivity was obtained by using FGA process at 300 °C in H<sub>2</sub>  $(2\%)/N_2$  ambient. Therefore, the engineered tunnel barrier with ZO stacks were useful structure and the optimized heat process for the ZO tunnel barrier would be effective method for high-integrated non-volatile memory applications.

# Acknowledgements

This work was supported by the National Program for 0.1-Terabit Non-Volatile Memory Device development, sponsored by the Korean Ministry of Knowledge Economy.

#### References

- [1] J. K. Bu et al. Solid State Electron, vol. 45 (2001) 113.

- [2] Hang-Ting Lue et al. IEDM Tech. Dig. 5-7 (2005) 547.

- [3] Wei Chen et al. *Applied Physics Letters*. Vol. 91 (2007) 022908.

Fig. 1 TEM image of SiO<sub>2</sub>/ZrO<sub>2</sub> layer on Si substrate.

Fig. 2 J-V curve of MZOS capacitors at FGA 300 °C. Inset is tunneling current of MZOS capacitors versus FGA temperature.

Fig. 3 Charge trapping characteristics of MZOS capacitors as a function of FGA temperature. Inset is hysteresis curves measured at 1 MHz and  $\pm 3$  V sweep.

Fig. 5 Retention characteristics of MAHZOS and MAHOS devices at room temperature.

Fig. 6 P/E cycling endurance of the MAHZOS and MAHOS devices.