# Low Leakage AlGaN/GaN HEMTs with a High On/Off Current Ratio

Yu-Syuan Lin, Yi-Wei Lian, Shawn S.H. Hsu, and Ting-Chi Lee<sup>1</sup>

Institute of Electronics Engineering, National Tsing Hua University, Hsin-Chu, Taiwan <sup>1</sup>Department of Electronics Engineering, National Chiao Tung University, Hsin-Chu, Taiwan Phone: +886-3-5731278, E-mail: shhsu@ee.nthu.edu.tw

## 1. Introduction

High performance AlGaN/GaN high electron mobility transistors (HEMTs) have been successfully demonstrated for high power applications in recent years. However, the relatively high Schottky gate leakage current is still a critical issue, which causes an additional noise source [1], collapse effect [2], and device reliability problems [3]. For power electronic applications, a large leakage current also causes additional off-state loss in the power supply and reduces the efficiency of the system.

The leakage sources of HEMTs may originate from surface charge, process induced damage, and bulk/buffer related traps. Several approaches have been adopted to solve the problem. The most straightforward approach is probably the use of an additional gate dielectric to block the leakage current path [4]-[5]. Using the fluoride plasma was also suggested to reduce the leakage current [6]. In this work, we propose a filled-oxide structure to reduce the leakage current, in which the mesa area is fully surrounded by Silicon dioxide. By this approach, the traps around the mesa edge can be alleviated and the gate metal contact across the damaged mesa area can be prevented. In addition, the post gate annealing under an N<sub>2</sub>/H<sub>2</sub> mixture ambient is also used to fill up the traps generated during the mesa etching process. A leakage current as low as  $10^{-9}$ A/mm is obtained and an on/off current ratio up to  $10^{8}$  is demonstrated in this work.

#### 2. Device Design and Fabrication

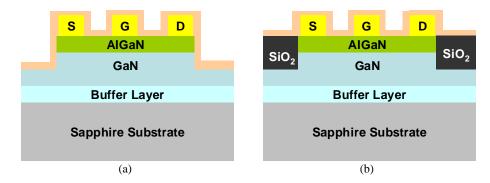

The device structure was grown on a c-plane sapphire substrate by metal-organic chemical vapor deposition (MOCVD). The epitaxial structure consisted of a GaN buffer layer, a 3-µm undoped GaN layer, a 3-nm undoped AlGaN layer, a 20-nm n-doped Al-GaN barrier layer, and then followed by a 5-nm undoped AlGaN cap layer. The Al mole fraction in the AlGaN layer was 0.25. The source/drain ohmic contacts were first formed with Ti/Al/Ti/Au (20nm/150nm/45nm/55nm) by rapid thermal annealing at 800 °C for 30 seconds in a N2 ambient. After the S/D ohmic contact formation, device isolation was achieved by dry etching using Cl<sub>2</sub>/Ar gas mixture and the etching depth is about 300 nm. For the filled-oxide structure, a 400 nm-thick e-beam oxide layer was filled around the device active region by lift-off process. Note that the conventional mesa isolation structure without the filled-oxide step is also fabricated for comparison. After the isolation process, the Ni/Au contact (20nm/300nm) was deposited to form the Schottky gate by lift-off process. Following the Schottky gate formation, both samples were annealed at 350°C for 60 seconds in N<sub>2</sub>/H<sub>2</sub> ambient for post-gate annealing. A PECVD silicon nitride/silicon dioxide layer of 0.4µm/0.8µm was then deposited for surface passivation. Finally, the pads were opened by RIE using a CHF<sub>3</sub>/O<sub>2</sub> mixture. The gate length  $L_{g}$ , the gate to drain spacing  $L_{gd}$ , and the gate to source spacing  $L_{gs}$  are all 2 µm and the overall widths of both devices are 50 µm. The cross sections of the traditional mesa isolation structure, and the proposed filled-oxide isolation structure are shown in Fig. 1(a) and 1(b), respectively.

### 3. Results and Discussion

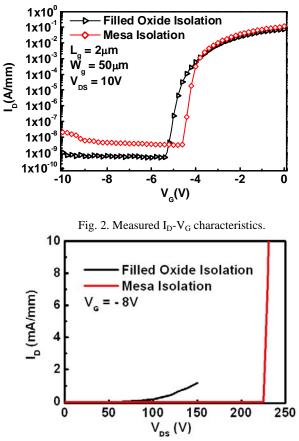

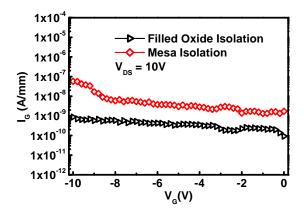

An Excellent on/off current ratio was achieved for each device in this work. Fig.2 compares the ID-VG curves of both the conventional and the filled-oxide devices. The on/off ratios of the mesa-isolated and filled-oxide-isolated devices with post-gate annealing are  $5 \times 10^6$ , and  $1.2 \times 10^8$ , respectively, which are greatly improved compared with that of the traditional mesa-type devices without the forming gas treatment (typical on/off ratio of  $10^3 \sim 10^5$ ) [7]. The results also show excellent pinch off characteristics in this work. The off-state drain leakage currents shown in Fig. 2 are smaller than 10<sup>-7</sup> A/mm and 10<sup>-9</sup> A/mm, respectively (typical off-state  $I_{\rm D}$  is  $10^{-4} \sim 10^{-6}$  A/mm for traditional structure). The gate leakage characteristics were also measured as shown in Fig. 3, which is smaller than 10<sup>-7</sup>A/mm for the mesa isolation and 10<sup>-9</sup>A/mm for the filled-oxide isolation structures, respectively. Compared with previous studies [7], the gate leakage is much smaller and is even comparable with the device using the MOS-HEMT structure [8]. The probable reason is that the H<sup>+</sup> introduced from the post-annealing can fill up the surface states/traps due to the etching process damage. Fig. 4 shows the measured breakdown voltage of both devices. The off-state drain-to-source breakdown voltage of GaN HEMT with mesa isolated structure is up to 220 V, while the breakdown voltage of GaN HEMT with filled-oxide isolation method is only 130 V (defined as  $I_{off} = 1 \text{mA/mm}$ ). The main reason may be attributed to the relative poor quality of e-beam oxide. This point is confirmed testing breakdown voltage of a vertical bv the metal-insulator-metal (MIM) diode with 0.4µm-thick e-beam oxide. The measured breakdown voltage of the MIM diode is only 60 V and the calculated critical field is only ~ 1.5 MV/cm, which is much lower than the expected value of 5 MV/cm. The problem of poor-quality oxide caused breakdown voltage degradation may be solved by using PECVD oxide instead of the e-beam oxide layer in future work.

#### 4. Conclusion

In this study, the AlGaN/GaN HEMTs with the filled-oxide structure was proposed to reduce the device leakage current successfully. In addition, the post-gate annealing treatment was also employed to further alleviate the surface states/traps in the transistor. The results showed good on/off ratio and extremely small leakage current for the filled-oxide-isolated devices.

Fig. 4. Measured off-state breakdown characteristics

Fig. 3. Measured I<sub>G</sub>-V<sub>G</sub> characteristics.

## References

- [1] Rumyantev S L et al., J. Appl. Phys. vol. 88, no. 11, pp.6726, 2000

- [2] S. Arulkumaran et al., *Applied Physics Letters*, vol. 84, no. 4, pp.613-615, 2004

- [3] G. Meneghesso et al., *IEEE Trans. on Device and Materials Reliability*, vol. 8, no. 2, pp.332-343, 2008

- [4] D. Kikuta et al., Solid-State Electronics, vol. 50, no. 3, pp.316-321, 2006

- [5] G. Heidelberger et al., *Phys. Stat. Sol.*, (a) vol. 203, No.7, pp.1876-1881, 2006

- [6] Yong Cai et al., *IEEE Trans. on Electron Devices*, vol. 53, pp. 2207-2215, 2006

- [7] Y. Lin et al., SSDM 2007, pp. 156-157

- [8] D. Kikuta et al., Solid-State Electronics, vol. 50, no. 3, pp. 316-321, 2006