# Large Scale Test Circuits for Systematic Evaluation of Variability and Noise of **MOSFETs' Electrical Characteristics**

Y. Kumagai<sup>1</sup>, K. Abe<sup>1</sup>, T. Fujisawa<sup>1</sup>, S. Watabe<sup>1</sup>, R. Kuroda<sup>1</sup>, N. Miyamoto<sup>2</sup>, T. Suwa<sup>2</sup>, A. Teramoto<sup>2</sup>, S. Sugawa<sup>1</sup> and T. Ohmi<sup>2, 3</sup>

<sup>1</sup> Graduate School of Engineering, Tohoku University

<sup>2</sup>New Industry Creation Hatchery Center, Tohoku Univ., <sup>3</sup>WPI Research Center, Tohoku Univ.

6-6-10, Aza-Aoba Aramaki Aoba, Sendai, Miyagi 980-8579, Japan Phone: +81-22-795-3977 E-mail: kumagai@fff.niche.tohoku.ac.jp

### 1. Introduction

Variation of the electrical characteristics of MOSFETs such as drain-source current  $(I_{ds})$ , subthreshold swing factor (S-factor), threshold voltage (V<sub>th</sub>), junction leakage current  $(I_{jleak})$ , and gate leakage current  $(I_{Gleak})$  as well as their random noise have been critical issues for the reduction of power consumption for various applications of LSI[1-2]. In order to accurately evaluate these variation and noise, statistical measurements of a large number of MOSFETs comparable to the actual products are indispensable. We have investigated the measuring methods for these issues [3-6]. By combining these test circuits, a systematic evaluation of various statistic parameters of characteristics becomes available. Since the developed test circuits is so simple, we can evaluate the impacts of the various manufacturing processes and device parameters to the variation and noise characteristics. In this paper, we report the evaluating key concept and technology including the test circuit structure with the important results of these circuits.

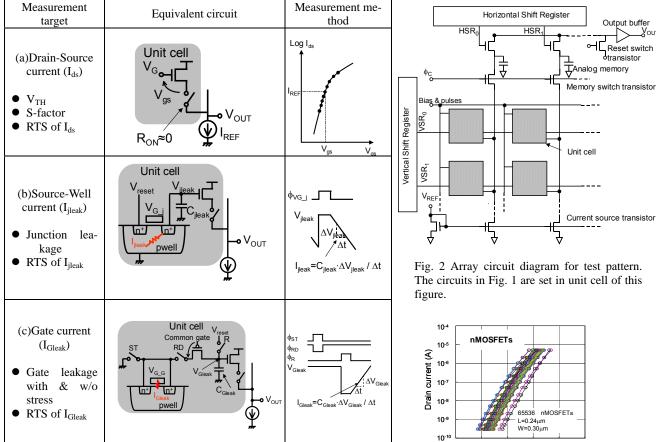

### 2. Test circuit

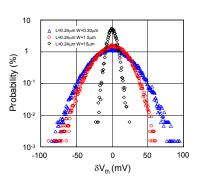

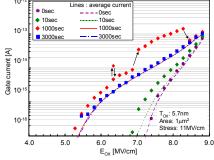

For statistical evaluation, the electrical properties for each MOSFET have to be measured in a very short period. Then, a large number of unit cells including devise under test (DUT) are set in a large array. In the unit cells, voltage signal that corresponds to the target current is readout using source follower amplifier. Fig. 1(a) shows concept of the circuit measuring Ids. The measured MOSFET and current source construct source follower circuit through a select switch.  $V_{gs}$  corresponding  $I_{ds}$  is expressed as  $\tilde{V}_{gs} = V_G - V_{OUT}$ .  $I_{ds} - V_{gs}$  characteristic are measured by changing the  $I_{REF}$  controlling the current source. S-factor is extracted from the  $I_{ds}\text{-}V_{gs}$  characteristic, represented as S=d(log  $I_{ds})/dV_{gs}$ .  $I_{ds}$  RTS noise of measured MOSFET appears as  $I_{gs}$  fluctuation in time scale corresponding to the  $I_{ds}$ . Fig. 1(b) shows concept of the circuit for measuring  $I_{jleak}$ . DUT's source terminal connected to gate of source follower transistor.  $I_{jleak}$  is converted to a voltage signal at the capacitor in the unit cell. When DUT turns on ,  $V_{jleak}$  is reset to  $V_{reset}$ . After turning off DUT, change in  $V_{jleak}$  is sampled continuously.  $I_{jleak}$  is represented as  $I_{jleak} = C_{jleak} dV_{jleak}/dt$ . Fig. 1(c) shows concept of circuit mearureing I<sub>Gleak</sub>. DUT's source/drain terminals connect to source follower transistor through common gate transistor and readout switch (RD).  $I_{Gleak}$  is converted to a voltage signal  $V_{Gleak}$  at the capacitor  $C_{\rm Gleak}.$  Thanks to the common gate transistor, voltage of DUT's source/drain terminal is constant while  $V_{\rm Gleak}$  is changed. Therefore, electric field across the gate oxide is constant. To apply a high voltage stress to the gate oxide of DUT for measuring stress induced leakage current, RD is turned off and the stress switch (ST) is turned on and high voltage is applied to  $V_{G\_G}$ . To measure  $I_{Gleak}$ , ST is turned off and RD is turned on, and reset switch (R) is turn on to reset C<sub>Gleak</sub>. After turning off R, a change in V<sub>Gleak</sub> is sampled continuously. Fig. 2 shows array test circuit diagram. This is constructed with arrayed unit cell described in Fig. 1, a vertical shift resistor and a horizontal shift resistor for selecting the unit cell, current source transistor located on every column, the analog memories for temporary storing voltage signal at each column, and the output buffer for the amplification of the voltage signal and output the signal outside the chip. The shift resistors fast select the unit cells sequentially and voltage signal from unit cells are readout with source follower circuit, therefore measuring a large number of cells in a short period becomes possible. In this experiment, the measurement of the Vth of one million MOSFETs can be finished in 0.7s,  $I_{jleak}$  of more than 28000 samples in 7.7s with ten times averaging,  $I_{Gleak}$  of more than 87000 samples in 20s for one bias. In addition the test circuits are simple, these can operate in a various MOSFETs, which have different gate length, gate width, gate insulator films, thickness, doping concentration and profile, and so on. The test pattern is manufactured by a 0.35- $\mu$ m 1-poly 1-metal CMOS technology and 0.22-µm 1-poly 2-metal CMOS technology.

### 3. Results

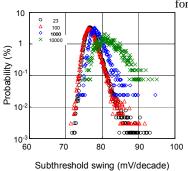

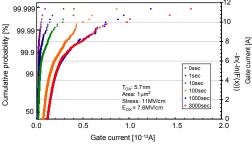

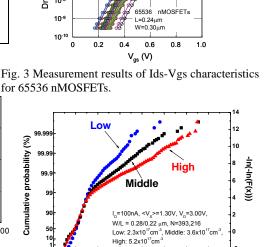

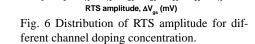

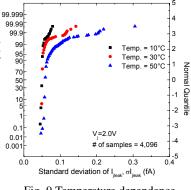

Fig. 3 shows measurement results of  $I_{ds}$ - $V_{gs}$  characteristic of 65536 MOSFETs. Fig. 4 shows distribution of  $V_{th}$  for three MOSFET's sizes. The  $V_{th}$  variation increases with a decrease of the gate width. Fig. 5 shows distribution of S-factor extracted from of  $I_{ds}$ - $V_{gs}$  characteristic as a function of antenna ratio that is a ratio of first metal layer area to gate area. The variation increases with increase in antenna ratio. Fig. 6 shows distribution of RTS of I<sub>ds</sub> as a function of channel doping concentration (NA). Noise intensity and occurrence frequency increase as NA becomes higher. Fig. 7 shows distribution of  $I_{\rm Gleak}$  for with and without stress. As stress time increase, tail cells increase. In very few cells of the tail cells, RTS of  $I_{Gleak}$  appears as shown in Fig. 8. In addition, RTS appears in I<sub>jleak</sub>. Fig. 9 shows the distribution of  $\sigma I_{jleak}$  in the time scale, that indicates noise intensity.  $\sigma I_{ileak}$  increases with increase in temperature.

## 4. Conclusions

This test circuits can measure statistical characteristics of MOSFETs in short time and can operate when the gate size, doping concentration and other device parameters of measuring MOSFET are changed. In addition, RTS noise are detected in Ids, Ijleak and IGleak by a fast sampling of the signals in the time scale. This developed test circuits is very efficient for systematic evaluation and useful to suppress the variability of electrical properties in MOSFETs.

#### References

- [1] B. Hoeneisen et al., Solid State Electron., p. 819, 1972.

- [2] T. Ohmi et al., J. Phys. D, Appl. Phys., p. R1, 2006.

- [3] S. Watabe et al., in IEEE T-ED, to be published.

- [4] K. Abe et al., in Symp. VLSI Tech. Dig., p. 210, 2007.

- [5] Y. Kumagai et al., Proc. IRPS, p. 219, 2008.

- [6] K. Abe et al., Proc. IRPS, p. 683, 2010.

Fig. 1 Concept of three circuits measuring  $I_{\text{ds}}, I_{\text{jleak}}$  and  $I_{\text{Gleak}}.$

Fig. 4 Distribution of  $V_{th}$  for three MOSFET's sizes.

Fig. 5 Distribution of S-factor for nMOSFETs having antenna ratios of 23, 100, 1000 and 10000.

Fig. 7 Distribution of gate leakage current for w/o stress and with stress.

Cumulative probability (%)

99

Fig. 8  $I_G$ - $V_G$  characteristic with and w/o stress. With 1000s stress, RTS appeared.

15 20 25 30

Cumulative Probability (%)

Fig. 9 Temperature dependence of  $\sigma I_{\text{jleak}}$  distribution.