# Effect of Fluorine Incorporation on WSi<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/GaAs Gate Stack

B.S. Ong,<sup>1,2</sup> K.L. Pey,<sup>1,2,a)</sup> C.Y. Ong,<sup>2</sup> C.S. Tan,<sup>2</sup> C.L. Gan,<sup>1,3</sup> H. Cai,<sup>3</sup> D.A. Antoniadis<sup>1,4</sup> and E.A. Fitzgerald<sup>1,5</sup> <sup>1</sup>Advanced Materials for Micro and Nano-Systems, Singapore-MIT Alliance

<sup>2</sup>School of Electrical and Electronic Engineering, Nanyang Technological University

<sup>3</sup>School of Materials Science and Engineering, Nanyang Technological University

<sup>4</sup>Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology

<sup>5</sup>Department of Materials Science and Engineering, Massachusetts Institute of Technology

Phone: +65 67906371, Fax: +65 67933318, E-mail: eklpey@ntu.edu.sg

### 1. INTRODUCTION

III-V compound semiconductors have been considered as the alternate channel material to replace Si for the metaloxide-semiconductor field effect transistors (MOSFETs) beyond the 22 nm technology node owing to their higher intrinsic electron mobility. However, III-V materials do not have a thermodynamically stable native oxide that can match the device performance similar to SiO<sub>2</sub> on Si. Several pregate surface passivation methods on III-V metal-oxidesemiconductor capacitor (MOSCAP) have been studied to remove the interface states [1]. However, not many post-gate treatments have been reported for GaAs MOS. Recently, fluorine incorporation into high- $\kappa$  dielectric on Si [2], Ge [3] and InGaAs [4] substrates have shown improved device performance and reliability.

In this paper, we study the effect of post-gate treatment by using CF<sub>4</sub> plasma to incorporate fluorine (F) into the Al<sub>2</sub>O<sub>3</sub> dielectric on GaAs substrate. We found out that with F incorporation, a lower dielectric constant  $(K_{eff})$  value is obtained and the reliability of gate stack is enhanced due to fluorine passivation of interface states and bulk oxide traps.

## 2. DEVICE FABRICATION

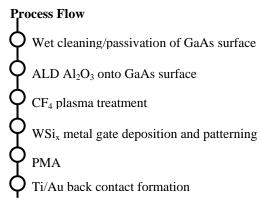

The process flow for fabrication of GaAs MOSCAP is shown in Fig. 1. GaAs capacitors were fabricated on (100) ptype (~8 x  $10^{17}$  cm<sup>-3</sup>) Zn-doped GaAs and (100) n-type (~3 x 10<sup>16</sup> cm<sup>-3</sup>) Si-doped GaAs. Prior to an atomic layer deposition (ALD) of Al<sub>2</sub>O<sub>3</sub>, standard cleaning procedures were used. After these surface pre-treatments, the samples were loaded into the ALD system immediately. A layer of Al<sub>2</sub>O<sub>3</sub> dielectric about 11 nm was grown at 300 °C using of Trimethylaluminum (TMA) and H<sub>2</sub>O as the precursors. After the  $Al_2O_3$  deposition, some samples were treated with  $CF_4$ plasma. WSix metal gate was then deposited using CVD system at 330 °C using WF<sub>6</sub> and SiH<sub>4</sub> as the gas sources and argon as the carrier gas. Capacitors were lithographically defined and dry etched using chlorine-based reactive ion etching system. Post metallization annealing (PMA) was then performed for both CF4 treated and control samples at 600 °C in N<sub>2</sub> ambient for 30 s. A Ti/Au bilayer metal film was finally deposited using electron beam evaporator for back-contact formation.

## 3. RESULTS AND DISCUSSION

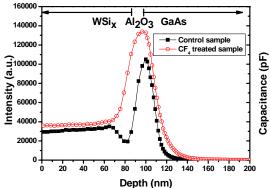

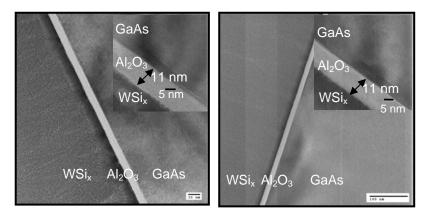

Fig. 2 shows the cross-sectional TEM micrographs of the GaAs MOSCAP without and with CF<sub>4</sub> treatment prior to WSi<sub>x</sub> gate deposition, respectively. The thickness of Al<sub>2</sub>O<sub>3</sub> is about 11 nm as shown in the inset of Fig. 2(a). This gate stack using CVD process exhibits smooth and sharp interfaces. The thickness of Al<sub>2</sub>O<sub>3</sub> for MOSCAP with CF<sub>4</sub> treatment is similar to the control sample and the HRTEM micrograph in Fig. 2(b) also shows smooth and sharp interfaces. This proves that the CF<sub>4</sub> plasma does not etch Al<sub>2</sub>O<sub>3</sub>, which will affect the abruptness of the interfaces.

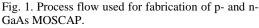

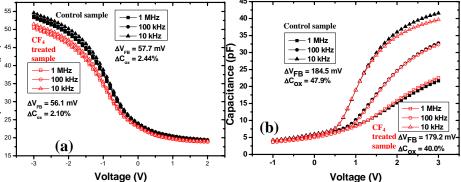

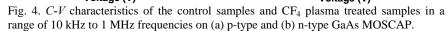

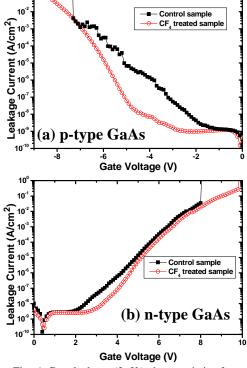

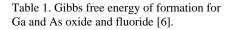

Fig. 3 shows the SIMS depth profile for the MOSCAPs with and without CF<sub>4</sub> treatment. The F atoms detected for the control sample are attributed to the WF<sub>6</sub> gas precursor used for metal gate deposition. The F concentration detected in the  $Al_2O_3$  is higher for the CF<sub>4</sub> treated sample. Fig. 4 shows the C-V characteristics of GaAs MOSCAP with and without CF4 plasma treatment on p and n-type GaAs. From Fig. 4(a), the CF<sub>4</sub> plasma treated sample shows a lower accumulation capacitance on p-type MOSCAP and hence, a lower  $K_{eff}$  due to F incorporation. The  $K_{eff}$  is 6.6 and 6.3 for the control sample and CF<sub>4</sub> treated sample, respectively. Though a lower  $K_{eff}$  value was obtained, F incorporation into the high- $\kappa$ dielectric helps to improve the C-V characteristics of the sample, as shown in Fig. 4 where the CF<sub>4</sub> treated samples have lower frequency dispersion at accumulation ( $\Delta C$ ) and at flatband voltage ( $\Delta V_{FB}$ ). Fig. 4(b) shows large frequency dispersion on n-type GaAs MOSCAP as compared to p-type that could probably be due to presence of other surface imperfections such as surface kinks which generate high density of defect states in the bandgap [5]. Fig. 5 shows the distribution of interface states  $(D_{it})$  for both p- and n-type GaAs MOSCAP measured using A.C. conductance method at 150 °C. It is verified that the CF<sub>4</sub> treated samples have a lower  $D_{it}$  as compared to control samples for both p- and ntype GaAs MOSCAP. Table 1 shows the Gibbs free energy of formation of GaF<sub>3</sub>, AsF<sub>3</sub> and GaAs native oxides [6]. The lower  $D_{it}$  could be attributed to energetically preferred GaF<sub>3</sub> and AsF3 as compared to GaAs native oxides. These native oxides are deemed as one of the sources for interface states.

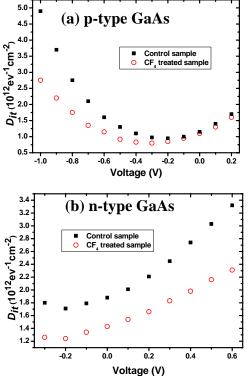

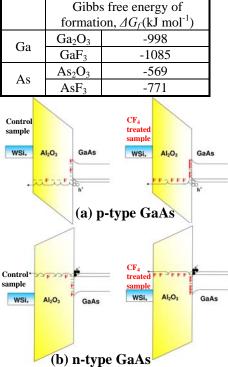

Fig. 6 shows the  $I_g$ - $V_g$  characteristics for both the p- and n-type gate stacks. It is noticed that samples with CF<sub>4</sub> plasma treatment exhibit lower leakage current and higher breakdown voltage in the accumulation region as shown in Figs. 6(a) and (b). This is due to passivation of bulk oxide traps in the  $Al_2O_3$  dielectric by the F atoms. A schematic model is proposed for F passivation as shown in Fig. 7. F atoms are able to passivate the interface states and bulk oxide traps, thereby improving the device performance of p- and ntype GaAs MOSCAP.

#### 4. SUMMARY

F-atom incorporation into the GaAs gate stack reduces the  $K_{eff}$  of Al<sub>2</sub>O<sub>3</sub> dielectric, but improves the MOSCAP characteristics by effectively passivating the interface states and bulk oxide traps, thereby improving the overall performance and reliability of the gate stack.

#### REFERENCES

- [1] M. Houssa et al., MRS Bulletin, **34** (7), 504 (2009).

- [2] C. S. Lai et al., Appl. Phys. Lett., 89, 72904 (2006).

- [3] R. Xie et al., Appl. Phys. Lett., 92, 163505 (2008).

- [4] Y. T. Chen et al., Appl. Phys. Lett., 95, 013501 (2009).

- [5] M. D. Pashley et al., Physical Review B, 48, 4612 (1993).

- [6] Yaws handbook of thermodynamic properties for

hydrocarbons and chemicals

Fig. 3. SIMS depth profile of F atoms in the  $WSi_x/Al_2O_3/GaAs$  gate stack for samples with and without  $CF_4$  plasma treatment.

Fig. 2. Cross-sectional TEM micrographs of the gate stack of (a) control sample and (b)  $CF_4$  treated sample and their corresponding HRTEM micrographs in the inset. The oxide thickness and interface roughness for (a) and (b) are similar implying that the  $CF_4$  plasma does not etch  $Al_2O_3$ .

Fig. 5. Plots of  $D_{it}$  vs gate voltage for control samples and CF<sub>4</sub> plasma treated samples on (a) p-type and (b) n-type GaAs MOSCAP.

10

Fig. 6. Gate leakage  $(I_g - V_g)$  characteristics for control samples and CF<sub>4</sub> plasma treated samples on (a) p-type and (b) n-type GaAs MOSCAP.

Fig. 7. Schematic model for F atoms passivation of interface states and bulk oxide traps for (a) ptype and (b) n-type GaAs MOSCAP in accumulation region.