# C-V Characteristics and Analysis of Undoped Gate-All-Around Nanowire FET Array

Rock-Hyun Baek<sup>1</sup>, Chang-Ki Baek<sup>2</sup>, Sang-Hyun Lee<sup>1</sup>, S. D. Suk<sup>3</sup>, M. Li<sup>3</sup>, Y. Y. Yeoh<sup>3</sup>, K. H. Yeo<sup>3</sup>, D.-W. Kim<sup>3</sup>, Jeong-Soo Lee<sup>1,4</sup>, Dae M. Kim<sup>2</sup> and Yoon-Ha Jeong<sup>1,4</sup>

<sup>1</sup>Pohang University of Science and Technology (POSTECH),

Dept. of Electronic and Electrical Eng., Gyeongbuk, Pohang 790-784, Republic of Korea

Phone: +82-54-279-2897, E-mail: rock8201@postech.ac.kr

<sup>2</sup>Korea Institute for Advanced Study (KIAS), School of Computational Sciences, Seoul 130-722, Republic of Korea <sup>3</sup>Samsung Electronics Company, Semiconductor R&D Center, Gyeonggi, Yongin 449-711, Republic of Korea

<sup>4</sup>National Center for Nanomaterials and Technology (NCNT), Gyeongbuk, Pohang 790-784, Republic of Korea

#### 1. Introduction

The gate-to-channel capacitor provides the fundamental device information such as EOT(electrical oxide thickness), flat band voltage, inversion charge, mobility, etc. and is useful for evaluating the device performance and characteristics [1-2]. However, as the active area (WxL) decrease, the capacitance of single device becomes small and hard to measure. Also, the gate tunneling current with thin oxide distorts the C-V shape [3-4]. Fortunately, the nanowire FET shows low gate leakage due to gate-all-around structure [5] but still suffers from the extremely small active area problem.

In this paper, we report the C-V characteristics measured from nanowire capacitor (NWCAP), which has been fabricated by connecting in parallel a number of identically processed nanowire FETs. Various capacitances were measured by using different electrode configurations. Moreover, we analyzed the effect of undoped and floating channel on the C-V curves and extracted accurate inversion charge ( $Q_{inv}$ ) and mobility. The measured data were compared extensively with conventional planar MOS capacitor (MOSCAP) data.

#### 2. GAA nanowire FET array structure and measurements

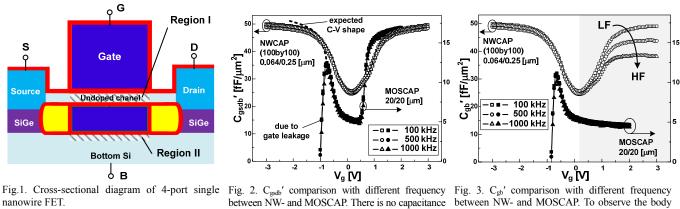

Fig. 1 shows a 4-port single nanowire FET structure. Because the device was fabricated on bulk silicon, the nanowire FET has a bottom Si and it is connected with Body contact. The undoped channel was surrounded by Gate and it thus floats on the bottom Si. The oxide was formed by in-situ steam generated (ISSG) process with  $T_{ox}$ =3.3 nm. The NWCAP has 100 by 100 array with single geometry W/L=64/500, 64/250, 64/100 nm, respectively. The planar MOSCAP used for comparison has W/L=20/20 µm with  $T_{ox}$ =2 nm. The capacitances were measured by Agilent 4284 LCR meter with  $V_{gs}$  from -3 V to 3 V in NWCAP and from -2 V to 2 V in MOSCAP with 50, 100, 300, 500, 700, 900, 1000 kHz. The C-V data are denoted by  $C_{gsd}$ , representing the Gate signal with Source/Drain grounded, while the other terminals kept Open.

#### 3. Frequency response of undoped floating channel

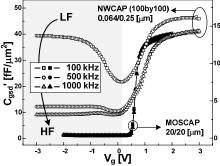

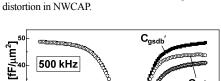

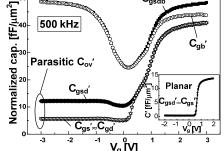

For investigating the undoped floating channel effect, we measured the various capacitance components ( $C_{gsdb}$ ,  $C_{gb}$ ,  $C_{gsd}$ ) per unit area from both NW- and MOSCAP and have presented the data in Fig. 2~5. All capacitance values were normalized by active area for accurate comparison.

Fig. 2 shows the  $C_{gsdb}'-V_g$  curves from NW- and MOSCAP measured with different frequencies. In NWCAP (open symbols) there is no severe capacitance distortion in the accumulation region owing to small leakage path in surrounded gate structure, in contrast with MOSCAP (solid symbols). In MOSCAP, as well known, the holes as substrate majority carriers in accumulation region ( $C_{gb}'$  in Fig. 3) and electrons in the inversion region ( $C_{gsd}'$  in Fig.4) can easily catch up with frequency change of the gate voltage. Accordingly, the  $C_{gsdb}'$ ,  $C_{gb}'$  and  $C_{gsd}'$  curves exhibit

frequency independent behavior (see Fig. 2-4). On the other hand, the NWCAP has the more complicated capacitance ( $C_{gsdb}'$ ,  $C_{gb}'$ ,  $C_{gsd}'$ ) characteristics, as clearly shown in Table.1.

(a)  $C_{gsdb}'$ : In accumulation region,  $C_{gsdb}'$  in Fig. 2 is same with  $C_{gb}'$  in Fig. 3. It implies the  $C_{gb}'$  caused by fast hole charging/discharging from bottom Si (Region II in Fig. 1) constitutes the dominant component of  $C_{gsdb}'$ . In inversion region,  $C_{gsdb}'$  consists mainly of fast electron charging/discharging between Source/Drain and channel (Region I in Fig. 1) and some slowly generated electrons (Region II in Fig. 1).

(b)  $C_{gb}/C_{gsd}$ : The  $C_{gb}$ ' (Fig. 3) and  $C_{gsd}$ ' (Fig. 4) splitting in the inversion and accumulation regions result from slow electron hole generation in bottom Si and undoped channel or electron hole injection from respective terminals. However,  $C_{gsd}$ ' in the inversion region in Fig. 4 shows the inversion charge injected from Source/Drain without the large band bending as occurs in the surface depletion region in planar MOSCAP.

Fig. 5 shows the  $C_{gsdb}$ ,  $C_{gb}'$ ,  $C_{gsd}'$ ,  $C_{gs}'$  and  $C_{gd}'$  variations versus  $V_{gs}$  at 500 kHz. In the accumulation region of NWCAP, the  $C_{gsd}'$  data is equal to the summation of  $C_{gs}'$  and  $C_{gd}' (C_{gsd}' \approx C_{gs}'+C_{gd}')$  and much smaller than  $C_{gsdb}'$ . It indicates the amount of hole required is determined by it generation in floating channel or injection from bulk Si and the generated holes from the Source and Drain are almost same. On the other hand, in the inversion region,  $C_{gsd}'$ ,  $C_{gs}'$  and  $C_{gd}'$  are same ( $C_{gsd}' \approx C_{gs}' \approx C_{gd}'$ ), indicating sufficient electron supply from the Source/Drain regardless of channel volume. In the MOSCAP (see the inset of Fig. 5),  $C_{gsd}'$ ,  $C_{gs}'$  and  $C_{gd}'$  are same in all bias regions, indicating thereby that the non-floating substrate contacted channel supplies the required amount of holes in the accumulation.

## 3. Results and Discussions

Fig. 6 shows the inversion capacitance per unit area  $C_{inv}'$  which is obtained by rejecting overlap capacitance ( $C_{ov}'\approx9.1$  fF/ $\mu m^2$  in NWCAP, 0.42 fF/ $\mu m^2$  in MOSCAP) from the  $C_{gsd}$  at 1MHz with  $V_{gs}$ =-3 V and -2V, respectively. As shown in Fig. 6, the NWCAP has larger  $C_{inv}'$  than MOSCAP in spite of the thicker oxide used and shows excellent gate controllability for channel inversion, as expected.  $Q_{inv}'$  shows its corresponding inversion charge per unit area.

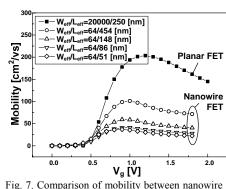

Using the extracted  $Q_{inv'}$ ,  $R_{sd}$  [6] and  $L_{eff}$ , we obtained the accurate mobility from the single FET via the well known eq. (1) and presented the  $\mu$ -V<sub>g</sub> curves in Fig. 7. Although larger  $Q_{inv'}$  was attained in the NWCAP, the extracted mobility therein is smaller than MOSCAP's. It indicates that the carrier transport in nanowire limited by lateral factors e.g. series resistance, potential barriers at Source/Drain, etc., and not by vertical factors. However, if the mobility is calculated by using channel diameter of 12 nm in [7], its values are comparable with planar MOSFET.

#### 4. Conclusions

In this study, we have investigated the gate response of undoped

and floating channel by measuring various C-V data from nanowire capacitor arrays. The undoped channel in nanowire suffers from slower frequency response but it is not a serious problem in inversion region in which device operates. In addition, the NWCAP is shown to exhibit superior channel inversion with higher Q<sub>inv</sub>', compared with the planar MOSCAP. Thus, the performance of nanowire FET could be greatly improved with the process refinements made in Source/Drain contacts. Also, the overlap capacitance has to be reduced for high frequency applications.

## Acknowledgements

This research was supported by World Class University (WCU) program through the Korea Science and Engineering Foundation funded by the Ministry of Education, Science and Technology. (Project No. R31-2008-000-10100-0). Also, this work was supported by National Research Foundation of Korea Grant funded by the Korean Government (2009-0089200) and partially supported by the BK21 program, the National Center for Nanomaterials Technology (NCNT) in Korea and "System IC 2010" project of Korea Ministry of Knowledge Economy. Finally, the authors thank Samsung Electronics Co., Ltd. for device fabrication.

## References

- [1] S. Severi et al., IEEE Trans. Electron Devices, 54(2007) 2690.

- [2] I. Ferain et al., IEEE Trans. Electron Devices, 55(2008) 1657.

- [3] C.-H. Choi et al., IEEE Trans. Electron Devices, 47(2000) 1843.

- [4] Y. L. Hsu et al., Solid-State Electron., 46(2002) 1941.

- [5] K. H. Yeo et al., in Proc. IEDM. Tech. Dig. (2006) 1.

- [6] R.-H. Baek et al., IEEE Trans. Nanotechnol., 9(2010) 212.

- [7] S. D. Suk et al., in Proc. IEDM, Tech. Dig. (2007) 891.

Fig. 4.  $C_{gsd}^{}{}^\prime$  comparison with different frequency  ${}^{}_{}$  Fig. 5.  $C_{gsdb}^{}{}^\prime, \; C_{gb}^{}{}^\prime, \; C_{gsd}^{}{}^\prime,$ between NW- and MOSCAP. To observe the S/D versus  $V_g$  at 500 kHz. effect only, the Body was opened.

Accumulation

Fast h<sup>+</sup> C/D from Body

(Region II in Fig.1)

Fast h<sup>+</sup> C/D from Body

(Region II in Fig.1)

in channel (Region I in Fig.1)

\* C/D(charging/discharging), h<sup>+</sup>(hole), e<sup>-</sup>(electron)

Cgsdb

$C_{gb}$

T<sub>ox</sub>=3.3 nm

MOSCAP

20/20 [µm]

T<sub>or</sub>=2 nm

Fast e C/D from Source/Drain and

some slow e<sup>-</sup> from Body

(Region I, II in Fig.1)

Slow  $e^{-}/h^{+}$  generation from Body

(Region II in Fig.1)

(Region I in Fig.1)

-2 -2 va v  $C_{gs}{}^\prime$  and  $C_{gd}{}^\prime$  variation Fig. 6.  $C_{inv}{}^\prime$  and  $Q_{inv}{}^\prime$  comparison between NWand MOSCAP. The NWCAP shows excellent electrostatic properties in spite of thicker Tox.

Fig. 7. Comparison of mobility between nanowire and planar FET within similar channel lengths.

Slow e<sup>-</sup>/h<sup>+</sup> generation Fast e C/D from the Source/Drain  $C_{gsd}$

S/D

floating

Body

floating