# Effects of Plasma-PH<sub>3</sub> passivation on Mobility Degradation Mechanisms and Current Conduction Mechanisms of In<sub>0.53</sub>Ga<sub>0.47</sub>As N-MOSFET

Sumarlina A.B.S<sup>1,2</sup>, H.J.Oh<sup>1</sup>, A.Du<sup>2</sup>, and S. J. Lee<sup>1,\*</sup>

<sup>1</sup> National University of Singapore, Department of Electrical and Computer Engineering, Singapore 117576 Phone: +65-6516-6140, Fax :+65 6779-1103,\*E-mail: elelsi@nus.edu.sg,

<sup>2</sup> GLOBALFOUNDRIES Singapore Pte.Ltd, 60 Woodlands Industrial Park D, St2, 738406, Singapore

# 1. Introduction

III-V compound semiconductor is becoming attractive as a material for high performance MOSFETs. In fact, the high performances of InGaAs MOSFETs with plasma-PH<sub>3</sub> passivation treatment have been demonstrated and the effect of variable process parameters have been studied [1-2]. Improvements made by the treatment is due to the presence of P-for-As exchange reaction through removal of As-O<sub>x</sub> components and the  $P_x N_y$  layer which achieves an abrupt, smooth interface. However, understanding of how this treatment is effective in improving the device performance in terms of its mobility  $(\mu)$ and current conduction have yet to be understood, especially since a detailed knowledge of carrier transport can give insight to defects that are present in the oxide. This motivated our current work.

## 2. Device Fabrication

MBE grown In<sub>0.53</sub>Ga<sub>0.47</sub>As on InP substrate was processed for device fabrication and material characterization. Detailed process flow can be referred to in Ref [1-2]. However, this work uses HfAlO of 5nm thick. After device fabrication, devices were measured at a temperature range between 250K to 420K for analysis.

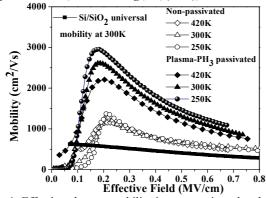

## 3. Mobility Scattering Mechanisms & Factors causing Mobility Improvement

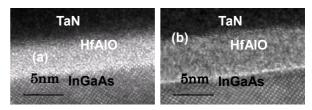

To investigate the factors governing µ, temperature dependence was investigated shown in Fig 1. µ of non-passivated devices, with interface trap correction, shows that at low E<sub>eff</sub> it increases with decreasing temperature, but still weaker than that of plasma-PH<sub>3</sub> passivated. This means that Coulombic scattering, which partially hides the effects of scattering with high-k phonons, contributes to the  $\mu$  for non-passivated devices. However, phonon scattering contributes to  $\mu$  of plasma-PH<sub>3</sub> passivated. Under high E<sub>eff</sub>,  $\mu$  is weakly dependent on temperature for non-passivated, but still strongly dependent on temperature for plasma-PH<sub>3</sub> passivated, suggesting surface roughness scattering or interface dipole scattering for the former and phonon scattering for the latter. However, RMS data from AFM shows ~0.16nm and ~0.15nm for non-passivated and plasma-PH<sub>3</sub> passivated respectively, with TEM images shown in Fig 2 (a) and (b) not revealing any significant increase in interface roughness, deduced from the waviness of the interface. This shows the possibility of interface dipole scattering in the non-passivated devices.

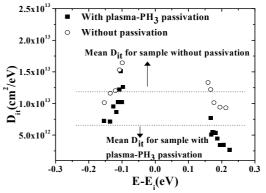

Since electron trapping induced by charges near the conduction band edge ( $E_c$ ) could be the cause for low channel  $\mu$  of MOSFETs, the reduced D<sub>it</sub> values near E<sub>c</sub> for passivated devices may be the reason for the improvement in the low  $E_{eff} \mu$ .

Close to one order of magnitude reduction in D<sub>it</sub> near to E<sub>c</sub> as shown in Fig 3 is observed due to the ability of the passivation in reducing elemental As and As-As bond which have their energy levels in the upper half of the bandgap [3-4]. This may be achieved by forming volatile hydrides, AsH<sub>x</sub> [2], through the small amount of H atoms existing in the PH<sub>3</sub>-based plasma treatment process and P-for-As exchange reaction. It can also be effective in reducing Ga vacancies seen in the reduction in  $D_{it}$  at ~0.2eV above  $E_{v}$  [5] which is also confirmed from Ga outdiffusion into the high-k from EDX (not shown). Fixed oxide charges gives values 0.75-2.2x10<sup>11</sup>cm<sup>-2</sup> for passivated and non-passivated respectively, which is one order lesser than that of D<sub>it</sub> implying that a significant amount of Coulombic scattering is caused by D<sub>it</sub>. For the mid E<sub>eff</sub> region, a more severe phonon scattering for non-passivated compared to passivated is observed, based on  $\mu_{ph}$  results from Matthiessen's rule. Phonon scattering from the substrate is expected to be the same for both samples, and hence the existence of the additional source of phonon scattering from the non-passivated suggests that HfAlO/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface contributes to an interfacial phonon scattering which is suppressed by the presence of the P<sub>x</sub>N<sub>y</sub> layer. The origin of this scattering, caused by the soft optical phonons in HfAlO, was found to have its scattering rate having a relatively weak function of temperature (not shown). Finally, the interface dipole scattering that exists at high Eeff of non-passivated could be due to Hf atoms (smaller electronegativity than Al) occupying the Ga vacancy sites, which changes the polarity of the interface dipoles, hence enhancing the potential fluctuation at the interface as explained in [6].

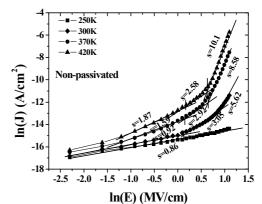

## 4. Current Conduction Mechanisms

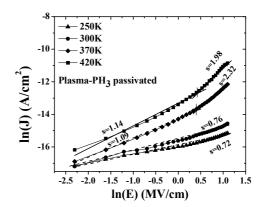

Gate current density result shows that plasma-PH<sub>3</sub> passivation is seen to improve, not only the  $\mu$  characteristics, but also the current density voltage. The curves of Fig 4, obtained from substrate injection region, are in agreement with Lampert's Space Charge limited Conduction (SCLC) theory. At 300K and low E<sub>eff</sub>, the curves are linear with slopes ~1, indicating an Ohmic behavior. However, a larger contribution of Ohmic conduction current is observed in non-passivated than passivated devices due to the higher D<sub>it</sub> existing near the E<sub>c</sub> (shown in Fig 3) with the shallower traps lying closer to  $E_c$ , thus generating a hopping current [7]. Beyond Ohmic region, Fig 4(a) shows non-passivated devices experiencing a slope of  $\sim 3.05$  in the J-V equation [8] which implies the trap states being exponentially distributed in energy [9]. This could originate from surface defects like vacancies and structural disorders, which could also be responsible for the interface dipole scattering explained earlier. On the other hand, Fig 4(b) shows that plasma-PH<sub>3</sub> passivated device does not have a slope of at least 2, thus it does not experience an SCLC regime, but only Ohmic conduction dominates at 300K implying that carrier transport is facilitated through the oxide. At >300K, Fig 4(a) shows the absence of Ohmic conduction in the low  $E_{eff}$ , since the slopes deviate from ~1. However the presence of Schottky emission (not shown) suggests it would be more appropriate to consider the leakage behavior of non-passivated devices as being controlled by Frenkel Poole emission and not SCLC at high  $E_{eff}$ . The trap energy levels are given as ~0.47-0.54eV below  $E_c$ . On the other hand, the slopes of ~2 for plasma-PH<sub>3</sub> passivated devices in Fig 4(b), imply a trap-free SCLC regime, where injection of carriers at the interface is limiting the current hence indicating a well formed interface between HfAlO and InGaAs.

#### 5. Summary

Carrier transport mechanisms of non-passivated and plasma-PH<sub>3</sub> passivated InGaAs MOSFETs have been studied with temperature dependence. It is found that Plasma-PH<sub>3</sub> passivation improves the device performance through (i) reduction in D<sub>it</sub> resulting in reduced Coulombic scattering at low E<sub>eff</sub> (ii) reduced surface optical phonon scattering at mid  $E_{\text{eff}}$  and (iii) reduced interface dipole scattering at high  $E_{\rm eff}$  Also, the dominance of Ohmic conduction and trap-free SCLC mechanism at >300K, in comparison to Schottky emission and Frenkel Poole emission (trap energy levels~0.47-0.54eV) for non-passivated, at low Eeff and high Eeff respectively, is the cause of reduced gate leakage and also imply the improvement in interface quality. The origins of the defects contributing to these conduction mechanisms could be related to the increased Coulombic scattering at low Eeff and interface dipole scattering at high Eeff for non-passivated devices.

#### References

- J.Q.Lin *et al.*, *Tech .Digest IEDM*, (2008), 977

H.-J.Oh et al, *J. Electrochem.Soc.*, **157**, (2010), H1051

G.Brammertz et al, *J. Electrochem.Soc* **155**,(2010), H945

- [4] J.Robertson, Microelectronic Eng. 86, (2009), 1558

- [5] H.P.Komsa, *Microelectronic Eng.*, **88**, (2011), 1436

- [6] Y.Urabe *et al*, *Tech*. *Digest IEDM*, (2010), 142

- [7] P. Mark *et al*, *J. Appl. Phys.* **33**, (1962), 205

- [8] D. Joung et al, *Appl.Phys.Lett*, **97**, (2010), 093105

- [9] R.Perera *et al*, *Microelec.Eng.*, **65**, (2003), 357

Fig 1. Effective electron mobility in non-passivated and pasivated InGaAs N-MOSFETs at various temperatures from 250K to 420K

Fig 2(a) HR-TEM images of non-passivated and (b) plasma-PH<sub>3</sub> passivated InGaAs MOSFET.

Fig 3. Energy distribution of  $D_{it}$  as determined by the rise/fall time dependence of Charge Pumping currents. ~Two times reduction in mean  $D_{it}$  is observed with plasma-PH<sub>3</sub> passivation compared to non-passivated.

Fig 4 (a) ln(J) vs ln(E) plots of non-passivated InGaAs devices for temperatures between 250K to 420K.

Fig 4 (b) ln(J) vs ln(E) plots of plasma-PH<sub>3</sub> passivated InGaAs devices for temperatures between 250K to 420K.