# Inkjet-Printable Hybrid Gate dielectrics for the Enhancement of Pentacene-based Thin Film Transistor Performance

Chao-Te Liu<sup>1</sup>, Wen-Hsi Lee<sup>1</sup>, Tsu-Lang Shih<sup>1</sup> and Hsueh-Jen Yan<sup>1</sup>

<sup>1</sup> Dept. of Electrical Engineering, National Cheng Kung University, Tainan 701, Taiwan, ROC Phone: +886-9-21019785 E-mail: n28981036@mail.ncku.edu.tw

### 1. Introduction

Recently, organic thin film transistors (OTFTs) for display have been studied widely because of potential application in low cost, large area and suiting for flexible electronics. They can be fabricated by easy processes based on solution methods. But the mobility of OTFTs is lower and the threshold voltage is higher than amorphous Si TFTs. Gate dielectrics play a significant role in ameliorating the performance of a field effect OTFTs<sup>1,2</sup>. Currently, easily processable polymer materials had been used as the gate dielectric of OTFTs but keep a relatively low dielectric constant (k=2-4)<sup>3-5</sup>, and it is required to reduce the film thickness to nanoscale in the cause of large capacitance.

Inkjet printing (IJP) process has been developed for semiconductor devices recently and become a promising tool for the display industry because of the possibility in mask-free process and patternability for nanoscale.

In this paper, we mixed cross-linked poly-4 vinyl phenol (PVP) solution and nanoparticles of TiO<sub>2</sub> by pearl milling to increase dielectric constant and raise dispersant of nanoparticles simultaneously for successful jetting. We successfully printed dielectric layout, accomplishing the purpose of directly-patternable and low roughness after curing, when the solid content of TiO<sub>2</sub> about 3 wt% in the ink. Finally, we realized a low leakage current density in the nanocomposite dielectric and high current ratio in the pentacene-TFTs device with top contact structure. These devices exhibited p-channel TFT characteristics with a high field-effect mobility (a saturation mobility of ~0.58  $cm^2V^{-1}s^{-1}$ ) and a low voltage operation (<6 V) comparable to the spin coating (SPC) process, indicating that these NC-dielectric materials can be used in low-cost and high-performance printable electronics. The fundamental properties of PVP/TiO<sub>2</sub> nanocomposite by inkjet printing and the carrier mobility relation to semiconductor layer films were examined with Raman spectroscopy analysis.

# 2. Experiments

# (1) <u>Hybrid of inorganic-organic materals</u>

In this work, two types of devices were fabricated and shown in Fig. 1. Nano-composite dielectric layers were formed by the cross-linked PVP (Mw~25,000, Aldrich) and cross-linking reagent poly-(melamine-co-formaldehyde) methylated (PMCF, Mw=511, Aldrich) dissolved in propylene glycol monomethyl ether acetate (PGMEA) selected as the polymer matrix in which titanium dioxide (TiO<sub>2</sub>) nano-particles, a high-k material (Hombitan® RM300, k=114), were uniformly dispersed. The dispersion of ceramic slurry with the surface modified nano-TiO2 particles by using 1-4 wt% dispersant (polysester) in PGMEA after pearl milling for 15 min at 2800 rpm, and subsequently blending the slurry of  $TiO_2$  nanoparticles into cross-linked PVP solution which adjusted the concentration of the blended  $TiO_2$  nanoparticles.

## (2) <u>Fabrication of devices</u>

100 nm thick indium-tin oxide (ITO) layer was thermally deposited as a gate electrode on the glass substrate. The NC-film on ITO glass substrates were inkjet printed with a thickness of 300-400 nm, from the filtered (0.45-um PTFE filter) compound slurry and then baked at 190°C for 30 min. The printer was piezoelectric drop-on-demand (DOD) inkjet printer (DMC-2800, DIMATIX Corp.) and the spherical drops were jetted through cartridge nozzles by adjusting voltage waveform to form a flat insulating layer. Gold was thermally mask-evaporated as cover electrodes for the MIM to obtain the leakage current density and dielectric constant.

For the top-contact OTFT structure, pentacene film was thermally deposited as an organic semiconductor layer on the nanocomposite gate dielectric film and its thickness was about 200 nm. Finally, as drain and source contacts, Au was thermally evaporated through another shadow mask with channel W/L=2. The current-voltage (I-V) characteristics of MIM were measured by an HP 4156A semiconductor parameter analyzer. The capacitance measurements were conducted with a HP 4284 A Precision LCR meter. The surface microstructures of the pentacene films on the dielectrics were characterized using a scanning electron microscope (SEM, XL-40FEG, Philips).

# 3. Results and Discussions

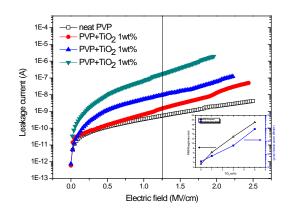

The deteriorating leakage current density of insulator layers due to the increasing of leakage conduction path relates to the surface roughness, which increased with the  $TiO_2$  ratio in the MIM structure are shown in Fig. 1, which indicate the differences in morphology between the neat and nano-composite films, are in evident.

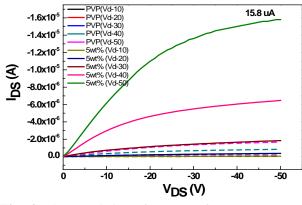

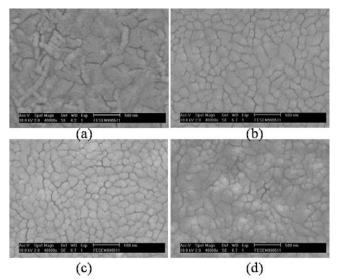

Lower degree of crystallinity, smaller crystalline domains, lower degree of order and lower angle grain boundaries for carriers transport are more helpful in Fig. 2 and 3.

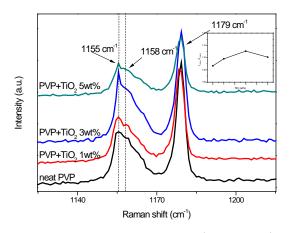

In Fig. 4, the greater the ratio of Pentacene molecules arranged in the direction of the lattice as possible, a better device characteristics of organic thin film transistor.

### 4. Conclusions

Finally, we realized a low leakage current density in the nanocomposite dielectric and high current ratio in the pentacene-TFTs device with top contact structure. These devices exhibited p-channel TFT characteristics with a high field-effect mobility (a saturation mobility of ~0.58 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and a low voltage operation (<6 V) comparable to the spin coating (SPC) process, indicating that these NC-dielectric materials can be used in low-cost and high-performance printable electronics. The fundamental properties of PVP/TiO<sub>2</sub> nanocomposite by inkjet printing and the carrier mobility relation to semiconductor layer films were examined with Raman spectroscopy analysis.

Fig. 1 The plots of I-V characteristics and relation of leakage current and surface roughness to  $TiO_2$  ratio in the MIM structure using nano-composite insulators with various  $TiO_2$  concentrations.

**Fig. 2** Characteristics of  $I_{DS}$ - $V_{DS}$  for pentacene TFTs deposited on the PVP-TiO<sub>2</sub> nanocomposite gate dielectric insulator with different TiO<sub>2</sub> contents: neat PVP (2-point segment line) and 5 wt% (straight line). For both devices, the drain voltage ( $V_{DS}$ ) was swept from 0 to -50 V and the gate voltage ( $V_{GS}$ ) was fixed at 0, -10, -20, -30, -40, and -50 V for each  $V_{DS}$  sweep.

Fig. 3 Microstructure of pentacene films onto composite films by IJP: (a) neat PVP 9 wt%(cross-linked), (b) PVP+TiO<sub>2</sub> 1wt%, (c) +TiO<sub>2</sub> 3wt% and (d) +TiO<sub>2</sub> 5wt%.

Fig. 4 Raman spectrum of 1155 cm<sup>-1</sup>, 1158 cm<sup>-1</sup> and 1179 cm<sup>-1</sup> peak.

#### References

- Gilles Horowitz, Mohammad Mottaghi, Philippe Lang, Fernand Rodriguez, Abderrahim Yassar, Stephane Lenfant, Dominique Vuillaume, Proc. of SPICE 6336 (2006) 63360G-1.

- [2] Wen-Hsi Lee, Chun Chieh Wang, Jia Chung Ho, Thin Solid Films 517 (2009) 5305-5310.

- [3] Wen-Hsi LEE\_, Ching-Chieh WANG, Wei-Ting CHEN, and Jia-Chuong HO, Jpn. J. Appl. Phys., Vol. 47, No. 12 (2008).

- [4] Facchetti, A.; Yoon, M. H.; Marks, T. J. Adv. Mater. 2005, 17, 1705.

- [5] Veres, J.; Ogier, S.; Lloyd, G.; de Leeuw, D. Chem. Mater. 2004, 16, 4543.

- [6] W. Y. Chou, and H. L. Cheng, Adv. Funct. Mater.14, 811 (2004).

#### Acknowledgements

The authors acknowledge the financial support of the National Science Council, R.O.C., under grant NSC99-2627-E-006-003.

#### References

- [1] S. Zaima and M. Hori, Jpn. J. Appl. Phys. 43 (1998) 278.

- [2] S. Zaima, Extended Abstracts of the 1999 International Conference on Solid State Devices and Materials (1999) 737.

- [3] M. Hori and T. Fukui, Advanced Metallization and Interconnect Systems for ULSI Applications (2000) 14.

## Appendix

**Chao-Te Liu** received the B.S. degree from National Sun Yat-sen University, Kaohsiung, Taiwan, ROC in 2007 and the M.S. degree from National Cheng Kung University, Tainan, Taiwan, ROC in 2009, both in electrical engineering. He has been gotten qualification of Ph.D Candidate and started researchs of semiconductor and dielectric ink for flexible electronic application.

E-mail: n28981036@mail.ncku.edu.tw