# Novel Extraction Method for Source and Drain Series Resistances in Silicon Nanowire MOSFETs Based on Radio-Frequency Analysis

Kyung Rok Kim<sup>1</sup>, Sunhae Shin<sup>1</sup>, Seongjae Cho<sup>2</sup>, Jung-Hee Lee<sup>3</sup>, and In Man Kang<sup>3\*</sup>

<sup>1</sup>School of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology,

100 Banyeon-ri, Eonyang-eup, Ulju-gun, Ulsan 689-798, Republic of Korea

<sup>2</sup>Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA

<sup>3</sup>School of Electronics Engineering, Kyungpook National University, 1370, Sankyuk-dong, Buk-gu, Daegu 702-701,

j

Republic of Korea, Phone: +82-53-950-5513, \*E-mail: imkang@ee.knu.ac.kr

## 1. Introduction

The source and drain (S/D) series resistances become critical parameters to model MOSFET characteristics based on nanowire structure. Although S/D series-resistance extraction methods based on a small-signal radio-frequency (RF) analysis have been reported, only planar structure with substrate components [1-3] or off-state bias-independent components [1, 4] have been considered.

In this paper, we propose a novel extraction method for S/D resistances of silicon nanowire (SNW) MOSFETs in consideration of bias-dependent RF components from both *Y*- and *Z*-parameters. The extraction results by our proposed method for the SNW MOSFETs are compared with those by the previous work [2]. The  $Y_{22}$ - and  $Z_{22}$ -parameters generated by HSPICE [5] showed good agreements with those obtained from three-dimensional (3-D) device simulation up to 100 GHz [6].

### 2. RF Model and Extraction Method

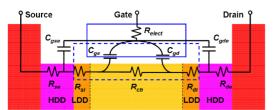

Figure 1 shows an equivalent circuit of an SNW MOSFET device operating in the strong inversion region  $(V_{GS} > V_{th})$  with  $V_{DS} = 0$  V, which results in the negligible transconductance  $(g_m)$  [3]. In this equivalent circuit,  $C_{gs}$  and  $C_{gd}$  are the intrinsic gate-to-source and gate-to-drain capacitance, respectively. Also,  $C_{gse}$  and  $C_{gde}$  are the extrinsic gate-to-source and gate-to-drain capacitance, respectively. The resistance components of  $R_{elect}$  and  $R_{ch}$  are the gate electrode resistance and the channel resistance, respectively. In terms of the S/D resistance,  $R_{si}$  and  $R_{di}$  are the gate bias-dependent S/D series resistances. In addition,  $R_{se}$  and  $R_{de}$ are the gate bias-independent source and drain series resistances. When the device is turned off, the intrinsic gate capacitances can be ignored and the channel resistance increases infinitely owing to the absence of channel charges. Therefore, the  $C_{gs}$ ,  $C_{gd}$ ,  $R_{ch}$ ,  $R_{si}$ , and  $R_{di}$  can be removed from the equivalent circuit model in case of an off-state.

Fig. 1 Equivalent circuit with the cross-sectional view of an SNW MOSFET.

The *Y*-parameters for the simplified equivalent circuit at the turn-off region are derived as following equations:

$$Y_{11} \approx \omega^{2} \left[ R_{elect} \left( C_{gse} + C_{gde} \right)^{2} + R_{se} C_{gse}^{2} + R_{de} C_{gde}^{2} \right]$$

(1)

+  $j\omega \left( C_{gse} + C_{gde} \right)$

$$Y_{12} \approx -\omega^{2} \left[ R_{elect} C_{gde} \left( C_{gse} + C_{gde} \right) + R_{de} C_{gde}^{2} \right] - j\omega C_{gde}$$

(2)

$$Y_{22} \approx \omega^{2} \left( R_{elect} + R_{de} \right) C_{gde}^{2} + j\omega C_{gde}$$

(3)

The capacitances are obtained from the imaginary parts of *Y*-parameters. Also, the equations for the resistance-related components extraction are provided as follows:

$$R_{de} = \frac{C_{gde} \operatorname{Re}(Y_{12}) + (C_{gse} + C_{gde}) \operatorname{Re}(Y_{22})}{\omega^2 C_{ese} C_{ede}^2}$$

(4)

$$R_{elect} = -\frac{\operatorname{Re}(Y_{12}) + \omega^2 R_{de} C_{gde}^2}{\omega^2 C_{gse} (C_{gse} + C_{gde})}$$

(5)

$$R_{se} = \frac{\text{Re}(Y_{11}) - \omega^2 R_{elect} (C_{gse} + C_{gde})^2 - \omega^2 R_{de} C_{gde}^2}{\omega^2 C_{gse}^2}$$

(6)

The extrinsic  $R_{elect}$ ,  $R_{se}$ ,  $R_{de}$ ,  $C_{gse}$ , and  $C_{gde}$  components are independent of gate bias. After de-embedding these values from the small-signal equivalent circuit in Fig. 1(a), the  $Y_{11}$ - and  $Z_{22}$ - parameters can be derived as follows:

$$Y_{11} \approx \omega^{2} \left( \frac{R_{si} R_{di} (C_{gs} + C_{gd})^{2} + R_{ch} (R_{di} C_{gd}^{2} + R_{si} C_{gs}^{2})}{R_{ch} + R_{si} + R_{di}} \right)$$

(7)

+  $j \omega (C_{gs} + C_{gd})$

Re $(Z_{22})_{u^{2} = 0} \approx R_{ch} + R_{si} + R_{di}$  (8)

Since the simulated structure has symmetry about the channel center,  $R_{si}$ ,  $R_{di}$ , and  $R_{ch}$  can be extracted by following equations:

$$R_{si} = R_{di} = \text{Re}(Y_{11}) / (2\omega^2 C_{gs}^2)$$

(9)

$$R_{ch} = \operatorname{Re}(Z_{22})_{m^2 = 0} - (R_{si} + R_{di})$$

(10)

## 3. Results and Discussion

In order to extract the small-signal parameters, both *Y*and *Z*-parameters of SNW MOSFETs up to 100 GHz are obtained from 3-D device simulation [6]. SNW MOSFETs with channel length ( $L_G$ ) of 30 nm have radius ( $R_n$ ) of 5 nm and 10 nm. The doping concentration of n-type lightly doped drain (LDD) region and highly doped drain (HDD) region is  $5 \times 10^{18}$  cm<sup>-3</sup> and  $1 \times 10^{20}$  cm<sup>-3</sup>, respectively.

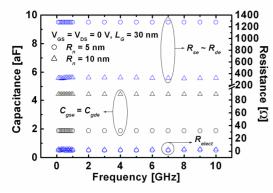

Fig. 2 Small-signal parameters extracted at  $V_{GS} = V_{DS} = 0$  V.

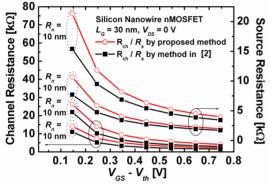

Fig. 3 Resistance components extracted from SNW MOSFETs with different nanowire radius  $(R_n)$  at  $V_{GS} > V_{th}$  with  $V_{DS} = 0$  V.

Figure 2 shows the extracted small-signal parameters as a function of frequency at  $V_{GS} = V_{DS} = 0$  V. The extracted parameters remain almost constant with frequency, which validates the reliability of the proposed method. In this simulation work,  $R_{elect}$  has been kept as negligibly small by using metal gate electrode. The gate-bias independent source resistances of devices with  $R_n = 5$  nm and 10 nm are 1298.8  $\Omega$  and 327.4  $\Omega$ , respectively, which proves that the proposed method is still applicable to the extremely scaled MOSFET devices. Fig. 3 shows the extracted total source series resistances  $(R_s = R_{si} + R_{se})$  and channel resistances  $(R_{ch})$  as a function of gate overdrive voltage  $(V_{GS} - V_{th})$ based on our newly proposed method in comparison with the previous work [2], which always underestimates the nanowire series resistance for all different radius due to substrate components only existing in the planar structure.

In order to evaluate the accuracy of our proposed extraction method for nanowire structure, the  $Y_{22}$ - and  $Z_{22}$ -parameters from 3-D device simulation results have been compared with those from circuit simulation by HSPICE based on the extracted parameters and the proposed small-signal equivalent circuit in Fig. 1. As shown in Fig. 4, the simulation results from an equivalent circuit based on the new extraction method successfully reproduce the 3-D device simulation results up to near 100-GHz. Parameters extracted by the previous method [2], however, show the significant deviations of HSPICE results from 3-D simulation data.

Fig. 4 Comparison of the physical 3-D device simulation data with the schematically modelled  $Y_{22}$ -and  $Z_{22}$ -parameters for a 30 nm SNW MOSFET device.

As shown in Fig. 4, the frequency-independent output impedance ( $\operatorname{Re}(Z_{22})$ ) and admittance ( $\operatorname{Re}(Y_{22})$ ) from the HSPICE simulations based on our method for nanowire structure without substrate parasitic also demonstrated good consistency with the 3-D device simulation results up to 100-GHz at various gate voltages even in the on-states.

#### 4. Conclusions

An analytical method of extracting S/D series resistance of SNW MOSFETs from the RF parameters has been proposed. Our methodology showed higher accuracy for a nanowire than the previous bias-independent method on planar MOSFETs. The schematically modeled *Y*- and *Z*parameters have demonstrated excellent agreements with the 3-D simulation results up to 100-GHz range.

#### Acknowledgements

This work was supported by the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (No. 2011-0005342, 2011-0025701, and 2011-0016222). Dr. S. Cho is supported by the National Research Foundation of Korea Grant funded by the Korean Government (NRF-2011-357-D00155).

#### References

- D. Lovelace, J. Costa, and N. Camilleri, *IEEE MTT-S Int. Microwave Symp. Dig.* (1994) 865.

- [2] R. Torres-Torres, R. S. Murphy-Arteaga, and S. Decoutere, *Electronics Lett.* 39 (2003) 1476.

- [3] E. Torres-Rios, R. Torres-Torres, G. Valdovinos-Fierro, and E. A. Gutierrez, *IEEE Trans. Electron Devices* 53 (2006) 571.

- [4] S. Cho, K. R. Kim, B.-G. Park, and I. M. Kang, *IEEE Trans. Electron Devices* 58 (2011) 1388.

- [5] HSPICE Users Manual (Synopsys, Mountain View, CA, 2009)

- [6] ATLAS Users Manual (SILVACO, Santa Clara, CA, 2009)