# High Performance Normally Off Nanochannel Al<sub>2</sub>O<sub>3</sub>/GaN FinFET

Ki-Sik Im<sup>1</sup>, Ki-Won Kim<sup>1</sup>, Dong-Seok Kim<sup>1</sup>, Hee-Sung Kang<sup>1</sup>, Young-Woo Jo<sup>1</sup>, Ryun-Hwi Kim<sup>1</sup>, Chul-Ho Won<sup>1</sup>, Kyu-Il Jang<sup>1</sup>, Mi-Kyung Kwon<sup>1</sup>, Sang-Min Jeon<sup>1</sup>, Dong-Hyeok Son<sup>1</sup>, Yoo-Mi Kwon<sup>1</sup>, Jae-Hoon Lee<sup>2</sup>, and Jung-Hee Lee<sup>1</sup>

Kyungpook National University<sup>1</sup>, School of Elec. Eng. and Com. Sci., 1370, Sankyuk-dong, Buk-gu, Daegu, 702-701, Samsung LED Co., Ltd.<sup>2</sup>, GaN Power Research Group, Suwon, 443-743, Republic of Korea Phone: +82-53-940-8655 E-mail: jlee@ee.knu.ac.kr

## 1. Introduction

Recently, excellent device performances have been demonstrated in AlGaN/GaN-based FinFETs with nanowire structures [1]-[4]. The reason for the high performances is because a 3-dimensional gate configuration greatly improves the gate controllability when the dimension becomes nanosized, as already proven from the 3-D Si devices which have similar structures. For examples, T. Zimmermann *et al.* [2] and B. Lu *et al.* [3] showed that very low subthreshold slope (SS) of and high maximum drain current ( $I_{d,max}$ ) can be obtained from these nanostructure devices including normally-off operation.

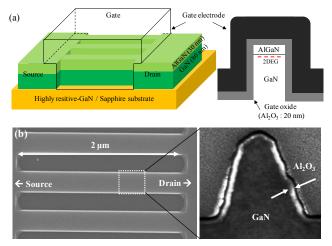

In this work, we have fabricated and characterized normally-off GaN FinFETs (Fig. 1(a)) with sub nanometer-sized width and high quality ALD Al<sub>2</sub>O<sub>3</sub> layer as gate dielectric. The fabricated Al<sub>2</sub>O<sub>3</sub>/GaN FinFET exhibited positive V<sub>th</sub> and enhanced device performances, compared to the conventional planar-type AlGaN/GaN-based normally-off devices [5]-[8].

## 2. Growth and device fabrication

The AlGaN/GaN heterostructure was grown by metal-organic chemical vapor deposition (MOCVD), which consists of 2 µm-thick highly resistive GaN layer, 80 nm-thick undoped GaN layer, and 30 nm-thick Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer in growth sequence on sapphire substrate. The measured 2-DEG density and mobility of the AlGaN/GaN heterointerface were  $8.8 \times 10^{12}$  cm<sup>-2</sup> and 1500 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, respectively.

For device isolation, the nanoribbon-shaped active region of the device was patterned by electron-beam lithography using hydrogen silsesquioxane (HSQ) and defined by transformer-coupled plasma-reactive ion etching using a BCl<sub>3</sub>/Cl<sub>2</sub> gas mixture. Surface treatment was directly followed in TMAH solution (25% solution at 85 °C) to smooth the surface and to remove the plasma damage from the etched GaN surface [6]. A 20 nm-thick Al<sub>2</sub>O<sub>3</sub> gate insulator layer was then deposited by ALD. After contact hole opening for the source and drain, Ti/Al/Ni/Au was deposited using an electron-beam evaporator, followed by rapid thermal annealing at 900 °C for 30 s in nitrogen ambient. Finally, Ni/Au was deposited as the gate metal. The schematic configuration of the proposed Al<sub>2</sub>O<sub>3</sub>/GaN FinFET with 60 nm width is shown in Fig. 1(a). The wide source/drain is contacted to the 2-DEG formed at AlGaN/GaN heterointerface to achieve low series resistance. Due to sloped profile of masking resist, the AlGaN layer on the top of the nanochannel tends to be etched away from the side edges. Images of the scanning electron microscopy and the cross-sectional transmission electron microscopy in Fig. 1(b) clearly show that the top surface of the nanoribbon with a sloped height of 150 nm becomes rounded and its width, space, and fin number is 60 nm, 500 nm, and 3, respectively.

Fig. 1. (a) Three-dimensional schematic view of the proposed Al<sub>2</sub>O<sub>3</sub>/GaN FinFET (20 nm Al<sub>2</sub>O<sub>3</sub> is not shown in left image). The gate metal overlapped the active region with ~ 0.5  $\mu$ m and the total gate length is 3  $\mu$ m. The right figure is cross-sectional illustration of AlGaN/GaN FinFET below the gate region. (b) Top-view SEM image of a mesa-etched fin before deposition of gate metal and corresponding cross-sectional TEM image.

## 3. Results and Discussion

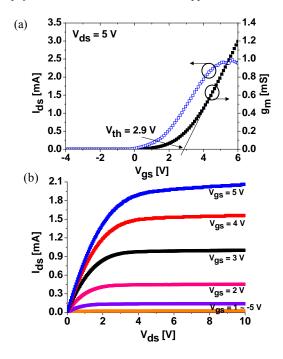

Fig. 2 shows the dc characteristics of the GaN FinFET with gate length of 2  $\mu$ m. As shown in Fig. 2(a), the fabricated device exhibits normally-off operation with V<sub>th</sub> of 2.9 V at V<sub>ds</sub> = 5 V, which defines the V<sub>th</sub> as the gate bias intercept of the extrapolation of drain current at the point of peak g<sub>m</sub>. The reason for normally-off operation is because the width of the 2-DEG channel on the top of the nanoribbon was greatly reduced, as discussed before, and the strain relaxation on the edge of nano-sized structure weakens the piezoelectric polarization which leads to the reduction of electron density in the top 2-DEG channel [4]. Furthermore, the negative effective oxide charge at the interface between Al<sub>2</sub>O<sub>3</sub> gate insulator and GaN (or AlGaN)

surface pushes the V<sub>th</sub> even positively higher [7]-[8]. The device exhibits a maximum drain current  $(I_{d,max})$  of 3 mA and a maximum transconductance  $(g_m)$  of 1 mS at  $V_{gs}$  = 6 V and  $V_{ds} = 5$  V. The normalized  $I_{d,max}$  and  $g_m$ , divided by the total gate width (sum of width and two heights for the nanochannel multiplied by the number of fin;  $(60 + 2 \times 150)$ nm)  $\times$  3), are 2.7 A/mm and 880 mS/mm, respectively, which are much higher than the results obtained from the conventional planar type devices and these are the highest values obtained from AlGaN/GaN-based HFETs ever reported [5]-[8]. The on-resistance of the device was estimated to be as low as 0.1 m $\Omega$ ·cm<sup>2</sup> from Fig. 2(b). These superior on-state performances are because the nanoribbon structure improves the gate controllability, and probably the remaining top 2-DEG channel serves as one of the current channels. In addition, the AlGaN/GaN heterojunction of wide source and drain at the overlapped gate region can supply many electrons to the nanochannels increase the high device performances.

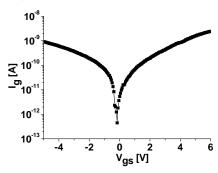

Fig. 3 shows that the gate leakage currents are only  $10^{-9}$  A at  $V_{gs} = -5$  V, which is very low even though the thickness of the Al<sub>2</sub>O<sub>3</sub> gate dielectric layer is only 20 nm. This result clearly demonstrates that the quality of the thin ALD Al<sub>2</sub>O<sub>3</sub> layer deposited in this work is excellent.

#### 3. Conclusions

Normally-off Al<sub>2</sub>O<sub>3</sub>/GaN FinFET with threshold voltage as high as 2.9 V, which is very promising for power switching applications, has been successfully demonstrated. The reason for normally-off operation is because the strain relaxation on the edge of nano-sized structure leads to the electron depletion in the top 2-DEG channel with reduced width and the negative effective gate oxide charge further increases the V<sub>th</sub> even higher. The device exhibits superior on-state performances such as maximum current density of 2.7 A/mm and maximum  $g_m$  of 880 mS/mm. This is because the nanoribbon structure improves the gate controllability and the remaining top 2-DEG channel serves as one of the current channels. In addition, the AlGaN/GaN heterojunctions of source and drain with large areas at the overlapped gate region can supply many electrons to the nanochannels.

#### Acknowledgements

This work was supported by Kyungpook National University Research Fund 2012, 2008 Brain Korea 21 (BK21), the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST) (No. 2012-0005671, 2012-0000627), R&D program of MKE/KETEP (2011101050017B, 'Development of high efficiency GaN power device for an power grid inverter system'), and WCU (World Class University) program through the Korea Science and Engineering Foundation funded by the Ministry of Education, Science and Technology (R33-10055), and the IT R&D program of MKE/KEIT (10038766, Energy Efficient Power Semiconductor Technology for Next Generation Data Center).

#### References

- K. Ohi and T. Hashizume, *Jpn. J. Appl. Phys.*, vol. 48, no. 8, pp. 081002, Aug. 2009.

- [2] T. Zimmermann, Y. Cao, X. Luo, D. Jena, and H. Xing, in Proc. 67th Annu. Device Res. Conf., Dec. 2009, pp. 129-130.

- [3] B. Lu, E. Matioli, and T. Palacios, *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 360-362, Mar. 2012.

- [4] S. Liu, Y. Cai, G. Gu, J. Wang, C. Zeng, W. Shi, Z. Feng, H. Qin, Z. Cheng, C. Chen, and B. Zhang, *IEEE Electron De*vice Lett., vol. 33, no. 3, pp. 354-356, Mar. 2012.

- [5] K.-S. Im, J.-B. Ha, K.-W. Kim, J.-S. Lee, D.-S. Kim, S.-H. Hahm, and J.-H. Lee, *IEEE Electron Device Lett.*, vol. 31, no. 3, pp. 192-194, Mar. 2010.

- [6] K.-W. Kim, S.-D. Jung, D.-S. Kim, H.-S. Kang, K.-S. Im, J.-J Oh, J.-B. Ha, J.-K. Shin, and J.-H. Lee, *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1376-1378, Oct. 2011.

- [7] Y. Hori, C. Mizue, and T. Hashizume, "Interface state characterization of ALD-Al<sub>2</sub>O<sub>3</sub>/GaN and ALD-Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN structures," phys. Status Solidi C, vol. 9, no. 6, pp. 1356-1360, Jun. 2012.

- [8] T. Marron, S. Takashima, Z. Li, and T. P. Chow. "Impact of annealing on Al<sub>2</sub>O<sub>3</sub> gate dielectric for GaN MOS devices." phys. Status Solidi C, vol. 9, no. 3-4, pp. 907-910, Mar. 2012.

Fig. 2. (a) Transfer curve of the fabricated nanochannel triple-gate  $Al_2O_3/GaN$  MISFET at  $V_{ds}$  = 5 V and (b)  $I_{ds}$  -  $V_{ds}$  characteristics with  $L_g$  of 2 µm.

Fig. 3. The gate leakage characteristic of the fabricated nanochannel triple-gate  $Al_2O_3/GaN$  MISFET.