# **Advanced SiC Devices with Trench Structure**

Takashi Nakamura, Masatoshi Aketa, Yuki Nakano

New Material Devices R&D Center, ROHM Co., Ltd. 21Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan E-mail: takashi.nakamura@dsn.rohm.co.jp

## 1. Introduction

This paper presents next generation Silicon Carbide (SiC) trench structure Schottky diodes, and trench MOS-FETs. SiC Schottky diodes, with newly developed trench structures, successfully showed lower forward voltage than conventional SiC diodes while keeping leakage current at an acceptable level. The developed SiC MOSFETs with a double-trench structure have improved reliability of the device while maintaining ultra low on-resistance due to the fact that the new structure effectively reduced the highest electric field at the bottom of the gate trench, preventing gate oxide breakdown.

## 2. SiC Trench Structure Schottky Diodes

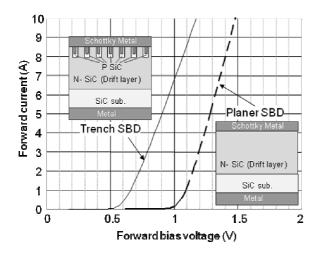

SiC Schottky diodes are attractive devices to reduce switching losses in high voltage applications such as Power Factor Correction (PFC) [1,2]. The reduction of conductive losses is also required to improve efficiency. However, SiC Schottky diodes have higher forward voltage drop when compared to silicon PN junction diodes. We have proposed the trench structure Schottky diodes to obtain a lower forward voltage drop while maintaining the same leakage current. Trench p region can suppress the concentration of electric field at the Schottky interface. The threshold voltage of the trench structure is 0.48 V smaller than that of the planar structure. The smaller threshold voltage can reduce the conductive losses during forward current operation.

Fig.1 Forward Characteristics of planer SBD and trench SBD

## 3. SiC Double-Trench MOSFETs

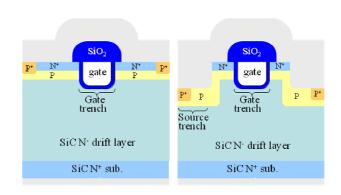

SiC trench MOSFETs can have lower conductive losses when compared with planar MOSFETs because planar MOSFETs have JFET regions which increase the on-resistance [3,4]. We previously reported 790 V SiC trench MOSFETs with the lowest  $R_{on}$  at room temperature. However, the trench MOSFETs had issues regarding oxide breakdown at the trench bottom during high drain-source voltage application. To resolve issue of gate oxide breakdown, double-trench MOSFET structure, which has both source and gate trenches, was developed. The device structures for the single and double-trench structures are shown in Fig.2 (a) and (b), respectively.

Fig.2 Schematic cross section of (a) conventional single-trench structure and (b) double-trench structure with source trench and gate trench.

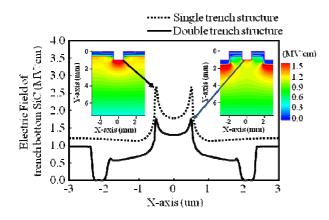

To suppress electric field at the gate oxide bottom, the source trench is fabricated deeper than gate trench. Deeper source trenches prevent the concentration of electric fields at the bottom of the gate trench. Fig.3 shows drain-source bias simulation results of the electric field distribution at 600V and with a gate-source voltage of 0V. Epitaxial layers were 7 $\mu$ m thick with a doping concentration of 7.5 x 10<sup>15</sup> cm<sup>-3</sup>. The highest electric field at the bottom of the gate trench of the single-trench structure was 2.66 MV/cm. On the other hand, that of double-trench structure was 1.66 MV/cm. This structure succeeds in preventing the destruction of oxide at the bottom of the gate trench.

Fig.3 Drain-source bias simulation results at 600V in gate-source voltage 0V.

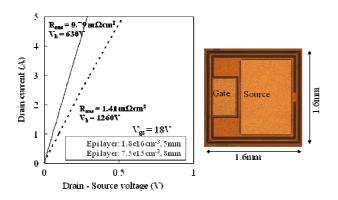

Fig.4 shows the characteristics of the trench MOSFETs using two different epilayers. The Ron,sp of these was estimated at 0.79 m $\Omega$ cm<sup>2</sup> (V<sub>B</sub>=600V class) and 1.41m $\Omega$ cm<sup>2</sup> (V<sub>B</sub>=1200V class), respectively. We could achieve ultra low on-resistance while maintaining the high reliability of the gate oxide.

Fig.4 Id – Vds characteristics of double-trench MOSFETs when Vgs = 18 V. The chip size is 1.6 mm x 1.6 mm. Active area is  $0.01422 \text{ cm}^2$ .

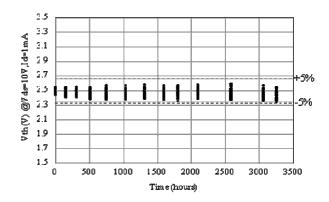

The stability of Vth (Threshold Voltage) during negative gate bias conditions is also an important issue for SiC MOSFETs. Fig.14 shows the time dependence of Vth with a constant negative gate bias of Vgs = -18 V at 150 °C. The number of test devices was 22. Vth was considerably stable and the change rate was less than 5% after 3000 hours.

Fig.5 The time dependence of Vth in the constant negative gate bias of Vgs = -18 V at 150 °C. The number of test device was 22 pcs. Device size was  $1.2 \times 2.4$  mm<sup>2</sup>.

#### 3. Conclusions

The two devices presented in this paper, SiC Trench Structure Diode and MOSFET, demonstrate significant performance improvements over conventional devices. In the case of the diode, the incorporation of a trench structure allows a reduction in leakage current with a minimal increase in on-resistance. This is accomplished by reducing the electric field at the Schottky interface without altering the drift layer by extending trenches into the p-type region where high electric fields are experienced. The double-trench MOSFET fabricated, with its lack of a JFET region, achieves class-leading low on-state resistance. By utilizing this trench structure, problems associated with oxide destruction were eliminated by reducing the electric field at the gate bottom.

#### Acknowledgements

We would like to special thanks to Prof. Kimoto, Kyoto University for technical discussions and advices.

#### References

- [1] R. Rupp and I. Zverev, Materials Science Forum 443-436 (2003) 805

- [2] M. Treu, R. Rupp, C. S. Tai, P. Blaschitz, J. Hilsenbeck, H. Brunner, D. Peters, R. Elpelt and T. Reimann, Materials Science Forum 527-529 (2006) 1155.

- [3] H. Nakao, H. Mikami, H.Yano, T. Hatayama, Y. Uraoka and T. Fuyuki, Mater. Sci. Forum 527-529 (2006) 1293.

- [4] H. Yano, H. Nakao, T. Hatayama, Y. Uraoka and T. Fuyuki, Mater. Sci. Forum 556-557 (2007) 807.