# Fabrication of ZrSiO/Ge Gate Stacks with GeO<sub>2</sub> and ZrGeO Interlayers

Shuta Kojima<sup>1</sup>, Keita Sakamoto<sup>1</sup>, Yoshiaki Iwamura<sup>1</sup>, Kana Hirayama<sup>1</sup>, Keisuke Yamamoto<sup>1, 3</sup>, Dong Wang<sup>1</sup>, and Hiroshi Nakashima<sup>2</sup>

Interdisciplinary Graduate School of Engineering Sciences, Kyushu University

6-1 Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan

Phone: +81-92-583-8924, Fax: +81-92-573-8729, E-mail: kojima1@asem.kyushu-u.ac.jp

Art, Science and Technology Center for Cooperative Reserch, Kyushu University

6-1 Kasuga-koen, Kasuga, Fukuoka 816-8580, Japan

<sup>3</sup>Resach Fellow of the Japan Society for the Promotion of Science

### 1. Introduction

Ge is of great interest as a candidate channel material for future CMOS devices due to its higher intrinsic carrier mobility. To realize Ge-CMOS technology, one of the most challenging issues is formation of a good high-k gate stack, and both thin EOT less than 1.0 nm and low  $D_{\rm it}$  less than  $1\times 10^{11}~{\rm cm}^{-2}~{\rm eV}^{-1}$  are mandatory. Recent studies on high-k/Ge gate stacks have rapidly progressed. For an example, the gate stacks fabricated using an ECR plasma postoxidation through a thin  ${\rm Al}_2{\rm O}_3$  showed a EOT of approximately 1.0 nm and a  $D_{\rm it}$  of lower than  $1\times 10^{11}~{\rm cm}^{-2}{\rm eV}^{-1}$  near the midgap.  $^{1)}$

Our group has proposed a method for electrical passivation of a Ge surface by an ultrathin  $\mathrm{SiO_2/GeO_2}$  bilayer and achieved high-quality interface with a  $D_{it}$  of  $1\times10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> near the midgap.<sup>2, 3)</sup> By using this bilayer passivation (BLP), we fabricated n- and p-MOSFETs on Ge (100) substrates and demonstrated the high electron and hole mobilities of 1097 and 376 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, respectively.<sup>4)</sup> However, EOT of the  $\mathrm{SiO_2}$  gate stack used in the MOSFET fabrication was approximately 50 nm, although EOT of  $\mathrm{GeO_2}$  interlayer (IL) was less than 2 nm. In order to enhance the current drivability, EOT should be decreased.

In this study, we fabricated ZrSiO/Ge high-k gate stack with GeO<sub>2</sub> IL and ZrGeO IL. The structural and electrical properties of these gate stacks are presented.

## 2. Experimental Procedure and Structural Analysis

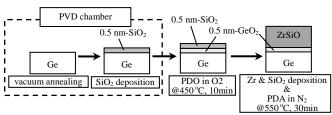

A p-type (100) Ge with a resistivity of 0.2  $\Omega$ cm was used. Fabrication process flow for high-k gate stack with GeO<sub>2</sub> IL is shown in Fig. 1. First, sacrificial oxidation was done at 450°C for 30 min by dry oxidation, followed by loading in a physical vapor deposition (PVD) camber for BLP. After volatilization of GeO<sub>2</sub> by vacuum annealing, a 0.5 nm-thick SiO<sub>2</sub> was deposited on the Ge surface at 350°C using magnetron sputtering from a SiO<sub>2</sub> target

Fig. 1. Fabrication process flow of Ge-MOS capacitor with structure of ZrSiO/GeO<sub>2</sub>-IL/Ge.

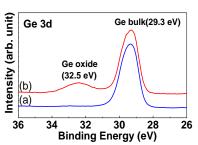

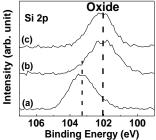

without the addition of O<sub>2</sub>. Then, postdeposition oxidation (PDO) was done at 450°C for 10 min in dry O<sub>2</sub>. It was confirmed from XPS that a GeO<sub>2</sub> layer grows during PDO, as shown in Fig. 2. Furthermore, the cross sectional TEM analysis suggested that the GeO<sub>2</sub> thickness was 0.5 nm. On the sample with 0.5 nm-thick SiO<sub>2</sub>/0.5 nm-GeO<sub>2</sub>/Ge structure, 2 nm-thick Zr film was deposited using magnetron sputtering at room temperature (RT), followed by the deposition of 0.45 nm-thick SiO<sub>2</sub> with the addition of O<sub>2</sub>. The XPS results of samples before and after the SiO<sub>2</sub>/Zr depositions are shown in Fig. 3, indicating that the Si 2p core level of a sample with the SiO<sub>2</sub>/Zr depositions shifted by 1.0 eV to lower binding energy relative to SiO<sub>2</sub>. This implies that Zr reacts with SiO<sub>2</sub> during the sputter depositions, resulting in the formation of Zr silicate (ZrSiO).<sup>5)</sup> After the depositions, PDA was performed at 550°C for 30 min in N<sub>2</sub>. Then, Al/TiN metal-gate process in Ref. 3 was done, which were the deposition of a TiN film, PMA at 450°C for 20 min, the evaporation of Al, the electrode patterning with an area of  $2.25 \times 10^{-4}$  cm<sup>2</sup>, and the contact annealing at 350°C for 10 min.

Fig. 2. Ge 3d XPS spectra for 0.5 nm-thick SiO<sub>2</sub> deposited sample. (a) and (b) are the results before and after PDO at 450°C for 10 min, respectively.

Fig. 3. Si 2p XPS spectra of samples (a) before and (b) after the SiO<sub>2</sub>/Zr depositions. The spectrum (c) represents after PDA at 550°C for 30 min.

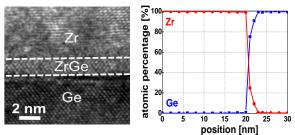

Fig.4 TEM and EDX results for the sample deposited with Zr on Ge.

The fabrication of high-k gate stack with ZrGeO IL is simple. A 2 nm-thick Zr film was directly deposited on Ge surface at RT using sputtering. It was confirmed from TEM and EDX analyses that Zr reacts with Ge, resulting in the formation of Zr germanide (ZrGe) during the sputtering, as shown in Fig. 4. The TEM analysis showed the thickness of ZrGe layer was approximately 2 nm. Then, 0.7 nm-thick SiO<sub>2</sub> film was deposited with the addition of O<sub>2</sub> at RT, and PDA was done at 500°C for 30 min in N<sub>2</sub>. Finally, Al/TiN metal-gate process was performed.

#### 3. Results and Discussion

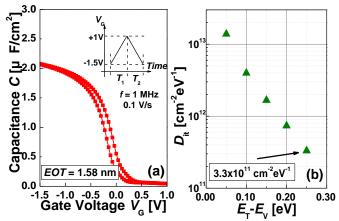

Figure 5 (a) shows the  $C-V_G$  characteristics for high-kgate stack with GeO2 IL. The EOT, hysteresis (HT), flat band voltage  $(V_{\rm fb})$ , and leakage current density  $(J_{\rm leak})$  at  $V_{\mathrm{fb}}$ -1 V are summarized in Table 1. The EOT of 1.6 nm is in good agreement with the estimation value (1.6 nm) using the permittivities and thicknesses of ZrSiO and GeO<sub>2</sub> layers (12 and 5.7, 4.0 and 0.5 nm). The  $J_{\text{leak}}$  was  $5\times10^{-4}$  Acm<sup>-2</sup>, which is 4 orders of magnitude lower than that of SiO<sub>2</sub> with the same EOT. The energy distribution of  $D_{it}$  is plotted in Fig. 5(b), which was measured using DLTS. The  $D_{\rm it}$  distribution is similar to that of GeO<sub>2</sub>/Ge,<sup>6)</sup> implying that GeO<sub>2</sub> played a role of IL. Thus, a capacitor with an EOT of 1.6 nm and a  $D_{it}$  of  $3\times10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> near the midgap could be successfully fabricated. However, EOT is still thick to satisfy the requirement of high-k gate stack. We chose ZrGeO as an alternative high-k IL.

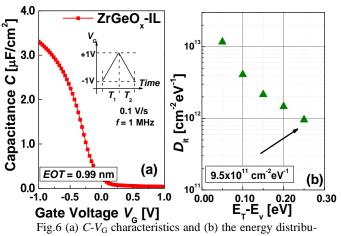

Figure 6 (a) show the  $C-V_G$  characteristics for high-k gate stack with ZrGeO IL. The EOT, HT,  $V_{\rm fb}$ , and  $J_{\rm leak}$  at  $V_{\rm fb}$ -1 V are summarized in Table 1. An EOT of 0.99 nm

Fig.5 (a) C-V<sub>G</sub> characteristic and (b) the energy distribution of  $D_{it}$  for high-k gate stack with GeO<sub>2</sub> IL.

could be achieved, which maybe originated from an increase in ZrSiO permittivity due to a decrease in Si content and higher permittivity of ZrGeO IL. The  $J_{leak}$  was as low as  $2\times10^{-1}$  Acm<sup>-2</sup> for an EOT of 0.99 nm, which is 4 orders of magnitude lower than that of  $SiO_2$ . Thus, the high-k gate stack fabricated in this study is a candidate as a gate stack towards embodying EOT less than 1.0 nm. Furthermore, the well-behaved C-V<sub>G</sub> curve means that ZrGeO played a role of IL. The energy distribution of  $D_{it}$  is plotted in Fig. 6(b). The  $D_{it}$  near the midgap is higher than that with  $GeO_2$ , but the  $D_{it}$  near the valence band is comparable. Considering an extremely low EOT of around 0.5 nm needed for future CMOS, IL should be composed by high-k materials. Although the  $D_{it}$  is still high, further decrease in  $D_{it}$  would be possible by combining the present gate stack fabrication technique with the strict surface cleaning technique.

#### 4. Conclusion

We fabricated ZrSiO/Ge gate stacks with two kinds of IL, which were ultrathin GeO<sub>2</sub> and ZrGeO. The MOS capacitor with  $GeO_2$ -IL showed EOT=1.6 nm and  $D_{ii}$ = 3.3×10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> near the midgap. The MOS capacitor with ZrGeO IL showed EOT of 0.99 nm and  $D_{it}$ =9.5×10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>. The  $J_{leak}$  for both capacitors were 4 orders of magnitude lower than that of SiO<sub>2</sub> with the same EOT.

#### References

[1]R. Zhang et al., IEEE Trans. Electron Devices 59 (2012) 335.

[2]K. Hirayama et al., Jpn. J. Appl. Phys. **50** (2011) 04DA10.

[3]H. Nakashima et al., Appl. Phys. Lett. 98 (2011) 252102.

[4]K. Yamamoto et al., Appl. Phys. Express 4 (2011) 051301.

[5]H. Watanabe, Appl. Phys. Lett. 81 (2002) 4221.

[6]H. Matsubara et al., Appl. Phys. Lett. 93 (2008) 032104.

Table. 1. EOT and HT,  $V_{\rm fb}$ ,  $J_{\rm leak}$  obtained from C-V<sub>G</sub> and J-V<sub>G</sub> characteristics. (a)GeO<sub>2</sub>-IL (b)ZrGeO<sub>y</sub>-IL

|                                                                        | (a)GCO <sub>2</sub> -IL | (b)ZrGcO <sub>X</sub> -iE |

|------------------------------------------------------------------------|-------------------------|---------------------------|

| EOT[nm]                                                                | 1.58                    | 0.99                      |

| HT[mV]                                                                 | 133                     | 85                        |

| $V_{ m fb}[{ m V}]$                                                    | 0.13                    | 0.06                      |

| $J_{\text{leak}}[\text{A/cm}^2]@\text{V}_{\text{fb}}\text{-}1\text{V}$ | $4.7 \times 10^{-4}$    | $2.2 \times 10^{-1}$      |

tion of  $D_{it}$  for high-k gate stack with ZrGeO IL.