# Extraction of Carrier Concentration and Mobility of Heavily Doped Poly-Si Nanowires with Junctionless (JL) Transistor Structures

Zer-Ming Lin<sup>a</sup>, Horng-Chih Lin<sup>a,b,\*</sup>, and Tiao-Yuan Huang<sup>a</sup>

<sup>a</sup> Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University,

No. 1001, Ta Hsueh Rd., Hsinchu, Taiwan 300, R.O.C.

<sup>b</sup>National Nano Device Laboratories, No. 26, Prosperity Rd. I, Science-Based Industrial Park, Hsinchu, Taiwan 30078, R.O.C.

\*Phone: +886-3-571-2121 ext. 54193, Fax: +886-3-572-4361, E-mail: <u>hclin@faculty.nctu.edu.tw</u>

### **1. INTRODUCTION**

Recently, transistors with junctionless (JL) scheme have been demonstrated for logic [1] and memory device applications [2]. Such a scheme is also very promising for construction of 3D poly-Si-based devices [3] and circuits since it can greatly simplify the processing by eliminating the implant steps. However, few approaches are available for probing some of the important characteristics, such as carrier concentration and mobility, in the tiny but heavily doped nanowire (NW) channels. In this study, we propose a very simple methodology which only involves the measurements of I-V characteristics of a JL device built with poly-Si NW channels and gate-all-around (GAA) configuration.

### 2. DEVICE STRUCTURE AND CHARACTERISTICS

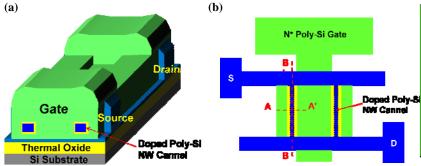

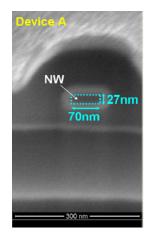

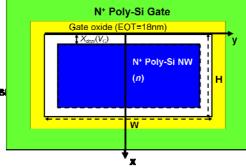

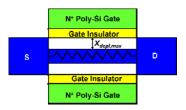

Figs. 1(a) and (b) show the 3D schematic structure and top view, respectively, of the GAA JL poly-Si NW devices characterized in this study. As shown in Fig. 1(a), the GAA JL TFT features two embedded heavily phosphorous-doped poly-Si NWs serving as the conduction channel. Details of the process flow can be seen in our previous work [3]. Note that the *in situ* doped n<sup>+</sup> poly-Si NW structure was prepared with an LPCVD process. Two splits of devices with different cross-sectional NW dimensions were characterized. The first group, denoted as "Device A", has a larger cross-sectional area of 70×27 nm<sup>2</sup>, as can be seen from the cross-sectional scanning electron microscopic (SEM) image shown in Fig. 2. The other group features a NW with cross-sectional area of around 23×12 nm<sup>2</sup>. Its cross-sectional SEM image can be found in our previous work [3].

Fig. 3 shows the great impact of the NW dimensions on the  $I_D$ -V<sub>G</sub> characteristics of the devices. By reducing the cross-sectional area of the NW channels, good switching ability and high on/off current ratio can be achieved. On the other hand, although Device A cannot be effectively turned off because of its large cross-sectional area, its transfer characteristics can be cleverly utilized to extract the active doping concentration and mobility of the *in situ* phosphorous-doped poly-Si NWs with theoretical analysis and measurement procedure stated below.

## **3. EXTRACTION OF CARRIER CONCENTRATION AND MOBILITY**

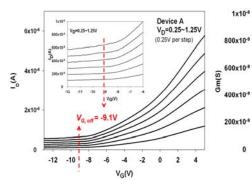

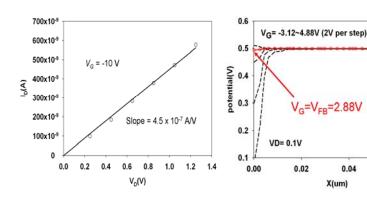

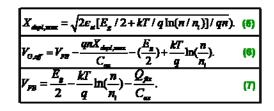

First, we detail the theoretical background of the methodology. Fig. 4 schematically shows the cross-sectional structural parameters of the device along line A-A' shown in Fig. 1(b). Owing to the rather thick structure and the heavy channel doping, the investigated Device A is partially depleted during the off-state operation and the depletion width, X<sub>depl</sub>, is expected to be much smaller than either H or W. Therefore, 1D Poisson's Equation is suitable for calculating the electric potential. The analytical solution of electric potential and the necessary boundary conditions applied to the 1D Poisson's Equation are summarized in Table. I. With the analytical solution of electric potential, the maximum depletion width  $(X_{depl,max})$  and the gate voltage  $(V_{G,off})$  as  $X_{depl,max}$  is reached can be evaluated. Expressions of the derived  $X_{depl,max}$ ,  $V_{Goff}$  as well as flat-band voltage (V<sub>FB</sub>) are summarized in Table II. As V<sub>G</sub> is smaller than V<sub>Goff</sub>, X<sub>depl.max</sub> is reached and maintained. Meanwhile, the conduction current through the core neutral region is no longer affected by the applied V<sub>G</sub>. Namely, the transfer characteristics of the JL transistors switch from "gated resistor" to "ungated resistor", as schematically shown in Fig. 5. As X<sub>depl,max</sub> is reached, the conduction area of the ungated resistor is equal to the cross-sectional area of NW minus the area of the depletion region. Table III summarizes the expression of the conduction area and the resistance of the device as operated in the "ungated resistor" regime. The above inference and prediction are confirmed with the I<sub>D</sub>-V<sub>G</sub> curves measured at V<sub>D</sub> ranging from 0.25 to 1.25 V shown in Fig. 6(a) in which we can see that two distinct regions can be distinguished. Results of the transconductance (G<sub>m</sub>) as a function of V<sub>G</sub> are shown in Fig. 6(b). Since  $G_m$  is the differentiation of  $I_D$  to  $V_G$ , it suddenly drops to zero when the device is switched from gated- to ungated-resistor behavior. V<sub>Goff</sub> can thus be extracted in the figure as the  $V_G$  when  $G_m$  drops to zero, which is -9.1 V in this case. Moreover,  $V_{\text{FB}}$ , which is equal to 2.88V, can also be determined as the V<sub>G</sub> corresponding to the G<sub>m</sub> peaks in Fig. 6(b) [4]. With the value of  $V_{G, off}$  and  $V_{FB}$  applied to Eqs. 6 and 7 (Table II), the active doping concentration (n) and fixed charges  $(Q_{fix})$  can be evaluated and the results are  $1.18 \times 10^{19} \text{ cm}^{-3}$  and  $-3.25 \times 10^{12}$  cm<sup>-2</sup>, respectively. To extract mobility ( $\mu$ ), I<sub>D</sub> in Fig. 6(a) measured at V<sub>G</sub>=-10V is shown as a function of V<sub>D</sub> in Fig. 7. It can be seen that the current is proportional to  $V_D$  and its slope, which is equal to 1/R, is  $4.5 \times 10^{-7}$  ( $\Omega^{-1}$ ). Based on the result and Eq. 9 (Table III), the mobility is determined to be 52.5 cm<sup>2</sup>/V-sec. Finally, it is worthy to make some careful checks to confirm the accuracy of the extracted parameters. First, by applying the extracted carrier concentration to Eq. 5, the estimated  $X_{depl,max}$  is around 11nm, which is indeed smaller than H(=27nm) and W(=70nm). Second, by applying the extracted parameters to a TCAD simulation tool, the electric potential across the middle of the NW along the y-direction (see Fig. 4) under various V<sub>G</sub> conditions can be calculated and the results are shown in Fig. 8. It can be seen that the electric potential is almost flat at V<sub>G</sub>=2.88V, confirming the feature of flat-band condition. This result supports the accuracy of the methodology in extracting V<sub>FB</sub>.

### 4. CONCLUSION

A very clever and simple procedure for extracting the carrier concentration, mobility, and interface fixed charge density of *in situ* phosphorous-doped poly-Si NWs is conceived and demonstrated. The principle of the methodology mainly relies on the switching of operation of a GAA JL device from gated to ungated mode. The scheme can be readily implemented in the manufacturing and characterization of future poly-Si based 3-D devices.

Acknowledgment –The authors would like to thank NDL for assistance in device fabrication. This work was supported in part by the National Science Council of the Republic of China (ROC) under contract NSC No. NSC 99-2221-E-009 -167 -MY3.

### References

- [1] J. P. Colinge et al., Nat. Nanotechnol., Vol. 5, p.225 (2010).

- [2] H. T. Lue et al., in VLSI Symp. Tech. Dig., Jun. 2008, pp. 140-141.

- [3] C. J. Su, et al., IEEE Electron Device Lett., vol.32, p.521 (2010).

- [4] Z.-M. Lin, H.-C. Lin, and T-Y. Huang, submitted to the IEEE T-ED.

Fig. 1 (a) Stereo and (b) top views of the fabricated GAA JL poly-Si NW transistors.

10-

10

10-

10-

10-9

10-1

10-12

10-13 10-14 10-15 -4

-3

cross-sectional area.

Device A

V<sub>D</sub>=0.25~1.25V

(0.25V per step)

-12 -10 -8

=-9.1 \

-6 -4 -2 0 2

VG(V)

-2

-1  $V_{G}(V)$

Fig. 3 Comparisons of I<sub>D</sub>-V<sub>G</sub> characteristics

for two devices featuring NWs with different

I<sub>b</sub>(A) 10-1 12x23 nm<sup>2</sup> (Ref. [3])

27x70 nm<sup>2</sup> (Device A)

V<sub>D</sub>=0.1,1V

1

V<sub>FB</sub>=2.88V

4

2

L<sub>g</sub>=5um

0

Fig. 2 Cross-sectional SEM image of Device A along line AA' shown in Fig. 1(b).

Fig. 6 (a) Transfer characteristics of Device A as a function of  $V_{D.}$  (b) Gm versus V<sub>G</sub> measured at various V<sub>D</sub>.

Fig. 7 I<sub>D</sub> extracted from Fig. 6(a) at  $V_{G}$ =-10V as a function of  $V_{D}$ .

Fig. 8 Simulated electric potential distributions in the middle of the NW along y-axis at V<sub>D</sub>=0.1V and various V<sub>G</sub>.

X(um)

Fig. 4 Schematic illustration of the cross-sectional structure of the GAA JL transistor as  $V_G < V_{FB}$  along line AA' shown in Fig. 1(b). EOT is effective oxide thickness, which is equal to 18nm in this case. X<sub>dep</sub> is the depth of depletion region and n is the active doping concentration.

Table. I 1D Poisson equation and the analytical solution of electric potential

| 1D Poisson's Eq.                                                                                                         |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| $\frac{d^2\Phi(x)}{d^2}$ -gr                                                                                             | (1) |

| da <sup>1</sup> 5,                                                                                                       |     |

| Two Boundary Conditions                                                                                                  |     |

| $E(x=X_{dept})=0$                                                                                                        | (2) |

| $\Phi(\mathbf{x}=X_{\mathbf{y}})=0$                                                                                      | (3) |

| Solution of Electric Polential                                                                                           |     |

| $\Phi(x) = \frac{qnX_{dy}}{s} x - \frac{qn(x^2 + X_{dy}^2)}{2s}, 0 < x < X_d$                                            |     |

| $\Phi(x) = \frac{1-\varepsilon_{ex}}{\varepsilon_{ex}} x - \frac{1-\varepsilon_{ex}}{2\varepsilon_{ex}}, 0 < x < X_{ex}$ |     |

Table. II Summary of the analytical expression of  $X_{dep,max}, V_{G,off}$  and  $V_{FB}$ .  $X_{dep,max}$  is the maximum depth of depletion region.  $V_{\text{G,off}} \text{ is the applied gate voltage as}$ X<sub>dep,max</sub> is reached

Fig. 5 Schematic illustration of the cross-sectional structure of the GAA JL transistor as  $V_G < V_{G, off}$  along line BB' shown in Fig. 1(b).

Table. III Analytical expression of conduction area and current of ungated resistor.

| Conduction Area                                                  |     |

|------------------------------------------------------------------|-----|

| $H \times W - 2(H + W) X_{depl, max} + 4 X_{depl, max}^2.$       | (8) |

| Resistance of Ungated Resistor                                   |     |

| $R = V_D / I_D$                                                  |     |

| $= L/nq\mu(H\times W - 2(H+W)X_{depl,sex} + 4X_{depl,sex}^{2}).$ | (9) |

2.88V

0.04

0.06