# Narrow Width Effects on High Frequency Performance and RF Noise of Sub-40nm Multi-finger nMOSFETs

Kuo-Liang Yeh, Chih-Shiang Chang, and Jyh-Chyurn Guo Institute of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan Tel: +886-3-5131368, Fax: +886-3-5724361, E-mail: jcguo@mail.nctu.edu.tw

## Abstract

The impact of narrow width effects on high frequency performance parameters like  $f_T$ ,  $f_{MAX}$ , and RF noise in 35 nm multi-finger n-MOSFETs is investigated in this paper. Multi-OD devices with reduced width under fixed finger number (N<sub>F</sub>) lead to higher R<sub>g</sub> and suffer the penalty in f<sub>T</sub>,  $f_{MAX}$ , and NF<sub>min</sub>. On the other hand, narrow-OD MOSFET with larger N<sub>F</sub> can yield lower R<sub>g</sub> and higher  $f_{MAX}$ . However, these narrow-OD devices even with lower R<sub>g</sub> suffer lower f<sub>T</sub> and higher NF<sub>min</sub>. The mechanisms responsible for narrow width effects on f<sub>T</sub>,  $f_{MAX}$ , and noise parameters will be presented to offer an important guideline of MOSFET layout for RF circuits design using nanoscale CMOS technology.

#### **I. Introduction**

Nanoscale CMOS devices with multi-finger layout have been extensively used for higher  $f_T$  and  $f_{MAX}$ , and lower RF noise driven by gate length scaling and gate resistance ( $R_g$ ) reduction from multi-finger structure [1-3]. Unfortunately, the continuous reduction of finger width ( $W_F$ ) and increase of finger number ( $N_F$ ) for smaller  $R_g$  may lead to the penalty of lower transconductance ( $g_m$ ) and larger parasitic capacitances. The former one comes from stress induced mobility degradation and the latter one stems from gate related fringing capacitances [4-5]. Both can not be scalable with device scaling and the impact may dominate high frequency characteristics in nanoscale devices. The potential impact from parasitic capacitances and the trade-off with  $R_g$  becomes a critical factor governing the specified RF performance parameters and has to be considered seriously in devices layout for RF circuit design.

#### **II. Experimental**

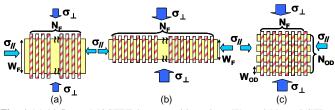

The multi-finger n-MOSFETs were fabricated in 65nm CMOS process, with 35nm physical gate length and the total gate width fixed at 64  $\mu$ m ( $W_{tot}=W_F \times N_F=64\mu$ m). Fig.1(a)~(c) illustrate multi-finger MOSFET layouts, namely standard, narrow-OD, and multi-OD devices in which  $\sigma_{1/}$  and  $\sigma_{\perp}$  denote the longitudinal and transverse stresses introduced from STI. S-parameters were measured by Agilent network analyzer E8364B up to 40GHz. In particular, open and short deembedding to the bottom metal, i.e. M1, were performed to remove the parasitic capacitances from the pads as well as interconnection lines [5]. Four noise parameters, such as NF<sub>min</sub>, R<sub>n</sub>, Re(Y<sub>opt</sub>), and Im(Y<sub>opt</sub>) can be measured by using ATN-NP5B from 1GHz up to 18GHz.

### **III. Results and Discussion**

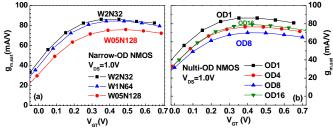

Fig. 2(a) demonstrates  $g_m$  versus  $V_{GT}$  ( $V_{GS}$ - $V_T$ ) in saturation region measured from narrow-OD and standard nMOS. This monotonic degradation of  $g_m$  with  $W_F$  scaling suggests that the increase of compressive  $\sigma_{\perp}$  is the dominant factor responsible for mobility degradation and the resulted  $g_m$  reduction [6]. As for multi-OD nMOS shown in Fig. 2(b), the  $g_{m,max}$  of OD4 and OD8 are degraded by 11.2% and 18.9%, as compared to OD1, but the degradation becomes smaller to 8.5% for OD16. According to our recent work [7], the increase of effective width ( $W_{eff}$ ) from STI top corner rounding induced  $\Delta W$  can compensate mobility degradation. Note that  $\Delta W$  of nMOS in this process is 38.7 nm. With the

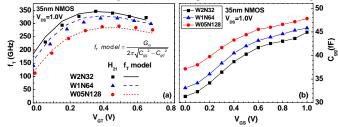

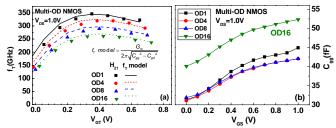

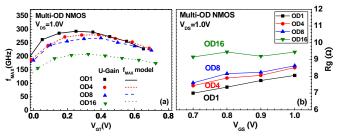

increase of  $N_{\text{OD}},\,\Delta W$  effect will be enhanced and may dominate STI  $\sigma_{\perp}\,$  effect, which explain the increase of  $g_m$  when scaling  $W_{OD}$ from  $0.25\mu m$  for OD8 to  $0.125\mu m$  for OD16. Fig. 3(a) reveals that W<sub>F</sub> scaling in narrow-OD nMOS leads to a monotonic f<sub>T</sub> degradation. An analytical model given by (1) [8] suggests that  $f_T$ degradation can be originated from g<sub>m</sub> degradation and/or increase of  $C_{gg}$ . For narrow-OD nMOS, the smallest  $g_m$  appearing in W05N128 (Fig.2(a)) is considered as one of major factors responsible for the worst f<sub>T</sub>. Furthermore, the measured C<sub>gg</sub> (Fig.3(b)) indicates 8.3% increase of  $C_{gg}$  in W05N128. The combined effect from lower  $g_m$  and larger  $C_{gg}$  can explain  $f_T$ degradation in narrow-OD devices [5]. As for multi-OD nMOS, Fig.4(a) again indicates a monotonic degradation of  $f_T$  with  $W_{OD}$ scaling. Obviously, OD16 with the smallest width (0.125µm) suffers the lowest f<sub>T</sub>. As shown in Fig.4(b), OD16 reveals substantially larger Cgg compared to OD1. Although OD16 yields higher  $g_m$  than OD4 and OD8, due to  $\Delta W$  effect (Fig.2(b)), the much larger  $C_{gg}$  offsets the  $g_m$  increase and leads to  $f_T$  degradation.

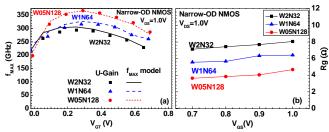

Fig. 5(a) presents an increase of  $f_{MAX}$  with  $W_F$  scaling and the highest  $f_{MAX}$  achieved by W05N128. The  $f_{MAX}$  can be calculated by (2) [8], which indicates that the higher  $f_T$  and lower  $R_g$  can enhance  $f_{MAX}$ . Referring to Fig.3(a), W05N128 suffers the lowest  $f_T$ . However, the smaller  $W_F$  and larger  $N_F$  in narrow-OD devices can reduce  $R_g$  as shown in Fig.5(b). Almost 50% lower  $R_g$  realized by W05N128 can over-compensate  $f_T$  degradation and contribute to higher  $f_{MAX}$ . On the other hand, multi-OD nMOS shown in Fig.6(a) indicates a monotonic degradation of  $f_{MAX}$  with  $W_{OD}$  scaling. Referring to Fig.4(a), the larger  $N_{OD}$ , i.e. the smaller  $W_{OD}$  indeed leads to  $f_T$  degradation. As for  $R_g$  shown in Fig.6(b), the smaller  $W_{OD}$  (larger  $N_{OD}$  and fixed  $N_F$ ) suffers the higher  $R_g$  and OD16 reveals around 20~25% higher  $R_g$ . According to (2), the lower  $f_T$  and larger  $R_g$  appearing in multi-OD devices are two key factors responsible for  $f_{MAX}$  degradation with  $W_{OD}$  scaling.

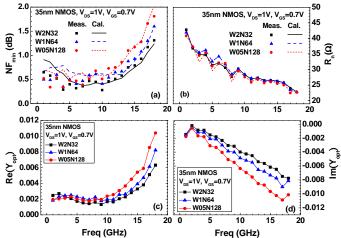

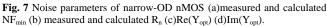

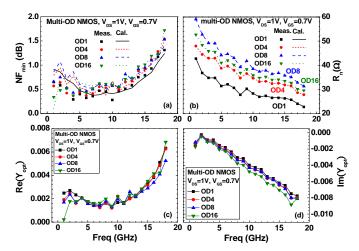

Fig. 7(a)-(d) present NF<sub>min</sub>, R<sub>n</sub>, Re(Y<sub>opt</sub>), and Im(Y<sub>opt</sub>) measured from the standard and narrow-OD nMOS (1~18GHz). W05N128 with the smallest W<sub>F</sub> and R<sub>g</sub> suffers 0.2~0.5dB higher NF<sub>min</sub> in 9~18GHz. Fig.7(c) and (d) reveal significant increase of  $Re(Y_{opt})$  and  $Im(Y_{opt})$  (absolute value) in W05N128 at higher frequencies, above 9GHz. According to (3)~(4) [8], the increase of either  $R_n$  or  $Re(Y_{opt})$  will result in higher NF<sub>min</sub> and the calculated NF<sub>min</sub> can fit measured data in terms of frequency and layout dependence as shown in Fig.7(a). This proven model combined with Fig.7(b) and (c) for measured  $R_n$  and  $Re(Y_{opt})$  indicates that the increase of  $Re(Y_{opt})$  is the primary factor responsible for higher  $NF_{min}$  in narrow-OD nMOS. According to (5) for  $R_n$ , the benefit of smaller Rg in narrow-OD device happens to be cancelled out by the increase of the second term due to lower gm from compressive  $\sigma_{\perp}$ . As for multi-OD nMOS shown in Fig.8(a)-(d), OD16 reveals the largest value in  $Re(Y_{\text{opt}})$  and  $|Im(Y_{\text{opt}}),$  leaving  $R_n$  as the exception. It is interesting to note that OD16 suffers the largest R<sub>o</sub> (Fig.6(b)) but achieves  $R_n$  lower than OD8. Referring to (5), the higher  $g_m$  can help reduce  $R_n$ , due to smaller  $g_{do}/g_m^2$ , and reverse the correlation between  $R_n$  and  $R_g$ . It explains why OD16 has the larger  $R_g$  but smaller  $R_n$  than OD8. The counterbalance between  $Re(Y_{opt})$  and  $R_n$  results in comparable NF<sub>min</sub> between OD16 and OD8. All of multi-OD nMOS suffer higher NF<sub>min</sub> than OD1.

$$f_{\tau} = \frac{g_m}{2\pi \sqrt{C_{gg}^2 - C_{gd}^2}}$$

(1)

$$f_{MAX} = \frac{r_{\tau}}{2\sqrt{R_g(g_{ds} + 2\pi f_{\tau} C_{gd}) + g_{ds}(R_i + R_s)}}$$

(2)

$$F_{\min} = 1 + 2R_n \operatorname{Re}(Y_{opt})[1 + R_n \operatorname{Re}(Y_{opt})]$$

(3)

(4)

$$NF_{min} = 10 \cdot \log F_{min}$$

$$R_n \approx R_g + \gamma \frac{g_{d_0}}{g_m^2} (\gamma > 1 \text{ for short channel devices})$$

(5)

# Acknowledgement

This work is supported in part by the National Science Council under Grant NSC98-2221-E009-166-MY3. Besides, the authors acknowledge the support from NDL for noise measurement and CiC for test chip and device fabrication.

#### References

- W. Jeamsaksiri, et al., Symp. VLSI Tech. Dig., 2005, pp. 60-61.

I. Post, et al., IEDM Tech. Digest. 2006, pp. 1013-1015.

- [3] H. Li, et al., Symp. VLSI Tech. Dig., 2007, pp. 56-57.

- [4] J.-C. Guo, et al., IEEE TED-56, pp.1598-1607, 2009.

- [5] K.-L. Yeh, et al., IEEE TED-58, pp.2838-2846, 2011.

- [6] Y. Luo, et al., IEEE Tran. on Semi. Manuf.-18, pp.63-68, 2005.

- [7] K.-L. Yeh, et al., IEEE TED-57, pp.3092-3100, 2010.

- [8] T. Manku, et al., J. of Solid-State Circuit -34, pp.277-285, 1999.

**Fig. 1** Multi-finger MOSFET layouts with various  $W_F$  and  $N_F$  and STI stresses  $\sigma_{ll}$  and  $\sigma_{\perp}$  (a) standard device :  $W_F X N_F = 2\mu m x 32$  (W2N32), (b) narrow-OD devices :  $W_F x N_F = 1\mu m x 64$  (W1N64), 0.5 $\mu m x 128$  (W05N128), and (c) multi-OD devices  $W_{OD} \times N_{OD} = W_F = 2\mu m$  : OD4, OD8, OD16.

**Fig. 2** The  $g_m$  versus  $V_{GT}$  ( $V_{DS}=1V$ ) measured from (a) narrow-OD nMOS and (b) multi-OD nMOS.  $g_m=Re(Y_{21})$  after open and short deembedding.

**Fig. 3** (a) The measured and calculated  $f_T$  versus  $V_{GT}$  ( $V_{DS}$ = 1.0V) and (b) the gate capacitances  $C_{gg}$  versus  $V_{GS}$  extracted from Im( $Y_{11}$ ) for narrow-OD and standard nMOS

Fig. 4 (a) Measured and calculated  $f_T$  vs.  $V_{GS}$  ( $V_{DS}{=}1.0V)$  (b)  $C_{gg}$  vs.  $V_{GS}$  extracted from Im( $Y_{11})$  for multi-OD and standard nMOS.

Fig. 5 (a) The measured and calculated  $f_{MAX}$  versus  $V_{GT}$  ( $V_{DS}$ = 1.0V) and (b) $R_g$  versus  $V_{GS}$  for narrow-OD nMOS (W1N64, W05N128) and W2N32

Fig. 6 (a) The measured and calculated  $f_{MAX}$  versus  $V_{GT}$  ( $V_{DS}$ = 1.0V) and (b)  $R_g$  versus  $V_{GS}$  for multi-OD nMOS (OD4, OD8, OD16) and OD1

Fig. 8 Noise parameters of multi-OD nMOS (a)measured and calculated NF<sub>min</sub> (b) measured and calculated  $R_n$  (c)Re( $Y_{opt}$ ) (d)Im( $Y_{opt}$ ).