# Study of Off-State Breakdown Improvement and Hot-Carrier Reliability in LDMOS Device with Gradual Junction Structure

Chin-Rung Yan<sup>1</sup>, Jone F Chen<sup>1</sup>, Chung-Yi Lin<sup>2</sup>, Hao-Tang Hsiu<sup>2</sup>, Yu-Chieh Liao<sup>2</sup>, Min-Ti Yang<sup>2</sup>, Ying-Chia Lin<sup>2</sup>, Huei-Haurng Chen<sup>2</sup>

<sup>1</sup> Institute of Microelectronics, Department of Electrical Engineering, National Cheng Kung University, Tainan, Taiwan Phone: +886-3-579-5000 ext.8709 E-mail: darren0613@gmail.com

<sup>2</sup> Device Technology Group, Powerchip Technology Corp., Hsin-Chu, Taiwan

## 1. Introduction

off-state Both breakdown voltage  $(V_{BD})$ and on-resistance (Ron) performances are the major considerations in designing LDMOS devices. However, these two parameters are usually trade-off with each other. In this work, a gradual junction structure is used to improve off-state V<sub>BD</sub> without sacrificing device drivability. Experimental data of V<sub>BD</sub> improvement and hot-carrier induced device degradation are presented and discussed. In addition, TCAD simulation results of electric field and impact ionization (I-I) rate are analyzed to explain the experimental data. Finally, electrical safe operating area (E-SOA) of devices is investigated. The device with gradual junction structure has wider E-SOA range.

## 2. Experiment

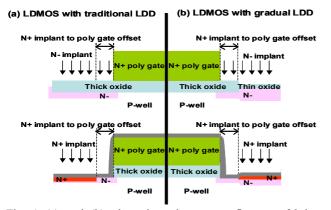

The dimensions of W/L and gate oxide thickness of the device used in this work are 10/0.9 um and 40 nm, respectively. Fig. 1(a) and (b) show the schematic process flows to fabricate LDMOS device with traditional and gradual junction structures, where the self-alignment implant of N- region experience uniform and gradual screen oxide thickness. The gradual screen oxide structure, which is formed by dual oxide (8nm and 40nm) process, leads to gradual junction profile in N- region of LDMOS device. After self-alignment implant of N- region, a n+ implant with a distance 0.75 um to the poly gate is defined.

Fig. 1 (a) and (b), the schematic process flows to fabricate traditional and gradual junction structures are compared.

#### 3. Experiment Results and Discussions

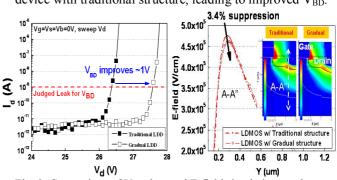

Fig. 2 shows the off-state breakdown characteristics for devices with traditional and gradual junction profile. Compared with the device with traditional structure, the device with gradual junction profile has better  $V_{BD}$  which is improved by about 1V. This improvement can be explained by TCAD simulation results in Fig. 2. At the same drain voltage (V<sub>D</sub>), the device with gradual junction profile has smaller electrical field (~3.4%) in cutline A-A" than the device with traditional structure, leading to improved V<sub>BD</sub>.

Fig. 2, Comparison of  $V_{\text{BD}}$  data and E-field simulation results.

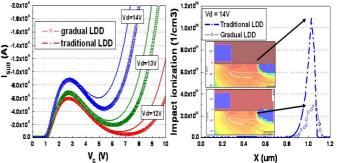

Fig. 3 shows substrate current ( $I_{SUB}$ ) vs. gate voltage ( $V_G$ ) characteristics under  $V_D = 12V$ , 13V, and 14V. At  $V_G$  is roughly 3V, the value of first  $I_{SUB}$  peak is about the same between devices with traditional and gradual junction profile. As the  $V_G$  is greater than roughly 6V, Kirk effect is becoming significant and  $I_{SUB}$  rises again. Such Kirk effect induced  $I_{SUB}$  rise is less severe in the device with gradual junction profile. The suppression of Kirk effect can be explained by TCAD simulation results. As seen in Fig. 3, at  $V_D = 14V$  and  $V_G = 7V$ , the device with gradual junction profile has smaller I-I rate, leading to smaller  $I_{SUB}$ .

Fig. 3, Comparison of  $I_{\mbox{\scriptsize SUB}}$  data and impact ionization simulation results.

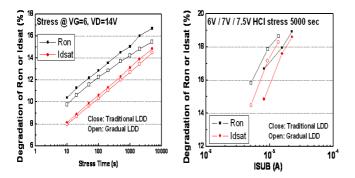

Since the device with gradual junction profile can suppress Kirk effect and leads to smaller I<sub>SUB</sub> at high V<sub>G</sub> bias, hot-carrier reliability of this device is likely to be improved. Fig. 4 shows the device parameter degradation of two kinds of device under 5000s of hot-carrier stress. The device parameters monitored are Ron and drivability current (I\_Dsat) which are measured at  $V_{\rm D}{\,=\,}0.1V$  and  $V_{\rm D}{\,=\,}$ 8V, respectively. For devices stressed under the same  $V_D$ and  $V_G$  ( $V_D = 14V$ ,  $V_G = 6V$ ), the device with gradual junction profile shows smaller Ron and  $I_{\text{Dsat}}$  degradation. This result suggests that reduced  $I_{SUB}$  (under the same  $V_G$ ) caused by suppression of I-I rate improves hot-carrier reliability. In order to realize the relation between  $I_{SUB}$  and device degradation, Fig. 4 also shows the amount of device degradation under 5000s stress for devices stressed at V<sub>G</sub> bias (6V, 7V, and 7.5V) such that  $I_{SUB}$  rise caused by Kirk effect is significant. Stress data show that for devices stressed under the same I<sub>SUB</sub>, the device with gradual junction profile produces more device degradation than the device with traditional structure. Remember that higher  $V_{G}$ bias is needed for the device with gradual junction profile to produce the same  $I_{\text{SUB}}$  (due to the suppression of Kirk effect). Thus, higher V<sub>G</sub> results in more electron injection to the gate oxide, leading to more device degradation [2].

Fig. 4, Comparison of device degradation data under hot-carrier stress.

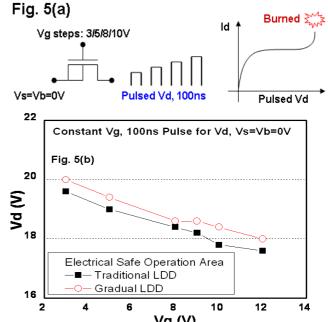

Finally, the E-SOA of devices with traditional and gradual junction structures is investigated. Fig. 5(a) depicts the measurement setting to obtain E-SOA, where different  $V_G$  steps and 100ns pulse of  $V_D$  are applied to the device. The breakdown points are judged at a given  $V_G$  and pulsed  $V_D$  which causes device burned. Results in Fig. 5(b) reveal that the device with gradual junction profile has wider E-SOA range than the device with traditional structure. Improvement of E-SOA range is suggested to be caused by suppression of  $I_{SUB}$  and better latch-up behavior.

Fig. 5, the measurement setting and comparison of electrical safe operation area (E-SOA) data.

## 3. Conclusions

A simple mask modification which produces gradual screen oxide structure can be utilized to fabricate LDMOS devices with gradual junction profile in the N- region. In off-state operation, the device with gradual junction structure shows roughly 1V improvement in V<sub>BD</sub> due to suppression of electrical field. In on-state operation, the device with gradual junction structure has less Kirk effect induced I<sub>SUB</sub> rise due to suppression of I-I rate. For hot-carrier stress under the same V<sub>G</sub> bias, the device with gradual junction structure exhibits less device parameter degradation due to suppression of I-I rate. For hot-carrier stress under the same I<sub>SUB</sub>, however, the device with gradual junction structure produces worse device degradation. The reason responsible for this phenomenon is that higher  $V_G$  is needed to produce the same  $I_{SUB}$ , leading to more electron injection to the gate oxide. Finally, experimental data show that the device with gradual junction structure has wider E-SOA range than the device with traditional structure.

#### Acknowledgements

We would like to thank Ariels Song and Shih-Hsiang Lin for measurement and simulation.

### References

S. A. Parke et al., IEEE T-ED, vol. 37, no.7, pp. 1694, 1992

J. F. Chen et al., Electro. Lett., vol. 44, no. 16, pp. 991, 2008