# A 3-mW/Gbps 1.8-V Current-reuse LVDS Driver with 30% Power Reduction using Vertical MOSFETs

Satoru Tanoi<sup>1,2</sup> and Tetsuo Endoh<sup>1,2</sup>

<sup>1</sup> Graduate School of Engineering, Tohoku University, <sup>2</sup> JST-CREST Aramaki aza Aoba 6-6, Aoba-ku, Sendai, 980-8579 Japan Phone: +81-22-795-4401 E-mail: endoh@riec.tohoku.ac.jp

### 1. Introduction

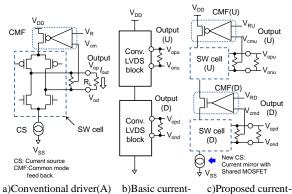

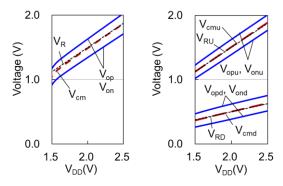

Recently low-voltage differential signaling(LVDS) drivers shown in Fig.1(a) with reducing the output swing voltage  $(V_{OD})$  have been developed to reduce the power consumption<sup>[1]</sup>. However, when  $V_{OD}$  is too small, the receiver failes. Therefore, the current-reuse approach<sup>[2]</sup> reduces more effectively the power consumption keeping the output current  $I_{out}$  in proportional to  $V_{OD}$ . The basic current reuse driver is shown in Fig.1(b). It has two conventional LVDS drivers and two output port (U and D). Since the U-port current is reused in D-port, the power consumption is reduced to approximately half. However, it is still difficult to realize the low  $V_{DD}$  operation in this basic topology, because of the large voltage drops of cascaded MOSFETs.

To overcome the above problems, we propose a new topology for the current reuse LVDS driver. Moreover, we describe the proposed driver with the vertical MOSFETs and its excellent features, such as a power reduction with high data rate in low  $V_{\rm DD}$  operation.

#### 2. Circuit Design

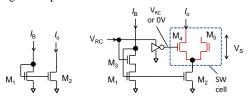

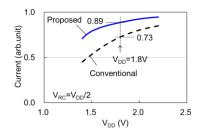

The topology for the proposed current reuse LVDS driver is shown in Fig.1(c). The keys are: 1)cascaded current mirror with shared MOSFET, 2)vertical MOSFETs with body effect free<sup>[3]</sup>. Figure 2 shows the proposed current mirror in comparison with conventional one. The output current of the conventional decreases rapidly with  $V_{DD}$  falling. We design a new cascaded current mirror with shared MOSFET for our driver. Since the MOSFET(M<sub>4</sub>, M<sub>5</sub>) are shared with the current mirror and the switch cell(SW cell), the  $V_{DD}$  is reduced equal to  $V_s$ . Figure 3 shows the output current comparison. The output current decreasing from the ideal current I<sub>M</sub> in our design is less than half the conventional. Figure 4(a) shows the structure of the vertical MOSFET<sup>[3]</sup> employed. Since the vertical MOSFET has no body-effect, and enables the low  $V_{\text{DD}}$  design compared with the planar  $MOSFET^{[2,3]}$ . Figure 4(b) shows the voltage drop (V<sub>n</sub>) of the circuit with cascaded vertical MOSFETs in comparison with conventional one. The voltage drop of the circuit(n=8) with the vertical MOSFET is 77.6% of that with planar one. Furthermore, we use the NMOS source follower in the down-side loop for stable operation.

## 3. Simulation Results and Discussion

We compare the characteristics of the following drivers; A, B, C and D. A shown in Fig.1 (a) is conventional driver without current reuse. B shown in Fig.1 (b) is basic current reuse driver with the conventional drivers. C and D shown in Fig.1 (c) are our proposed current reuse drivers. C is design with planar MOSFETs, and D is designed with vertical ones. In the simulation, we use the parameters of the 0.18-um planar MOSFET for 1.8-V in a 90nm technology.

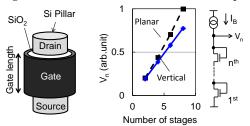

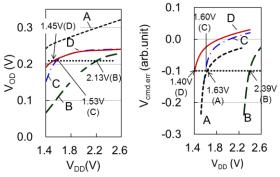

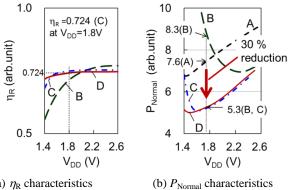

The vertical MOSFET is simulated with the model whose body is connected to the source. We set a target of  $V_{\text{OD}}$  as 200mV at 1.8-V  $V_{DD}$ . And, we set the mirror ratio as 40, and  $I_M (= 40I_B)$  as 2.5mA for a V<sub>OD</sub> target with a 100 $\Omega$  R<sub>L</sub>. Figure 5 shows the output voltage comparison between the drivers with and without the current reuse(A and D). The proposed design(D) shows the stable outputs as well as the conventional driver without current reuse(A). To compare the minimum operation voltage of each circuit, we define  $V_{DD,OD}$ , as  $V_{DD}$ , where a 200-mV  $V_{OD}$  is obtained. And we define  $V_{DD.cmerr}$ , with the feed-back error ( $V_{cmd.err}$ ) equal to 10%. The minimum  $V_{DD}$  ( $V_{DD,min}$ ) is defined as higher voltage of V<sub>DD.OD</sub> or V<sub>cmd.err</sub>. Figure 6(a) shows the typical V<sub>OD</sub> and V<sub>DD.OD</sub> of each driver, and Fig.6(b) shows the typical  $V_{\text{cmd.err}}$  and  $V_{\text{DD.cmerr}}$ . Note that the U-port feed-back errors are small enough. The V<sub>DD,min</sub> of the A, B, C and D is 1.63, 2.39, 1.60, 1.45V relatively. The B-type with the conventional drivers can't be operated in low V<sub>DD</sub>. Thanks to our proposed current mirror, the 1.8-V V<sub>DD</sub> operation is achieved with enough margin in the proposed driver (C and D). Figure 7(a) shows the current reuse ratio  $\eta_R$  (=I\_{out}/I\_{toal}) of each driver. The C and D-types with our proposed topology show higher than 68% in the  $V_{DD}$  range from 1.4 to 2.6V. Figure 7(b) shows the power consumption  $P_{\text{Normal}}$  normalized by output power  $P_{\text{out}}$ . The  $P_{\text{Normal}}$  of the current reuse drive with two ports is given by (1)

$$P_{Normal} = \frac{1}{2\eta_R} \cdot \frac{V_{DD}}{V_{OD}} \quad \cdot$$

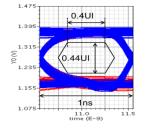

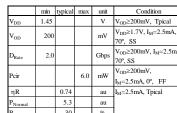

Since each proposed driver (C and D) shows high  $\eta_{\rm R}$  in low  $V_{\rm DD}$ , the low  $P_{\rm Normal}$  is achieved, though C (planar) is marginal with  $V_{\rm DD}$  lower than 1.5-V. The proposed driver with vertical MOSFETs shows stable  $P_{\rm Normal}$  with even low  $V_{\rm DD}$ . The typical  $P_{\rm Normal}$  of the proposed driver (D) is 5.3 with 1.8-V V\_{\rm DD} and 200-mV V\_{\rm OD}. This is equal to 70% of the conventional deriver (A) power. Figure 8 shows the achieved eye diagram of the proposed driver (D), with 1-ns data period, 1.7-V V\_{\rm DD}, 70°C and SS parameters. The power consumption with 1.9-V V\_{\rm DD}, 0°C and FF is 6.0mW. Thus proposed driver (D) with two ports achieves 2-Gbps with enough margins. The figure-of-merit is 3-mW/Gbps. The performance of our driver is summarized in Table I. **4. Conclusions**

A low  $V_{DD}$  current reuse LVDS driver is proposed. The new cascaded current mirror and the vertical MOSFETs enable the stable  $V_{OD}$  and high  $\eta_R$  with low  $V_{DD}$ . The performance of 3-mW/Gbps with 1.8-V  $V_{DD}$  is achieved using parameters of a 0.18-um MOSFET in 90nm technology. Achieved power reduction is equal to 30% of the conventional driver power consumption.

#### Acknowledgements

This work has been supported in part by a grant from "Research of Innovative Material and Process for Creation of Next-generation Electronics Devices" of CREST (Research and Development of Vertical Body Channel MOSFET and Its Integration Process, Research Director: Tetsuo Endoh), under the Japan Science and Technology Agency (JST). This study also was designed in with Cadence and Synopsys CAD tools, and in the chip fabrication program of VDEC, the University of Tokyo, with the collaboration by STARC, Fujitsu Limited. **References**

- References

- [1] S. Jamasb et al., Proc. IEEE MWSCAS, (2001) 610.

- [2] S. Tanoi and T. Endoh, JJAP, 51, (2012) 04DE11.

- [3] K. Sakui and T. Endoh, IEEE ICMTS, Proc. (2010) 220.

reused driver(C/D)

reuse driver(B)

Fig. 1. Proposed LVDS drivers.

a)Conventional b)Proposed circ. with shared MOS Fig. 2. Proposed Current mirror circuit.

Fig. 3. Current mirror characteristics comparison.

(a) Vertical MOSFET (b) Characteristics of circuits Structure<sup>[3]</sup> with cascaded MOSFETs

Fig. 4. Vertical MOSFET structure and characteristics of circuits with vertical MOSFTE in comparison with planar.

(a) Conventional driver(A)(b) Proposed driver(D)Fig. 5. Output voltage comparison.

(a)  $V_{OD}$  characteristics (b)  $V_{cmd.err}$  characteristics \*A: Conventional t driver(planar),

B: Conventional basic current reuse driver(planar),

C: Proposed driver(planar),

D: Proposed driver(vertical)

Fig. 6.  $V_{OD}$  and  $V_{cmd.err}$  characteristics ( $I_M$ =2.5mA).

(a)  $\eta_{\rm R}$  characteristics \*A,B,C and D: see Fig. 6.

Fig. 7.

$$\eta_R$$

and  $P_{\text{Normal}}$  characteristics (I<sub>M</sub>=2.5mA).

Table I The proposed driver (D)

\*Load: L=2nH,  $C_{L1}$ =0.2pF,  $C_{L2}$ =2.0pF. Fig. 8. Eye diagram of the proposed driver (D).

| r <sub>RED</sub>                 |                                 | 50    |       | 70        |                      |

|----------------------------------|---------------------------------|-------|-------|-----------|----------------------|

| V <sub>RU</sub> =3V <sub>D</sub> | <sub>D</sub> /4, V <sub>R</sub> | D=VDD | 4, DR | ate:Total | data rate of 2 ports |