# A 256-configuration-context MEMS optically reconfigurable gate array

Yuichiro Yamaji and Minoru Watanabe

Electrical and Electronic Engineering

Shizuoka University

3-5-1 Johoku, Hamamatsu, Shizuoka 432-8561, Japan

Email: tmwatan@ipc.shizuoka.ac.jp

Abstract—Demand for Field Programmable Gate Arrays (FP-GAs) designed for space use is increasing to support hardware repair and hardware update functions as well as software repair and update functions in spacecraft, satellites, space stations, and other applications. However, many high-energy charged particles are incident to devices in radiation-rich space environments. Since FPGA's configuration context is stored on SRAM, the configuration context is damaged by high-energy charged particles Therefore, this paper presents a proposal for a 256-configuration-context dependable MEMS optically reconfigurable gate array that can be reconfigured using damaged configuration contexts.

#### I. Introduction

Demand for Field Programmable Gate Arrays (FPGAs) designed for space use is increasing to support hardware repair and hardware update functions in addition to support software repair and update functions in spacecraft, satellites, space stations, and other applications [1][2]. However, in space radiation environment, incidences of high-energy charged particles cause single-event or multi-event upset (S/MEU)-associated temporary failures in SRAM [3][4]. Such S/MEU-associated temporary failures alter contents of SRAM. For that reason, it is difficult to maintain the reliability of configuration data on SRAM during long-term use in a space environment [5]–[7]. Of course, although TMR implementations can resolve a part of such FPGA hardware troubles [8][9], and although some damage can be corrected by error-checking and correction methods [10], the methods are not perfect for repair of MEUs.

To date, MEU-tolerant optically reconfigurable gate arrays (ORGAs) have been developed [11][12]. An ORGA consists of a holographic memory, a laser array, and an optically programmable gate array VLSI. Contexts of the gate array are stored in a holographic memory, from which they are read out optically and are programmed optically onto the gate array VLSI using photodiodes. Such an optical configuration is an extremely robust configuration. In the ORGAs, even if high-energy charged particles damage 35 % of configuration data, a correct configuration procedure can be executed using the damaged configuration data [13]. Therefore, ORGAs have been demonstrated as robust devices against space radiation.

This paper presents a proposal of an optoelectronic programmable device having the world's first 256 configuration contexts intended for space use. The 256-configuration-context

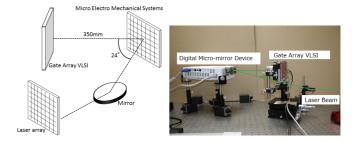

Fig. 1. Dependable MEMS-ORGA.

dependable MEMS optically reconfigurable gate array can be reconfigured using damaged configuration contexts.

# II. 256-CONFIGURATION-CONTEXT DEPENDABLE MEMS-ORGA

Fig. 1 presents a 256-configuration-context dependable MEMS-ORGA. The MEMS-ORGA comprises a gate-array VLSI (ORGA-VLSI), an electrically writable MEMS holographic memory storing 256 configuration contexts, and 256 lasers. The 256 optical reconfiguration contexts are stored on the electrically writable MEMS holographic memory. The 256 lasers are also used to address the 256 reconfiguration contexts. One configuration context is programmed onto ORGA-VLSI if one laser turns on. The optical reconfiguration can be regarded as a majority voting operation. Therefore, this device is useful as a robust dynamic reconfigurable device under a space radiation environment.

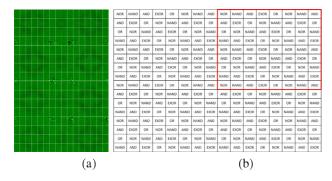

The MEMS optically reconfigurable gate array was constructed using a 532 nm, 300 mW laser (torus 532; Laser Quantum), a MEMS holographic memory, and an ORGA-VLSI [11],[12]. A laser was shared and used for emulation of 256 lasers. A computer-generated MEMS holographic memory pattern is presented in Fig. 2. Each value of a pixel takes a binary value of H or L. The holographic memory includes 256 configuration context patterns, as shown in the map of Fig. 2(b). Each region consists of  $126 \times 94$  pixels. The holographic memory pattern, shown in Fig. 2, is programmed electronically onto the MEMS holographic memory using a personal computer. The MEMS holographic memory consists of  $1,024 \times 768$  pixels, each of  $10.8 \times 10.8$   $\mu m^2$ . It was provided by Texas

Fig. 2. (a) Binary holographic memory pattern including 256 configuration contexts and (b) an implementation map of the configuration contexts.

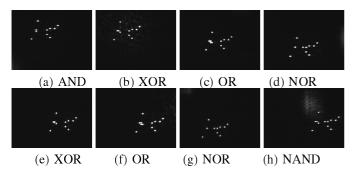

Fig. 3. CCD captured images of configuration contexts of circuits.

Instruments Inc.. After programming, all mirror angles on the MEMS holographic memory were adjusted depending on the holographic memory pattern of Fig. 2. The beam from the laser source is of 1.7-mm-diameter. The collimated beam is incident to the MEMS holographic memory. Then, the beam is reflected onto the ORGA-VLSI. The ORGA-VLSI chip was fabricated using a 0.35  $\mu$ m triple-metal CMOS process [11],[12]. The ORGA-VLSI chip consists of 4 logic blocks, 5 switching matrices, and 12 I/O bits. The VLSI chip functionality is fundamentally identical to that of typical FPGAs.

### III. EXPERIMENTAL RESULTS

Using the experimental system explained above, circuits were implemented on the system. Since the holographic memory pattern is symmetrical, 8 × 8 configuration contexts at the upper right side on holographic memory pattern shown in Fig. 2 were displayed on the MEMS device. Particularly, demonstration results for eight circuits on the diagonal line are discussed in detail. The eight circuits on the diagonal line are, respectively, an AND circuit, an EXOR circuit, an OR circuit, an NOR circuit, an EXOR circuit, an OR circuit, an NOR circuit, and an NAND circuit. The CCD captured images of the configuration contexts are depicted in Figs. 3(a) - 3(h), which were generated, respectively, from the upperright-side diagonal region of the MEMS holographic memory. Such configuration context patterns were programmed sequentially onto an ORGA-VLSI. Laser-based reconfiguration times were measured as 125-335 ns. The experiments show that the MEMS ORGA architecture supports extremely rapid reconfiguration by switching a laser array. Moreover, the

MEMS holographic memory can be reconfigured constantly and electrically in less than 22  $\mu s$  by switching a MEMS device

## IV. CONCLUSION

This paper has described a 256-configuration-context dependable MEMS optically reconfigurable gate array that is useful in a radiation-rich space environment. The gate array enables 125–335 ns high-speed reconfiguration and flexible reconfiguration by both switching of an electrically rewritable MEMS holographic memory and switching of a laser array. Such architecture presents new and exciting avenues for the use of programmable devices in a space radiation environment.

#### ACKNOWLEDGMENTS

This research was supported by the Ministry of Education, Science, Sports and Culture, Grant-in-Aid for Scientific Research (B), No. 24300017. The VLSI chip in this study was fabricated in the chip fabrication program of VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Rohm Co. Ltd. and Toppan Printing Co. Ltd.

#### REFERENCES

- [1] Altera Corp., "Altera Devices," http://www. altera.com.

- [2] Xilinx Inc., "Xilinx Product Data Sheets," http://www. xilinx.com.

- [3] S. Redant et al., "Radiation Test Results on First Silicon in the Design Against Radiation Effects (DARE) Library," IEEE Trans. on Nuclear Science, vol. 52, no. 5, pp. 1550-1554, 2005.

- [4] A. Makihara et al., "Single-Event Effects in 0.18 um CMOS Commercial Processes," IEEE Trans. on Nuclear Science, vol. 50, no. 6, pp. 2135-2138, 2003.

- [5] Y. Lin, L. He, "Devices and architecture concurrent optimization for FPGA transient soft error rate," International Conference on Computer Aided Design, 2007

- [6] Greg Miller, Carl Carmichael, Jet Propulsion Labs, "Single-Event Upset Mitigation for Xilinx FPGA Block Memories," XILINX Application Note, Virtex-II FPGAs, 2007.

- [7] A. E. Barbour, "A reconfigurable fault-tolerant system," Midwest Symposium on Circuits and Systems, pp. 189-194, 1992.

- [8] C. E. Stroud, "Reliability of Majority Voting Based VLSI Fault-Tolerant Circuits," IEEE Trans. on VLSI Systems, vol. 2, no. 4. pp. 516-521, 1994.

- [9] M. Radu, D. Pitica, C. Posteuca, "Reliability and failure analysis of voting circuits in hardware redundant design," International Symposium on Electronic Materials and Packaging, pp. 421-423, 2000.

- [10] Jean-Luc Peter, "ECC design of a custom DRAM storage unit," IEEE VLSI Test Symposium, pp. 171 - 173, 1993.

- [11] M. Nakajima, M. Watanabe, "A four-context optically differential reconfigurable gate array," IEEE/OSA Journal of Lightwave Technology, Vol. 27, No 20, pp. 4460-4470, 2009.

- [12] H. Morita, M. Watanabe, "Microelectromechanical Configuration of an Optically Reconfigurable Gate Array," IEEE Journal of Quantum Electronics, Vol. 46, Issue 9, pp. 1288 - 1294, 2010.

- [13] M. Nakajima, M. Watanabe, "Optical buffering technique under space radiation environment," Optics Letters, Vol. 34, Issue 23, pp. 3719-3721, 2009.