# Comparison of Minimum Operation Voltage (Vmin) in Fully Depleted Silicon-on-Thin-BOX (SOTB) and Bulk SRAM Cells

T. Mizutani<sup>1</sup>, Y. Yamamoto<sup>2</sup>, H. Makiyama<sup>2</sup>, H. Shinohara<sup>2</sup>, T. Iwamatsu<sup>2</sup>, H. Oda<sup>2</sup>, N. Sugii<sup>2</sup>, and T. Hiramoto<sup>1</sup>

<sup>1</sup>Institute of Industrial Science, The University of Tokyo, <sup>2</sup>Low-power Electronics Association & Project (LEAP)

4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, Japan, Phone: +81-3-5452-6264, E-mail: mizutani@nano.iis.u-tokyo.ac.jp

#### **Abstract**

The minimum operation voltage (Vmin) of intrinsic channel fully depleted (FD) silicon-on-thin-BOX (SOTB) SRAM cells are measured and compared with conventional bulk SRAM cells in order to directly compare the worst cells. It is confirmed that the worst Vmin of 1k SOTB SRAM cells is half of that of 1k bulk cells, which is a great advantage of SOTB SRAM for lower power and lower voltage operation.

## 1. Introduction

One of the most significant barriers for further supply voltage ( $V_{DD}$ ) scaling in SRAM is the random variability of transistors [1-6]. The minimum operation voltage (Vmin) in large scale SRAM cell array is much higher than that in logic circuits [7], which obstructs low voltage operation of SRAM and forces very complicated circuit design. One of the solutions for Vmin reduction is the introduction of intrinsic channel FD SOI or SOTB FETs that have drastically smaller random threshold voltage ( $V_{TH}$ ) and drain current variability than conventional bulk FETs [8-9]. Actually, we have recently achieved ultra-low voltage operation of 2M bit SOTB SRAM at 0.37V [10].

The stability of SRAM cells is usually characterized by static noise margin (SNM) [1-6]. However, since the stability of SRAM array is determined by the worst cell in the cell array, it is hard to quantitatively compare the cell stability by merely SNM in different technologies.

In this study, "Vmin of the cell" is measured. Vmin's of 1k FD SOTB SRAM cells are intensively measured and directly compared with those in 1k bulk SRAM cells. It is found that the worst Vmin of SOTB SRAM cells is half of that of bulk cells thanks to smaller random  $V_{\text{TH}}$  variability.

#### 2. Measurements

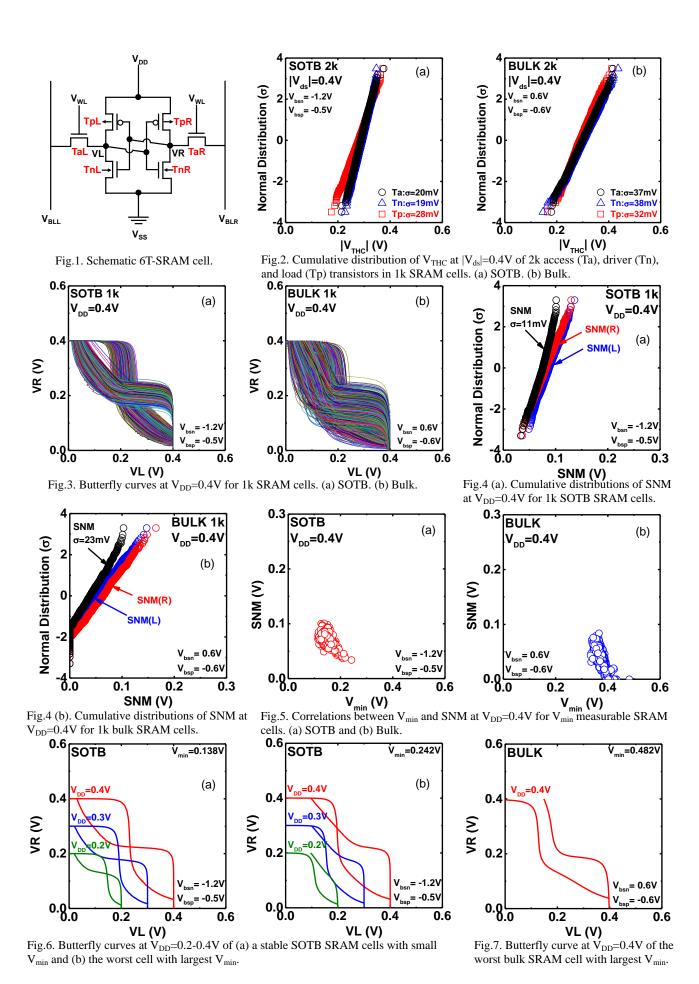

SRAM device-matrix array (DMA) SRAM TEG [5-6] with intrinsic channel SOTB FETs was fabricated by the 65nm technology [10-11]. Terminals for  $V_{DD}$ , WL, two BLs, and two storage nodes (VL and VR) can be accessed (Fig. 1), so that all 6 transistors as well as SNM can be measured. The SOI thickness is 12nm, BOX thickness is 10nm, and  $T_{INV}$  is 2.8nm. For reference, conventional bulk SRAM DMA TEG with the same dimensions was also fabricated. Average  $V_{TH}$ 's of SOTB and bulk FETs are adjusted to the same value (approximately 0.29V) by substrate bias for fair comparison.

Vmin of each cell was measured by the following method [12]. Initially, HIGH was written to one of the storage nodes (VL, for example). Then,  $V_{DD}$  was lowered and it was checked when the state of VL was flipped. During this procedure, both word line ( $V_{WL}$ ) and bit line voltages ( $V_{BL}$ ) were kept at  $V_{DD}$ . The same operation was done for the other node (VR). Vmin of the cell is defined as the minimum  $V_{DD}$

where the states in both cases are not flipped. It turned out that Vmin's of some of very stable cells could not be measured, because the cells were too stable (Vmin  $< \sim 0.1$ V for SOTB) and there were forward pn-junction current due to substrate bias (Vmin  $< \sim 0.3$ V for bulk).

#### 3. Results

Fig. 2 shows  $V_{TH}$  distributions of cell transistors in 1k SOTB and bulk SRAM. Obviously, SOTB FETs have smaller  $V_{TH}$  variability. Before measuring Vmin's, SNMs were measured. Fig. 3 shows butterfly curves of 1k SOTB and bulk SRAM cells at  $V_{DD} = 0.4V$  and Fig. 4 shows SNM distributions at  $V_{DD} = 0.4V$ . SOTB cells have clear "eyes" in butterfly curves even at 0.4V, while many bulk cells show zero SNM at 0.4V, which makes the direct quantitative comparison of the worst cells very difficult.

Fig. 5 shows the correlation between measured SNM and Vmin. Good correlations are found, especially in unstable cells with high Vmin's. Please note that the worst Vmin in 1k cells is 0.242V and 0.482V for SOTB and bulk, respectively. This is the direct quantitative comparison of cell array between SOTB and bulk. By utilizing SOTB, Vmin of cell array can be reduced by half, which is a great advantage of SOTB SRAM over bulk SRAM.

Fig. 6 shows butterfly curves of a stable cell (Vmin = 0.138V) and the worst cell (0.242V) of SOTB. The stable cell has a clear eye even at 0.2V, while the worst cell has no eye at 0.2V, as expected. Fig. 7 shows butterfly curves of the worst bulk cell, which shows no eye even at 0.4V.

## 4. Conclusions

The stability of the worst cells in SOTB and bulk SRAM is directly compared by measuring Vmin's of the SRAM cells. It is found that the worst Vmin can be reduced by half by introducing SOTB thanks to reduced  $V_{TH}$  variability.

### Acknowledgements

This work is supported by the Ministry of Economy, Trade and Industry (METI) and New Energy and Industrial Technology Development Organization (NEDO).

## References

- [1] A. J. Bhavnagarwala et al., IEEE JSSC, p.658, 2001.

- [2] F. Tachibana et al., JJAP, 44, p.2147, 2005.

- [3] A. Bhavnagarwala et al., IEDM., p.675, 2005.

- [4] A. Asenov et al., VLSI Tech. Symp., p.87, 2007.

- [5] X. Song et al., IEDM, p.62, 2010.

- [6] T. Hiramoto et al., IEEE TED, 58, p.2249, 2011.

- [7] S. Jain et al., ISSCC, p. 66, 2012.

- [8] R. Tsuchiya et al., IEDM, p. 631, 2004.

- [9] T. Mizutani et al., Silicon Nano. Workshop, p. 71, 2012.

- [10] Y. Yamamoto et al., to be presented in VLSI Tech. Symp., 2013.

- [11] Y. Yamamoto et al., VLSI Tech. Symp., p. 109, 2012.

- [12] A. Kumar et al., to be presented in Si Nano. Workshop, 2013.

- 743 -