# Self-Assembly Study to Precisely Align Dies Having Microbump Covered with Non-Conductive Film for Advanced Chip-to-Wafer 3D Integration

Yuka Ito<sup>1, 2</sup>, Takafumi Fukushima<sup>3</sup>, Kang-Wook Lee<sup>3</sup>, Koji Choki<sup>2</sup>, Tetsu Tanaka<sup>1, 4</sup>, and Mitsumasa Koyanagi<sup>3</sup>

<sup>1</sup>Department of Bioengineering and Robotics, Graduate School of Engineering, Tohoku University

6-6-01 Aza-Aoba, Aramaki, Aoba-ku, Sendai 980-8579, Japan

Phone: +81-22-795-6909, E-mail: link@lbc.mech.tohoku.ac.jp

<sup>2</sup>Sumitomo Bakelite Co., Ltd.,

20-7 Kiyohara Industrial Park, Utsunomiya 321-3231, Japan

<sup>3</sup> New Industry Creation Hatchery Center, Tohoku University

<sup>4</sup>Deptartment of Biomedical Engineering, Graduate School of Biomedical Engineering, Tohoku University

#### **Abstract**

We demonstrated self-assembly new for high-throughput and high-yield multichip-to-wafer 3D stacking using chips covered with a non-conductive film (NCF) on the top surface. The NCF is a promising candidate to completely fill between small microbumps of the chips and is essential for realizing fine-pitch microbump-to-microbump interconnections. 3-mm-square chips laminated with the NCF were precisely self-assembled to wafers within 4 µm by surface tension of water. The results indicate that the self-assembly technique using chips with the NCF can achieve not high-accurate only chip alignment but high-strength chip bonding at once.

# 1. Introduction

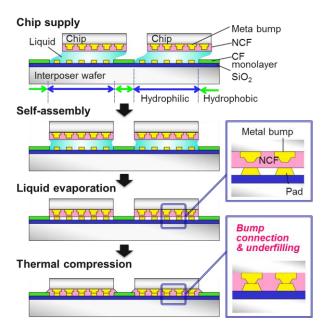

Chip-to-wafer integration is an attractive 3D integration method to realize high-production yield owing to the usage of known good dies (KGDs). In particular, advanced multichip-to-wafer method using self-assembly with liquid surface tension is a promising technique for 3D integration, which can also overcome trade-off between throughput and alignment accuracy in conventional mechanical assembly [1]. When we use chips with metal microbumps for multichip self-assembly [2-5], the chips are thermally compressed and interconnected to the corresponding wafers with metal microbumps. Then, an "underfilling" process with liquid resins using capillary force is required for injecting the resins into the resulting narrow gap between the chips and wafers in order to obtain highly-reliable microbump interconnections. However, as the gap and bump sizes/pitches recently become smaller and smaller, conventional capillary underfilling suffers from low throughput and void generation. Therefore, capillary underfilling is not suitable for chip-to-wafer 3D integration. NCF is often alternatively used for the capillary underfill resins and can be formed in wafer-level. In this paper, we propose new self-assembly using chips with metal microbumps covered with NCF for advanced chip-to-wafer 3D integration. Figure 1 shows chip self-assembly with NCF onto SiO<sub>2</sub> assembly areas on a wafer. Immediately after self-assembly and the subsequent thermal compression, NCF is ejected from the bump top to give microbump joining and underfilling is simultaneously completed. This method can skip bothering one-by-one underfilling processes after bump connection. Here, we demonstrate self-assembly with chips having NCF and evaluate alignment accuracies.

### 2. Experimental

Assembly wafers and chips used in this study were prepared from Si wafers with a hydrophilic  $\mathrm{SiO}_2$  layer and metallized vernier scales for alignment accuracy evaluation. In assembly wafer fabrication, hydrophobic fluorocarbon areas surrounding the hydrophilic assembly areas were patterned by lithography and lift-off processes. In chip fabrication, a NCF was laminated on a 140-µm-thick wafers by a vacuum laminator. After that, 3-mm-squire chips were diced by blade dicing with chip size accuracies within  $\pm 2.5$  µm (hereinafter referred to as "NCF chip").

In self-assembly processes, we employed an industrial scalar robot to sort the chips from chip trays on which KGDs without dimensional errors and visible defects such as particles and scratches were arrayed. A 0.4 µl ultrapure water droplet was provided onto the hydrophilic assembly area on the assembly wafers, and then, the chips were roughly pre-aligned until the NCF surface was contacted to the water droplet. After keeping a 100-µm height between the chips and the wafers, the chips were released to the assembly areas. After spontaneous water evaporation, alignment accuracies of the assembled chips were evaluated by observing vernier pattern with an IR microscopy. For comparison, 140-µm-thick chips having a SiO<sub>2</sub> layer on the top surface and diced by plasma etching within ±2.0 μm (hereinafter referred to as "SiO2 chip") were also evaluated. We have demonstrated self-assembly-based 3D integration [1-5], where multichip self-assembly with submicron accuracies can be given by the hydrophilic SiO<sub>2</sub> chips.

### 3. Results and Discussion

Size precisions of  $SiO_2$  chips and NCF chips after dicing were 2999.0  $\pm 2.0~\mu m$  and 2999.9  $\pm 3.0~\mu m$ , respectively. The former size precision was influenced mainly by lithography, whereas the latter size precision was influenced by blade dicing. The NCF chips were rapidly assembled to the

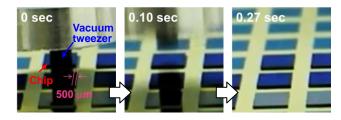

assembly areas on the wafers by water surface tension as well as the  $SiO_2$  chips. Figure 2 shows that a NCF chip with 500- $\mu$ m-initial displacement swam to the assembly area for 0.27 sec. The NCF chips can be precisely assembled to the corresponding hydrophilic areas even by 1000- $\mu$ m initial displacement, but that depends on self-assembly conditions such as chip release height, cleanliness on chips and wafers, water volume, robot sorting speed, and so on.

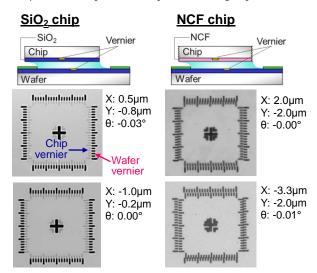

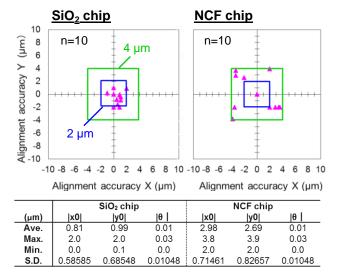

Figure 3 shows photomicrographs of vernier patterns after self-assembly. Figure 4 shows alignment position maps when we use 10 SiO<sub>2</sub> chips and NCF chips. Alignment accuracies for the SiO2 chips were 0.9 µm on average and 2.0 µm at worst. In contrast, the NCF chips were aligned with an average accuracy of 2.8 µm and within 3.9 µm in the worst case. The NCF chips could be also successfully assembled with high alignment accuracy as well as the SiO<sub>2</sub> chips. The difference in alignment accuracies between both chips mainly derived from chip size precisions. In addition, slight NCF undulation and fractions peeling could be found on the dicing edge due to viscoelasticity of the NCF and less adhesion strength of the NCF to Si or SiO2. However, the NCF chips provided good prospects to obtain higher chip alignment accuracy by optimization of chip fabrication processes.

## 4. Conclusions

We preformed fundamental studies of self-assembly with NCF chips by water surface tension to achieve micobump-to-microbump interconnections for advanced chip-to-wafer 3D integration. 3-mm-square NCF chips were self-assembled to hydrophilic areas formed on wafers within 2-3  $\mu$ m. The alignment accuracies can further increase and we would realize higher alignment accuracies comparable to SiO<sub>2</sub> chips employed in our previous works

Fig. 1 Conceptual image of self-assembly using chips having metal microbump covered with NCF to the wafer.

using the NCF chips.

#### References

- [1] T. Fukushima et al., IEDM Tech. Dig., (2005) 359.

- [2] T. Fukushima et al., IEDM Tech. Dig., (2007) 985.

- [3] T. Fukushima et al., *IEDM Tech. Dig.*, (2009) 349.

- [4] Y. Ito et al, Jpn. J. Appl. Phys. 52 (2013) 04CB09.

- [5] T. Fukushima, et al., IEEE Trans. Electron. Dev., 59 (2012) 2956.

Fig. 2 Self-assembly behavior of a NCF chip to wafer by 500- $\mu$ m-initial displacement captured with high-speed camera.

Fig. 3 Vernier images on  $SiO_2$  chip (left) and NCF chips (right) through IR microscopy.

Fig. 4 Alignment position maps between SiO<sub>2</sub> chips without NCF (left) and NCF chip (right).