## High speed silicon modulators for integrated transceivers

- G T Reed (1), D J Thomson(1), F Y Gardes(1), G Z Mashanovich(1), Y. Hu(1), Li K(1), P W Wilson(1), L Zimmermann(2), H Porte(3), B Goll(4), H Zimmermann(4), D. Knoll(2), S. Lischke(2), S-W Chen(5), S S H Hsu(5), J-M Fedeli(6), K Debnath(7), T F Krauss (8), L O'Faolain(7).

- (1) Optoelectronics Research Centre, University of Southampton, Southampton, Hampshire, SO17 1BJ, UK (2) IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

- (3) PHOTLINE Technologies, ZI Les Tilleroyes Trépillot, 16 rue Auguste Jouchoux, 25000 Besançon France (4) Vienna University of Technology, EMCE, Guβhausstr. 25/354, A-1040 Vienna, Austria

- (5) Electrical Engineering, National Tsing Hua University Sec. 2, Kuang-Fu Rd., Hsinchu, Taiwan (6) CEA, LETI, Minatec Campus, 17 Rue des Martyrs, 38054 GRENOBLE FRANCE

- (7) School of Physics and Astronomy, University of St Andrews, Fife, Scotland, KY16 9SS

(8) Department of Physics, University of York, Yorkshire, YO10 5DD, UK

## <u>Abstract</u>

We present a summary of our recent work on silicon optical modulators, integration with modulator drivers, and the first silicon modulator fully integrated with BiCMOS. Finally we discuss multiplexed photonic crystal modulators for ultra-low power operation.

## Introduction

Silicon modulators are essential devices communications silicon photonics based short reach interconnect. We discuss several modulators that enable different short reach applications to be targeted. In some applications, such as highly multiplexed interconnection of microprocessor cores, modulator power consumption and footprint are of paramount importance. On the other hand, if relatively few channels are required for interconnect of remote devices, or in some point to point server applications, data rate and temperature insensitivity may be more important than footprint. Therefore, we will also discuss a novel multiplexer/demultiplexer that is suited to small channel counts.

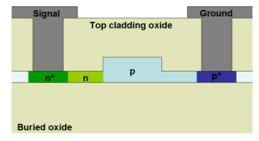

Reasons for increasing the data rate of the modulation include the potential for increased channel efficiency and reductions in power consumption. We have previously presented modulators with data rates up to 50Gb/s (e.g.[1], [2], [3]). A schematic of the cross section of one example of such a device is shown in figure 1, developed in the European project "HELIOS".

Fig. 1 Modulator cross section;

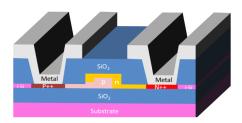

Similarly, we have developed polarisation independent modulators within a project funded by the UK "Engineering and Physical Sciences Research Council (EPSRC) entitled UK Silicon Photonics (UKSP). Figure 2 shows a typical modulator cross section. The thicker silicon guiding layer (400nm vs 220nm) supports both TE and TM polarisation modes, and the device can be designed for polarisation insensitive performance. The device comprises a "wrap-around" pn junction, which facilitates optimisation for polarisation independent performance [3].

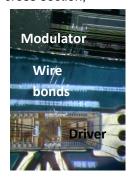

Work has also been carried out on the integration of modulators with electronics, both as back-end and front-end processes. Within the UKSP project a Mach Zehnder modulator (MZM) carrier depletion silicon optical modulator has been integrated with CMOS driving electronics using a wire bonding approach. An optical microscope image of this is shown in figure 3a. The MZI used is asymmetric and has 3.5mm phase modulators in either arm. Multimode interference (MMI) structures are used to split and recombine the light in the MZI arms. The dual drive CMOS driver was fabrication using the IBM-8RF 130nm process [4]. Operation at 10Gbit/s as targeted by the design of the driver is demonstrated.

Fig. 2 Modulator cross section;

Also within UKSP a full single channel link with transmitter and receiver integrated electronics is demonstrated. The TIA was fabricated using 180nm TSMC technology [5]. An optical microscope image of the receiver is shown in figure 3b.

In the case of our front-end integration work, we have integrated a modulator driver with the modulator design of figure 1, into a BiCMOS process. Photonic SOI is not suitable for integration with high-performance bipolar transistors for two reasons:

a) (b)

Fig. 3. Optical microscope image of the wire bonded carrier depletion modulator and CMOS driver (a) and photodetector and TIA (b).

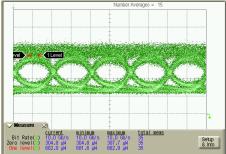

incompatibility with collector fabrication and the higher thermal resistance compared to bulk Silicon substrates normally used for high-performance BiCMOS processes. Therefore we developed a process combining local-SOI areas with bulk-Si areas. The starting substrate was photonic SOI, which is etched down to the handling wafer and then locally regrown by Si-epitaxy, finishing with polishing to obtain surfaces at the same height for local-SOI and for bulk Silicon. After local-SOI fabrication the BiCMOS process follows a modified standard flow. Figure 4 shows an optical eye diagram produced from the integrated system, at 10Gbits/s, with modulation depth at 8.4dB, when operated at quadrature. Using this method it was possible to integrate photonics and electronics into the same substrate.

Figure 4. Output optical eye diagram from the modulator at 10Gbit/s.

For ultra low power applications we have demonstrated a series of photonic crystal based multiplexed modulators, by integrating with a single low refractive index waveguide. To date only low data rates have been demonstrated but the modulators should be improved via implementation of carrier depletion structures. The AC component of the power consumption was calculated as ~0.6fJ/bit at 1Gbit/s [6].

## References

- 1. D. J. Thomson, et al, Optics Express, vol. 19, pp. 11507-11516, 2011.

- 2. D. J. Thomson, et al, *IEEE Photonics Technology Letters*, vol. 24, pp. 234-236, 2012.

- 3. F. Y. Gardes, et al Optics Express, vol. 19, pp. 11804-11814, 2011

- 4. K. Li and P. Wilson, IEEE International Symposium on Circuits and Systems, ISCAS, (2013).

- 5. S.S.H. Hsu et al., IEEE Symposium of RF Integration Technology, (2011).

- 6. K. Debnath, et al, *Optics Express*, vol. 20, pp. 27420-27428, 2012.