# Cell Pitch Design Limitation for Electrical and Thermal Characteristics in Super Junction MOSFET

Jongmin Geum<sup>1</sup>, Sinsu Kyoung<sup>1</sup>, Eun Sik Jung<sup>2</sup>, Yongtae Kim<sup>3</sup> and Man Young Sung<sup>1</sup>

<sup>1</sup> Korea Univ.

School of Electrical Engineering

Korea University Anam-Dong, Seongbuk-Gu, Seoul 136-701, Republic of Korea

Phone: +82-3290-3782 E-mail: semicad@korea.ac.kr

<sup>2</sup> Maple Semiconductor

Bucheon Technopark Ssangyoung III, 36-1, Samjeng-Dong, Seoul 136-701, Republic of Korea

<sup>3</sup> Semiconductor Materials & Devices Lab., Korea Institute of Science & Technology

Seoul 131, Korea

## Abstract

In Super Junction (SJ) MOSFET, Cell pitch parameter has to be considered because of the on-resistance characteristics. Unlike conventional Power MOSFET, SJ MOSFET has opposite tendency of the on-resistance characteristics when cell pitch is reduced. In this paper, electrical and thermal characteristic effects of the cell pitch degradation in SJ MOSFET are simulated to confirm opposite tendency using TCAD tool.

# 1. Introduction

The most important issue for semiconductor power devices is reducing the conduction loss that occurs when it turned on[1-3]. SJ MOSFET has far superior electrical characteristics, such as higher voltage and lower on-resistance, to those of conventional high-voltage MOSFETs[7]. The power electronics market is demanding low on-resistance at an appropriate voltage level. So on-resistance is the most important parameter when SJ MOSFET is designed. In conventional Power MOSFET, reducing cell pitch parameter has been used to decrease on-resistance[8]. But in SJ MOSFET, reducing cell pitch makes on-resistance increases because device current path area is decreasing with steady value of on-state depletion layer width[9]. Additionally, reducing cell pitch results in a higher breakdown voltage and thermal resistivity. In this paper, cell pitch limitation is proposed using relationship of cell pitch, electrical and thermal characteristics confirmed by TCAD simulation.

## 2. Result

#### 2.1 Basic analysis

On-resistance analysis in SJ MOSFET differs from conventional MOSFET due to P pillar structure. Reducing cell pitch, n pillar width is almost same with that of non-reducing cell pitch. That result can be assumed in eq.(1)[9].

$$R_{on} = \rho_D L_D \left( \frac{W_{Cell}}{W_N - W_{Depletion-N}} \right)$$

(1)

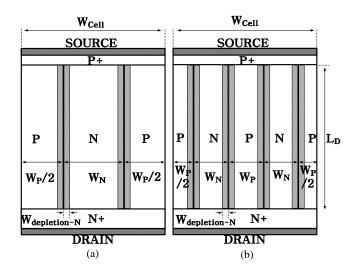

$W_{Cell}$  means full cell width of SJ device,  $W_{\rm N}$  is the n pillar width and  $W_{Depletion-N}$  is the depletion width of on-state drain voltage biased in the N, P pillar junction area. Because the  $W_{Depletion-N}$  parameter is related in forward bias drain-source voltage,  $W_{Depletion-N}$  is constant when cell pitch is decreasing. So Ron is increasing with both  $W_{Cell}$  and  $W_{\rm N}$  reduced due to uniform  $W_{Depletion-N}$ . It can be observed in Fig.1.

Fig. 1 Relationship of cell pitch decreasing and depletion width. (a) N pillar path =  $W_N$ -2 $W_{Depletion-N}$ . (b) N pillar path =  $W_N$ -4 $W_{Depletion-N}$

In Fig.1, (b) structure has half of the cell pitch compared with that of (a). But  $W_{DN}$  of (b) structure is 2 times larger than that of (a). So reducing cell pitch is affected on on-resistance characteristics degradation in SJ MOSFET.

Cell pitch modulation also affects thermal resistivity.

When current path is decreasing, the same current is flowing in narrower area than that of wider one. So in narrower cell pitch, Thermal resistivity is larger than wider one.

## 2.2 Simulation result

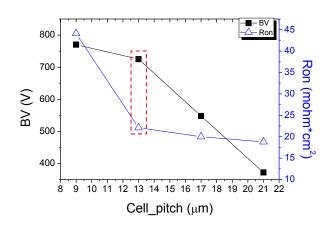

In order to study the cell pitch limit according to the electrical and thermal characteristics, the SJ MOSFET structure for 600V is simulated. The doping concentration of the N, P pillar is  $4.73 \cdot 10^{15}$  cm<sup>-3</sup> and  $5.93 \cdot 10^{15}$  cm<sup>-3</sup>. Drift depth is 59µm and 9, 13, 17, 21µm cell pitch are simulated. As shown in Fig.2, on-resistance is rapidly increasing at 13 µm cell pitch and also increasing breakdown voltage in trade-off relation when cell pitch is reduced. To achieve best breakdown voltage characteristic, cell pitch has to be decreasing. But on-resistance in SJ MOFET is more drastically increasing compared with the breakdown voltage about two times. So cell pitch limitation is needed to achieve best on-resistance characteristics. Optimum point of cell pitch is 13 µm at relation of breakdown voltage versus on-resistance in Fig.2.

Fig. 2 Breakdown voltage and on on-resistance characteristics of cell pitch modulation.

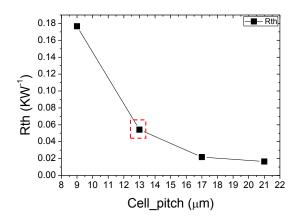

Fig. 3 Thermal resistance characteristics of cell pitch modulation.

This cell pitch limitation also is needed in Thermal resistance characteristic. As shown in Fig.3, Thermal resistivity is rapidly increasing with cell pitch shrinking. This simulation is based on same area and current,  $1 \text{ cm}^2$  and 100 A. When cell pitch is reducing, cross sectional area of current path is decreasing and heat generation is also increasing. So higher T<sub>1</sub>-T<sub>2</sub> is achieved and R<sub>th</sub> is abruptly increasing. Cell pitch limitation has to be needed in thermal characteristics by high thermal resistance, R<sub>th</sub>. 13 µm cell pitch is optimum point of heat characteristics as shown in Fig.3.

## 3. Conclusions

Conventional Power MOSFET can have low on-resistance characteristic using cell pitch reducing. But in SJ MOSFET, reducing cell pitch cause increasing of on-resistance due to decreasing of N pillar width with uniform on-state depletion width. And cell pitch degradation cause increasing of thermal resistivity too. So Cell pitch limitation has to be needed. In this paper, 600V SJ MOSFET has optimum point of 13  $\mu$ m cell pitch. This cell pitch limitation can apply with other voltage size devices in further paper issues.

## Acknowledgements

This work was supported by the IT R&D program of the Ministry of Industry, Trade and Resource [1003571, Development of High Voltage/ Current Power Module and ESD for BLDC Motor] and supported by the 2011 IT-SOC program of the Ministry of Industry, Trade and Resource

## References

- [1] H.W.Lee, E.S. Jung, R. Oh, and M.Y. Sung, J.KIEEME, vol.25, No.5, pp.340-344(2012)

- [2] S.S. Kyoung, J.S.Lee, S.H. Kwak, E.G. Kang and M.Y.Sung, IEEE Electron Device, vol.30, No.1, pp.82 (2009)

- [3] J.S. Lee, E. G. Kang, and M.Y. Sung, J.KIEEME, vol.2, No.5, pp.403(2007)

- [4] J.S. Lee, E.G. Kang, and M.Y. Sung, J.KIEEME. vol.2, No.5, pp.403(2007)

- [5] J.S. Lee and M.Y. Sung, ELEX, Vol.6, No.23, pp.1621-1625 (2009)

- [6] J.S. Lee, S.S. Kyoung, E.G. Kang and M.Y. Sung, J.KIEEME, Vol.21, No.10, pp.889-895(2008)

- [7] P.N. Kondecar, TENCON Vol.4, pp1455-1458(2003)

- [8] B.J. Baliga, Fundamentals of Power Semiconductor devices(2008)

- [9] B.J. Baliga, Advanced Power MOSFET Concepts(2010)