# An Explicit Compact Model for High-Voltage LDMOS

Hongtao Zhou<sup>1</sup>, Xing Zhou<sup>1</sup> and Francis Benistant<sup>2</sup>

<sup>1</sup> School of Electrical and Electronic Engineering, Nanyang Technological University 50 Nanyang Avenue, Singapore 639798 Phone: +65-6790-4532 Email: exzhou@ntu.edu.sg <sup>2</sup> GLOBALFOUNDRIES Singapore Pte Ltd 60 Woodlands Industrial Park D Street 2, Singapore 738406

## Abstract

In this paper, we present an analytical DC model for high-voltage (HV) LDMOS. The proposed model is based on explicit calculations of surface potential, drift resistance and internal drain voltage. LDMOS characteristics such as trans-conductance sharp peak and quasi-saturation are well captured. The model is robust, efficient and showing good agreement with both numerical and measured data.

## 1. Introduction

Lateral double-diffused MOSFETs (LDMOS) are widely used in applications such as automotive and RF circuits. Numerous compact models have been reported over the past few decades. One approach is to construct a sub-circuit so that its terminal behaviors match the ones of a LDMOS [1]. Another approach is to introduce an internal node between the channel and drift region (K-point) [2-5]. In both cases, iterations are usually required and efforts have to be made to ensure convergence and improve efficiency.

In order to avoid iterations and eliminate any convergence issues, we present a novel analytical approach by introducing a unified regional drift resistance. Separate equations for each operating region can be easily formulated and then unified into a single-piece expression. This enables the explicit calculation of K-point voltage, improves robustness and efficiency of the model.

# 2. Formulations

The LDMOS device is divided into the channel and drift regions. Applying KCL at the K-point, the following equation can be derived:

$$\mu C_{ox} \frac{W}{L} \Big( q_{in,s} - \frac{1}{2} A_{b,s} V_{ks} + V_{th} A_{b,s} \Big) V_{ks} = \frac{V_{ds} - V_{ks}}{R_{drift}} \quad (1)$$

In eq. (1),  $q_{in,s}$  is the normalized inversion charge density obtained from the surface potential solution at the source side [6].  $R_{drift}$  is the unified drift resistance calculated by smoothly joining the linear, quasi-saturation and saturation regional resistance, given as

$$R_{drift} = \vartheta_{max} \left( R_{lin}, R_{qsat}, R_{sat} \right) \tag{2}$$

$R_{lin}$  is the drift region resistance without any lateral field effect. It is modulated by the gate and body bias, and

this effect may vary due to the structural differences in LDMOS.  $R_{qsat}$  is the high lateral-field drift resistance obtained with the assumption that all the voltage is dropped across the drift region. As reported in [5], the current in drift region may increase beyond saturation.  $R_{sat}$  is the resistance beyond linear channel region, and it is proportional to the drain bias with a slope equal to the saturation current. Their expressions are shown below, and they are only valid in their specific regions.

$$R_{lin} = R_{ov} \left( 1 + V_{gs} \theta_1 \right) \left( 1 + V_{bs} \theta_2 \right) + R_{dr} \left( \frac{L_{dr}}{W} \right) \tag{3}$$

$$R_{qsat} = \frac{V_{ds}}{A_f (V_{ds} - v_{sat} (L_{ov} + L_{dr}) / \mu_{dr}) + v_{sat} (L_{ov} + L_{dr}) / (R_{lf} \mu_{dr})}$$

(4)

$$R_{sat} = \frac{V_{ds} - V_{ds,eff}}{I_{ch}}$$

(5)

K-point here is defined at the end of the linear channel instead of the physical point at the body-drift junction, and its voltage can be calculated by solving eq. (1) analytically. Once  $V_{ks}$  is obtained, its value can be substituted back into eq. (1) to obtain the drain current.

## 3. Model Verification

Comparison with TCAD Simulations

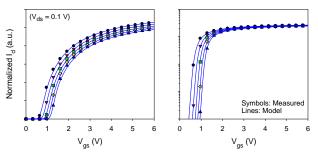

In order to verify the compact model, we conducted TCAD simulations to compare IV curves in DC operation. The numerical device has a channel length of 1 $\mu$ m, a gate-overlap length of 1 $\mu$ m and a drift-region length of 2 $\mu$ m. The drift region doping concentration is set to a constant at  $1 \times 10^{16}$  cm<sup>-3</sup>, and the channel doping peak is set at  $1 \times 10^{18}$  cm<sup>-3</sup>.

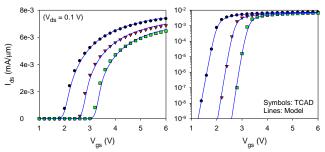

Fig 1.  $I_{ds}$ - $V_{gs}$  curves in linear region ( $V_{ds} = 0.1$  V) at  $V_{bs} = 0, -1, -2$  V.

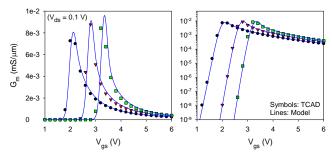

Fig 2.  $G_m - V_{gs}$  curves in linear region ( $V_{ds} = 0.1$  V) at  $V_{bs} = 0, -1, -2$  V.

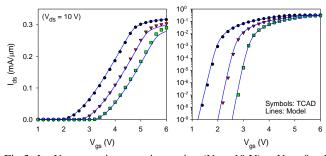

Fig 3.  $I_{ds}-V_{gs}$  curves in saturation region ( $V_{ds} = 10$  V) at  $V_{bs} = 0, -1, -2$  V.

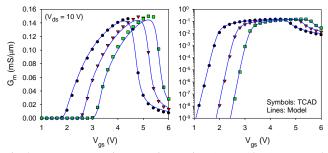

Fig 4.  $G_m - V_{gs}$  curves in saturation region ( $V_{ds} = 10$  V) at  $V_{bs} = 0$ , -1, -2 V.

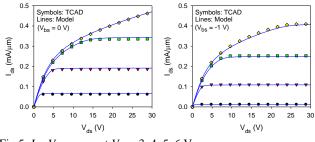

Fig 5.  $I_{ds}$ - $V_{ds}$  curves at  $V_{gs}$  = 3, 4, 5, 6 V.

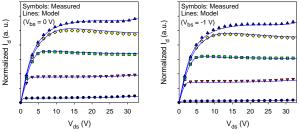

## Comparison with Measured Data

The model is also calibrated with a 30V-LDMOS device. As shown in the following figures, the calculated current shows excellent consistency with the measured data. In addition, lattice self-heating effect is included through a standard thermal resistor. Substrate current is calculated by considering impact ionization effects in both channel and drift regions.

Fig 6.  $I_d$ – $V_{gs}$  curves in saturation region ( $V_{ds} = 0.1$  V) at  $V_{bs} = 0$ , -0.5, -1, -1.5, -2 V.

Fig 7.  $I_d - V_{ds}$  curves at  $V_{gs} = 1.2, 2.4, 3.6, 4.8, 6.0$  V.

#### 4. Conclusions

In this paper, an explicit compact model for HV-LDMOS is presented. Different from conventional sub-circuit and iterative approaches, expressions for drift resistance are derived for specific regions and later unified. This novel approach enables the explicit calculation of the K-point voltage and terminal current. Without iterations, the model is highly robust and efficient, and its accuracy has been well demonstrated by comparing to both numerical and experimental data.

#### Acknowledgements

This work is supported by a Research Scholarship from GLOBALFOUNDRIES Singapore Pte Ltd awarded to Hongtao Zhou.

#### References

- W. Yao, G. Gildenblat, C. C. McAndrew, and A. Cassagnes, IEEE Transactions on Electron Devices 59 (3), 542-550 (2012).

- [2] A. C. T. Aarts and W. J. Kloosterman, IEEE Transactions on Electron Devices 53 (4), 897-902 (2006).

- [3] C. Anghel, N. Hefyene, A. M. Ionescu, M. Vermandel, B. Bakeroot, J. Doutreloigne, R. Gillon, S. Frere, C. Maier, and Y. Mourier, presented at the 2001 International Semiconductor Conference, October 9, 2001 October 13, 2001, Sinaia, Romania, 2001 (unpublished).

- [4] Y. S. Chauhan, C. Anghel, F. Krummenacher, C. Maier, R. Gillon, B. Bakeroot, B. Desoete, S. Frere, A. B. Desormeaux, A. Sharma, M. Declercq, and A. M. Ionescu, Solid-State Electronics 50 (11-12), 1801-1813 (2006).

- [5] A. Tanaka, Y. Oritsuki, H. Kikuchihara, M. Miyake, H. J. Mattausch, M. Miura-Mattausch, Y. Liu, and K. Green, IEEE Transactions on Electron Devices 58 (7), 2072-2080 (2011).

- [6] G. H. See, X. Zhou, K. Chandrasekaran, S. B. Chiah, Z. Zhu, C. Wei, S. Lin, G. Zhu, and G. H. Lim, IEEE Transactions on Electron Devices 55 (2), 624-631 (2008).