# A Proposal of a Forming-Free Resistive Switching Memory based on Breakdown and Anodic Reoxidization of thin SiO<sub>2</sub> on NiSi<sub>2</sub> Electrode using CeO<sub>x</sub> Buffer Layer

M. S. Hadi, S. Kano, C. Dou, K. Kakushima, P. Ahemt, Y. Kataoka,

A. Nishiyama, N. Sugii, H. Wakabayashi, K. Tsutsui, K. Natori, H. Iwai Tokyo Institute of Technology, 4259 Nagatsuta, Midori-ku, Yokohama 226-8502, Japan

Phone: +81-45-924-5847 E-mail: hadi.m.aa@m.titech.ac.jp

### Abstract

A novel forming-free resistive memory with a large ON/OFF ratio of  $10^4$  is proposed based on breakdown and anodically reoxidized thin SiO<sub>2</sub> layer using CeO<sub>x</sub> buffer layer and silicide electrodes. Low resistive state (LRS) is achieved by hard breakdown of the thin-SiO<sub>2</sub> layer owing to high dielectric constant of the CeO<sub>x</sub> layer. By applying opposite bias to the electrode, high resistive state (HRS) can be reverted back by local anodic oxidation of the breakdown spot by high oxygen ion conductivity of CeO<sub>x</sub> layer.

## 1. Introduction

Resistive memory has been focused as one of the non-volatile memories for next-generation, owing to low voltage and fast operation with excellent retention properties [1]. Base on the conductive-filament switching model, HRS and LRS are determined by the annihilation and creation of the oxygen vacancies at the tip of filaments within the oxides, which is commonly created during initial forming process [2]. The HRS/LRS ratio is strongly dependent on the forming process, and is sensitive to the compliance current as it determines the size of the filaments [3]. Forming-free devices have been presented using defect-rich AlON at the cost of HRS/LRS ratio [4]. We propose a novel structure to achieve forming-free, high HRS/LRS ratio and fast operation using a laminated structure of a thin SiO<sub>2</sub> with CeO<sub>x</sub> buffer layer and silicide electrode.

## 2. Device Fabrication

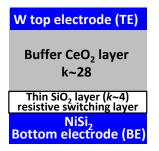

Fig. 1 shows the structure of fabricated resistive switching devices, which consists of W top layer and CeO<sub>x</sub> buffer layer. NiSi<sub>2</sub> was selected as a bottom electrode (BE) as pure-SiO<sub>2</sub> can be easily created and out-diffusion of Ni atom is suppressed [5]. For comparison, devices with TiN BEs were also fabricated as references. CeO<sub>x</sub> films with different thicknesses were deposited on BEs by e-beam evaporation. Patterned W top electrodes (TE) with an area of  $10 \times 10 \mu m^2$  were used to measure the switching behaviors, including cycling tests and switching speed measurements.

#### 3. Results and Discussion

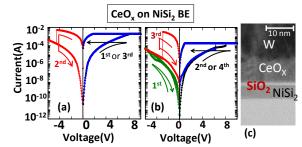

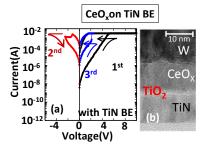

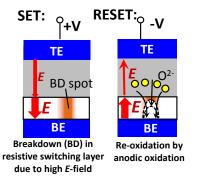

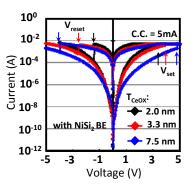

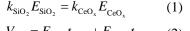

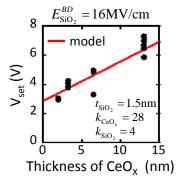

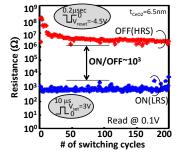

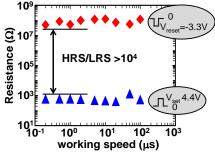

Fig. 2 shows the current-voltage (IV) curve of devices with  $NiSi_2$  BE. Initial forward and backward voltage sweep to positive voltage showed a change in resistive states from HRS to LRS. A sudden decrease in current with voltage application to reverse bias indicates a bipolar-type switching. By applying third voltage sweep to positive direction showed current behavior identical to the initial current, therefore a forming-free resistive switching is achieved. TEM image indicates the formation of 1.5-nm-thick SiO<sub>2</sub> between CeO<sub>x</sub> and NiSi<sub>2</sub> BE, reactively formed by the catalytic effect of  $CeO_x$  [6]. On the other hand, devices with TiN BE required forming process for resistive switching, due to the formation of TiO<sub>2</sub>, which has a high dielectric constant (fig.6). Therefore, silicide-BE to form a thin SiO<sub>2</sub> layer is the key to achieve forming-free operation. A model to explain the obtained switching behavior is shown in fig. 4. For set-process, high electric field induces a breakdown to the thin SiO<sub>2</sub>, due to low dielectric constant  $(k\sim4)$ , to change the state to LRS. For reset-process, oxygen ions from CeO<sub>2</sub> layer induce local anodic oxidation of the breakdown spot to create SiO<sub>2</sub> and change the state to HRS. The voltage to induce breakdown in the thin  $SiO_2$  layer  $(V_{set})$  can be explained by electrostatics with eq. (1~3), using hard breakdown field of  $SiO_2$  ( $E_{BD}$ ). Fig. 5 shows the IV curves of devices with different CeO<sub>x</sub> thicknesses, and the V<sub>set</sub> is summarized in fig. 6. Cyclic test and pulse switching measurement showed no degradation at least down to 200 nsec (limited to our measurement setup) with on-off ratio of  $10^4$ , indicating the breakdown and oxidation can be reliably processed in a short period (fig. 7, 8).

Based on the above model, the requirements for material selection are discussed (fig. 9). For set-process, buffer high-k layer should have high dielectric constants to induce breakdown in thin  $SiO_2$  layer, and high breakdown field so as not to form conduction filaments in the buffer high-k layer. Resistance of HRS is determined by the insulating property of  $SiO_2$ , so that silicides which form pure  $SiO_2$  are preferable. For reset-process, buffer layer should have a high oxygen ion conductivity to induce anodic oxidation to the breakdown spots. As LRS is mainly limited by the electron conduction of buffer high-k layer, narrow bandgap is preferable to lower the resistance, which is usually the case for high-k materials.

### 3. Conclusions

We have successfully demonstrated a forming-free resistive switching behavior using a device with thin  $SiO_2$ and a  $CeO_x$  on  $NiSi_2$  electrode. Set and reset processes are achieved by breakdown of thin  $SiO_2$  and anodic oxidation of the breakdown spot, so that it gives a high HRS/LRS ratio owing to the excellent insulating property of  $SiO_2$ . **References**

# [1] L. Goux, et al., VLSI symp. tech., p. 24 (2011).

- [2] W. Kim, et al., VLSI symp. tech., p.22 (2011).

- [3] W. H. Liu, et al., IEDM p. 135 (2009).

- [4] W. Kim, et al., VLSI symp. tech., p. 22

- [5] W. J. Strydom, et al., Solid-State Electron., 30, p. 947 (1987).

- [6] T. Chikyow, et al., APL, 65, p. 1030 (1994).

Fig.1 A schematic illustration of the fabricated resistive switching device. A thin  $SiO_2$  layer is formed by oxidation of  $NiSi_2$  BE.

Fig.2 (a) I-V curve of the device with NiSi<sub>2</sub> BE shows a bipolar forming-free switching behavior; positive bias for set and negative one for reset. (b) No difference was observed under reverse initial voltage sweep. (c) Formation of a 1.5-nm-thick SiO<sub>2</sub> layer on NiSi<sub>2</sub> BE was confirmed by TEM image.

Fig. 3 (a) I-V curve of the device with TiN BE indicates the need of forming processes for resistive switching. TEM image reveals a formation of  $TiO_2$  layer, which has high dielectric constant.

Fig.4 Owing to buffer CeO<sub>x</sub> layer, high electric field induces breakdown to the thin SiO<sub>2</sub> layer during set process (+V). The layer also prompt the anodic reoxidation by oxygen ion diffusion to the breakdown spot with reverse voltage application (-V) from CeO<sub>x</sub> layer. The resistance of HRS is determined by the excellent insulating properties of SiO<sub>2</sub>.

Fig.5 CeO<sub>x</sub> thickness dependent switching behaviors with NiSi<sub>2</sub> BE. Smaller V<sub>set</sub> and V<sub>reset</sub> value were observed with thinner CeO<sub>x</sub> thickness.

$$V_{app} = E_{\rm SiO_2} I_{\rm SiO_2} + E_{\rm CeO_x} I_{\rm CeO_x}$$

(2)

$$V_{set} = E_{\mathrm{SiO}_2}^{BD} \left( t_{\mathrm{SiO}_2} + \frac{k_{\mathrm{SiO}_2}}{k_{\mathrm{CeO}_x}} t_{\mathrm{CeO}_x} \right) \quad (3)$$

Fig.6 The CeO<sub>x</sub> thickness dependency of  $V_{set}$  can be well explained by the electrostatics to induce hard breakdown field to thin SiO<sub>2</sub>.

Fig.7 Cyclic switching endurance shows a stable HRS/LRS ratio of  $10^3$  with small spread for both HRS and LRS.

Fig.8 Resistive switching rate with different pulse width confirms no degradation in HRS/LRS at least down to 200nsec.

|                                                                                                                                                    | buffer layer:                                                                                                                                                                        | Example: CeO <sub>x</sub> , TiO <sub>2</sub> , YSZ, STO |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

|                                                                                                                                                    | $ \begin{cases} > \text{ High } k \text{ value} \\ > \text{ High } E_{BD} \end{cases}  \text{ induce BD in switching layer} \\ > \text{ High oxygen ion conductivity} \end{cases} $  |                                                         |  |

|                                                                                                                                                    | $ \begin{array}{l} \rightarrow \text{Easy for Re-oxidation process} \\ \succ \text{Small } E_g \\ \rightarrow \text{ large current after breakdown of switching layer} \end{array} $ |                                                         |  |

|                                                                                                                                                    | Switching laye                                                                                                                                                                       | Example: SiO <sub>2</sub> on Silicide BE                |  |

| $\begin{cases} \succ \text{ Low } k \text{ value} \\ \succ \text{ Wide } E_g \\ \succ \text{ Can be formed by anodic oxidation at BE} \end{cases}$ |                                                                                                                                                                                      |                                                         |  |

Fig.9. Summary of material equirements for buffer high-k, switching layers. Several possible candidates are also listed as examples.