# Effects of High-Temperature Annealing on Properties of Al<sub>2</sub>O<sub>3</sub>/InAlN Interface Formed by Atomic Layer Deposition

Takuma Nakano, Masahito Chiba, and Masamichi Akazawa\*

Research Center for Integrated Quantum Electronics, Hokkaido University, Sapporo 060-8628, Japan \*Phone: +81-11-706-6875 E-mail: akazawa@rciqe.hokudai.ac.jp

### Abstract

Effects of high-temperature annealing on the properties of the Al<sub>2</sub>O<sub>3</sub>/InAlN interface formed by atomic layer deposition (ALD) are investigated. Post deposition annealing at 850 °C deteriorated the electrical property of the InAlN metal-oxide-semiconductor diode with an 18 nm-thick ALD-Al<sub>2</sub>O<sub>3</sub> layer. However, the Al<sub>2</sub>O<sub>3</sub>/ InAlN interface property was improved by two-step ALD interrupted by annealing at 850 °C right after the initial 2 nm-thick Al<sub>2</sub>O<sub>3</sub> layer formation.

### **1. Introduction**

InAlN lattice matched to GaN is one of the candidate barrier materials for high frequency and high power GaN-based high-mobility-electron transistors (HEMTs) [1]. For a high performance of HEMTs, use of a gate insulator to suppress the leakage current has been proposed [2]. Recently, a marked progress of the cut-off frequency of InAlN/GaN HEMTs has been achieved by inserting a gate insulator [3]. However, a control method of the insulator/InAlN interfaces, particularly annealing to improve the interface properties, has not been matured. Although Al<sub>2</sub>O<sub>3</sub> by atomic layer deposition (ALD) is promising for a gate insulator, it should be taken into account that annealing at a high temperature causes crystallization of Al<sub>2</sub>O<sub>3</sub> to deteriorate insulating properties [4]. Here, actual effects of high temperature annealing on the ALD-Al<sub>2</sub>O<sub>3</sub>/InAlN interface properties are investigated to find an appropriate method.

### 2. Sample preparation

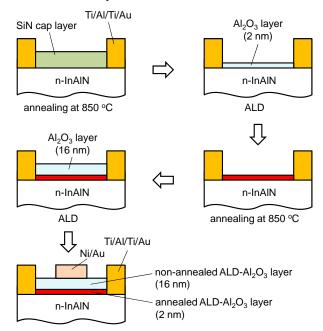

Here, a fabrication process for a metal-oxide- semiconductor (MOS) diode illustrated in Fig. 1 is adopted in order to separate the annealing effects on the Al2O3/InAlN interface from those on the Al<sub>2</sub>O<sub>3</sub> bulk. The process sequence is as follows. Tested MOS diodes consisted of the ALD-Al<sub>2</sub>O<sub>3</sub> (18 nm)/n-In<sub>0.17</sub>Al<sub>0.83</sub>N (160 nm,  $n = 2 \times 10^{18} \text{ cm}^{-3}$ ) structures. An annular Ti/Al/Ti/Au (20 nm/50 nm/20 nm/100 nm) ohmic contact was formed and annealed at 850 °C for 1 min using a 20 nm-thick SiN<sub>x</sub> cap layer for surface protection. After removing the SiN<sub>x</sub> cap layer using buffered hydrofluoric acid, a 2 nm-thick ALD-Al<sub>2</sub>O<sub>3</sub> layer was formed at 350°C using H<sub>2</sub>O and trimethylaluminum. Subsequently, the sample was annealed at 850°C for 1 min. Then, the outer Al<sub>2</sub>O<sub>3</sub> layer of 16 nm thickness was deposited by ALD again. Finally, a circular Ni/Au (20 nm/50 nm) electrode was formed on the Al<sub>2</sub>O<sub>3</sub> layer at the center of the annular

ohmic electrode. For comparison, MOS diodes with an  $Al_2O_3$  layer of 18 nm thickness by conventional one-step ALD without interruption were also prepared. Post deposition annealing for these was performed prior to Ni/Au electrode formation. For XPS investigation, a 15 nm-thick InAlN layer on the GaN buffer layer was used.

## 3. Results and discussion

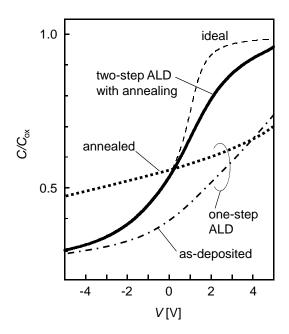

The 1 MHz capacitance-voltage (C-V) curves measured before and after post deposition annealing at 850°C for 1 min are compared in Fig. 2 for the MOS diodes fabricated by one-step ALD without interruption. After annealing the C-V characteristic was markedly deteriorated compared with that of the as-deposited sample, which indicated that post deposition annealing at a high temperature was not suitable for this structure.

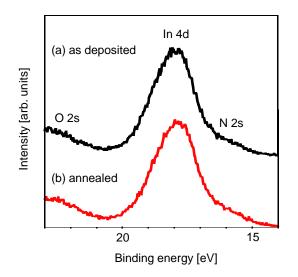

In order to investigate the influence of annealing on the interface, X-ray photoelectron spectroscopy (XPS) investigation was performed on the sample with 2 nm-thick  $Al_2O_3$  layer on InAlN. The In 4d spectra measured before and after annealing at 850 °C for 1 min are shown in Fig. 3. There was no marked evidence of intermixing at the interface. This result indicates that high-temperature annealing does not necessarily deteriorate the interface structure.

Fig 1 Fabrication process with two-step ALD.

Fig 2 C-V curves. The solid line indicates the 1 MHz curve for the MOS diode through two-step ALD combined with annealing, while the one-dot-chain and dotted lines are respectively those for the one-step ALD samples before and after annealing at 850 °C. The broken line shows the ideal curve.

Fig 3 XPS In 4d spectra with N 2s and O 2s spectra of the  $Al_2O_3(2 \text{ nm})/InAlN$  sample measured (a) before and (b) after annealing at 850 °C for 1 min.

There is the possibility that the deterioration of the electrical properties of the MOS diode was owing to the bulk of the  $Al_2O_3$  layer. Therefore, we tried to apply the proposed interface formation method. Actually, the C-V curve measured for the two-step ALD sample showed a much improved characteristic with a large capacitance change, as shown in Fig. 2 where the ideal curve overlaps the measured one in the depletion region. This result indicates that the reduction of the interface states while maintaining the high dielectric quality was achieved by adopting

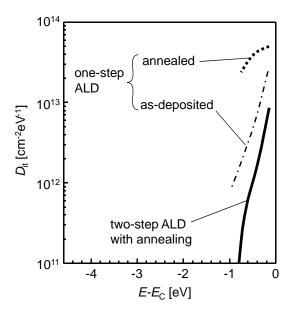

Fig 4  $D_{it}$  distributions evaluated from C-V curves.

the two-step ALD method.

The  $D_{it}$  distribution was evaluated for all samples by the high-frequency method, as shown in Fig. 4. The  $D_{it}$  evaluation is limited to near the conduction band because the time constant of the interface states becomes much longer than the practical measurement time deep inside the band gap. Although high-temperature annealing led to an increase in  $D_{it}$  for the sample through one-step ALD,  $D_{it}$  was markedly reduced for the two-step ALD sample. Therefore, the interface properties are improved by high-temperature annealing when the deterioration of the Al<sub>2</sub>O<sub>3</sub> insulator bulk properties, probably owing to crystallization [4], is suppressed.

## 4. Conclusions

Although the electrical properties of the MOS diode with the single  $ALD-Al_2O_3$  layer was deteriorated, XPS results showed that annealing at 850 °C was not harmful for the  $ALD-Al_2O_3/InAlN$  interface. Thus, the deterioration of the diode properties was possibly caused by the annealed  $Al_2O_3$  insulator bulk. Actually, an improvement of the  $Al_2O_3/InAlN$  interface properties was achieved by minimizing annealed layer thickness in two-step ALD.

#### Acknowledgements

This work was supported by JSPS KAKENHI Grant Number 24560022. The authors are thankful to Professors T. Hashizume and E. Sano for their fruitful discussions.

## References

- [1] J. Kuzmík, IEEE Electron. Device Lett. 22 (2001) 510.

- [2] G. Pozzovivo et al., Appl. Phys. Lett. 91 (2007) 043509.

- [3] Y. Yue et al., presented at IWN2012, Int. Workshop on Nitride Semiconductors 2012, Sapporo, Japan, Oct. 14-19, 2012.

- [4] Y. Hori, C. Mizue, and T. Hashizume, Jpn. J. Appl. Phys. 49 (2010) 080201.