# CAAC-OS-based Nonvolatile Programmable Analog Device: Voltage Controlled Oscillator Realizing Instant Frequency Switching

Yuki Okamoto<sup>1</sup>, Takashi Nakagawa<sup>1</sup>, Takeshi Aoki<sup>1</sup>, Munehiro Kozuma<sup>1</sup>, Yoshiyuki Kurokawa<sup>1</sup>, Takayuki Ikeda<sup>1</sup>, Naoto Yamade<sup>1</sup>, Yutaka Okazaki<sup>1</sup>, Hidekazu Miyairi<sup>1</sup>, Masahiro Fujita<sup>2</sup>, and Shunpei Yamazaki<sup>1</sup>

<sup>1</sup> Semiconductor Energy Laboratory Co., Ltd. 398 Hase, Atsugi-shi, Kanagawa, 243-0036, Japan Phone: +81-46-248-1131, Fax: +81-46-270-3751, E-mail: yo1273@sel.co.jp

<sup>2</sup> VLSI Design and Education Center (VDEC), The University of Tokyo 2-11-16 Yayoi, Bunkyo-ku, Tokyo, 113-0032, Japan

#### **Abstract**

A VCO using programmable analog memory (PAM) as a voltage-controlled element is developed as a programmable analog device including a c-axis aligned crystalline In-Ga-Zn oxide FET. The oscillation frequency of the VCO is controlled by analog voltage data (AVD) stored at the PAM. The frequency can change over six orders of magnitude with a driving voltage of 1.5 V and AVD ranging from 0.7 to 2.5 V. This is realized by switching among PAMs that keep their values with infrequent AVD refresh. A low-power PLL using the VCO is also proposed.

#### 1. Introduction

A c-axis aligned crystalline In-Ga-Zn oxide (CAAC-IGZO), a crystalline oxide semiconductor (OS), can be used to achieve a FET exhibiting ultra-low off-state current [1]. LSI [2]–[7] as well as display [8] applications utilizing the CAAC-IGZO FET have been developed. They include field-programmable gate arrays (FPGAs), having CAAC-IGZO FET-based nonvolatile configuration memory [5]–[7], that employ a multi-context architecture to realize instant configuration switching and require extremely low power for data retention.

The CAAC-IGZO FET-based configuration memory in these FPGAs works as memory holding binary digital data; it also has the potential to work as nonvolatile programmable analog memory (PAM) that can keep the values.

As an example application of a programmable analog device, this paper reports on a VCO using nonvolatile PAM with a CAAC-IGZO FET as a voltage-controlled element (VCE). The VCO outputs a signal with intended oscillation frequency in accordance with analog voltage data (AVD) stored at PAM and is capable of switching frequencies at high speed and obtaining stable oscillation in a short time after power-on.

## 2. Design and Fabrication

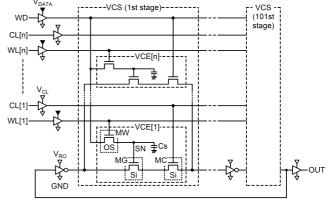

Fig. 1 is a circuit diagram of the fabricated VCO. The VCO is a ring oscillator composed of 101-stage inverters and voltage-controlled switches (VCS) between the inverters. Each VCS consists of multiple VCEs (VCE[i]). VCE[i] stores intended AVD ( $V_{\rm DATA}$ ) at a node SN, and the channel resistance of a transistor MG is controlled based on the AVD when the AVD is well controlled by a circuit for setting voltage. In other words, the VCS resistance is based on the AVD programmed in a selected VCE to enable control of the VCO oscillation frequency. With the use of a

CAAC-IGZO FET as a transistor MW, the node SN is regarded as floating when the transistor MW is off; thus, the AVD can be kept for a long time.

Multiple VCEs have the following advantage: by programming different AVD in the VCEs and changing selection of VCEs, the oscillation frequency of the VCO can be switched immediately in accordance with AVD programmed in the selected VCE.

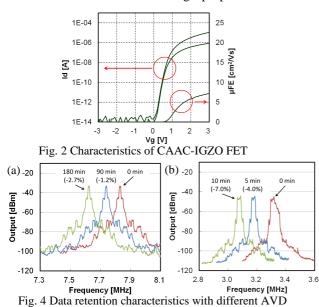

The VCO has been fabricated with a hybrid process involving a 1.0  $\mu$ m CAAC-IGZO FET and a 0.5  $\mu$ m CMOS FET [2]–[7]. Fig. 2 shows the static characteristics of a CAAC-IGZO FET. The off-state current of this FET is extremely low; an off-state current of a CAAC-IGZO FET with a channel length of 3  $\mu$ m is approximately 5E–23 A/ $\mu$ m at 85 °C [9].

## 3. Measurements and Results

3-1. Oscillation Frequency vs.  $V_{DATA}$

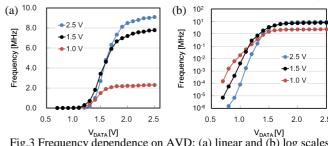

Fig. 3 shows the relationship between oscillation frequency and AVD programmed in each VCE; the relationship is measured on a test element group with a VCS having four VCEs. The driving voltage  $V_{\rm RO}$  of the inverter is 1.0, 1.5, or 2.5 V. The driving voltage  $V_{\rm CL}$  of a circuit selecting the gate of the transistor MW is 2.5 V. The backgate voltage  $V_{\rm BG}$  of the transistor MW is –9.0 V. The write time is 500  $\mu$ s.

The results of selecting only VCE[1] show the VCO oscillation frequency depends on the level of  $V_{\rm DATA}$ . For example, at  $V_{\rm RO}$  of 1.5 V, the oscillation frequencies are 7.20 Hz and 7.83 MHz with  $V_{\rm DATA}$  of 0.7 V and 2.5 V, respectively. In other words, the VCO changes the oscillation frequency over six orders of magnitude with  $V_{\rm RO}$  ranging from 0.7 to 2.5 V. Note that inverter delay may be dominant in a region with high  $V_{\rm DATA}$ ; therefore, the oscillation frequency does not depend significantly on  $V_{\rm DATA}$ . On the other hand, in a region with low  $V_{\rm DATA}$ , specifically 1.3 V or lower, oscillation frequency depends strongly on  $V_{\rm DATA}$ .

With regard to oscillation frequency dependence on  $V_{\rm RO}$ , with  $V_{\rm RO}$  of 1.0 and 2.5 V, the highest oscillation frequencies are 2.30 and 9.09 MHz, respectively, and the maximum gradients of the log-scale oscillation frequency with respect to  $V_{\rm DATA}$  are 0.47 and 1.08 decades per 100 mV, respectively. Accordingly,  $V_{\rm RO}$  may be changed to meet intended applications of the VCO; for example, a high driving voltage is used to obtain a wide frequency range, and a low driving voltage is used to control the frequency at short intervals.

# 3-2. Oscillation Frequency Retention

Fig. 4 shows frequency retention characteristics, i.e., oscillation frequency spectra of the VCO and the change with time when  $V_{\rm DATA}$  is 1.5 or 2.5 V. In the initial state, power consumption of the VCO with  $V_{\rm DATA}$  of 2.5 and 1.5 V is 795 and 336  $\mu$ W, respectively, and figures of merit [10] are estimated at –127.7 and –134.3 dBc/Hz.

With  $V_{\rm DATA}$  of 2.5 V, the central oscillation frequency is decreased by 1.2% in 90 min. In contrast, with  $V_{\rm DATA}$  of 1.5 V, the central oscillation frequency is attenuated by 4.0% in 5 min. This probably occurs because the rate of increase of the oscillation frequency to  $V_{\rm DATA}$  is higher at  $V_{\rm DATA}$  of approximately 1.5 V than when it is approximately 2.5 V, and thus a small fluctuation of AVD programmed in a VCE greatly influences the oscillation frequency.

The results demonstrate that the oscillation frequency of the VCO can be kept constant by re-programming AVD with refresh at very long intervals. Depending on the AVD, changing the interval between refreshes is effective.

#### 3-3. Frequency Switching

Owing to nonvolatile analog memory, the VCO is capable of maintaining the oscillation frequency after power-off and subsequent reboot. Fig. 5 shows the waveform of an output OUT of the VCO when the VCO in the off state is rebooted with  $V_{\rm DATA}$  of 2.5 V. Fig. 5 demonstrates that when power supply is restarted at time ( $\alpha$  + 1.0)  $\mu$ s, oscillation is restarted in less than 30 ns.

Furthermore, programming different AVD in VCEs of the VCO enables instant switching of the oscillation frequency. Fig. 6 shows the oscillation frequency is switched by changing selected VCE between VCE[1] and VCE[2] when  $V_{\rm RO}$  is 1.5 V. It is clear from Fig. 6 that the frequency is switched in less than 100 ns.

#### 4. PLL Application

In a general PLL, circuits other than a VCO are forced to operate even after oscillation of the VCO is stabilized. These circuits account for a large proportion of the total

power consumption. It has been reported that in a PLL operating at approximately 20 GHz and 1.5 V, circuits other than the VCO account for 60% of the total current consumption [11].

In contrast, in a PLL including the proposed VCO, circuits excluding the VCO can be powered off in periods other than an infrequent refresh period required to maintain the oscillation frequency; thus, power consumption can be drastically reduced. Further, in rebooting the PLL, AVD corresponding to the previous oscillation frequency can be held, which should result in high-speed rebooting.

# References

- [1] S. Yamazaki et al., Jpn. J. Appl. Phys., 53 (2014) 04ED18-1.

- [2] T. Ohmaru et al., Ext. Abst. SSDM (2012) 1144.

- [3] H. Inoue et al., IEEE J. Solid-State Circuits, 47 (2012) 2258.

- [4] T. Aoki et al., Proc. VLSI Technology Symp. (2011) 174.

- [5] M. Kozuma et al., Jpn. J. Appl. Phys., 53 (2014) 14EE12-1.

- [6] T. Aoki et al., ISSCC Dig. Tech. Papers, 30.9 (2014) 502.

- [7] Y. Okamoto et al., IEEE Trans. VLSI Syst., to be published.

- [8] S. Yamazaki et al., Proc. SID'12 Dig. (2012) 183.

- [9] Y. Sekine et al., ECS Trans. 37 (2011) 77.

- [10] X. Gao et al., TCAS-II, 56 (2009) 117.

[11] Y. Ding et al., IEEE J. Solid-State Circuits, 42 (2007) 1240.

Fig. 1 Circuit diagram of proposed VCO including CAAC-IGZO FET with channel width  $W = 4 \mu m$  and Si FET with  $W = 16 \mu m$

$(V_{RO} = 1.5 \text{ V});$  (a)  $V_{DATA} = 2.5 \text{ V},$  (b)  $V_{DATA} = 1.5 \text{ V}$

Fig. 5 Output waveform from power-off to reboot;  $\alpha = 15$  min

Fig. 6 Output waveform in switching selected VCE;  $V_{RO} = 1.5 \text{ V}$