# Combined PEALD gate-dielectric and *in-situ* SiN cap-layer for reduced $V_{th}$ shift and $R_{DS-ON}$ dispersion of AlGaN/GaN HEMTs on 200 mm Si wafer

N. Ronchi<sup>1</sup>, B. De Jaeger<sup>1</sup>, M. Van Hove<sup>1</sup>, R. Roelofs<sup>2</sup>, T.-L. Wu<sup>1,3</sup>, J. Hu<sup>1,3</sup>, X. Kang<sup>1</sup> and S. Decoutere<sup>1</sup>

<sup>1</sup> imec - Kapeldreef 75, B-3001 Leuven, Belgium

<sup>2</sup> ASM - Kapeldreef 75, B-3001 Leuven, Belgium

<sup>3</sup> KU Leuven, Dep. of Electrical Engineering, Kasteelpark Arenberg 10, B-3001, Leuven, Belgium. Phone: +32 16 28 8557, e-mail: nicolo.ronchi@imec.be

#### **Abstract**

The present work focuses on the gate dielectric and MOCVD (MetalOrganic Chemical Vapour Deposition) capping layer of AlGaN/GaN transistors grown on 200 mm Si wafers. Firstly, it will be shown how a SiN gate dielectric grown by means of PEALD (Plasma Enhanced Atomic Layer Deposition) reduces the threshold voltage (V<sub>th</sub>) shift induced by negative gate bias and the gate leakage with respect to a SiN gate dielectric grown by RTCVD (Rapid Thermal Chemical Vapor Deposition). Secondly, the dynamic RDS-ON dispersion of two samples with same gate dielectric (PEALD-SiN) but different MOCVD capping layer is compared. Results will show that the traps causing the RDS-ON dispersion are mainly located at the surface and that their amount can drastically be reduced by using in-situ MOCVD SiN as capping layer.

## 1. Introduction

The use of GaN as substitute of Si for power-switching applications has raised several challenges to make this new technology competitive in terms of performances and costs. AlGaN/GaN HEMTs (High Electron Mobility Transistors) realized on 200 mm Si wafers with Au-free contacts (compatible with standard CMOS technology) seems today an attractive path to follow to reach a cost-effective high-performant device [1].

One of the main issues is the choice of the surface termination in the gate region to reduce both gate leakage and density of trap states at the semiconductor/passivation interface. The MISHEMT structure (Metal Insulator Semiconductor HEMT) is the best solution to suppress the gate leakage in both forward and reverse bias in comparison with a Schottky gate contact. In this paper we will compare two different techniques for the deposition of SiN as gate dielectric. One of the possibilities is the deposition by means of RTCVD. The characteristic of this technique is that the wafer is processed at high temperature for a short time [2]. The other possibility which will be analyzed is the deposition by means of PEALD. This process allows lower deposition temperature during the process, with lower density of interface states [3].

Several publications show how the surface treatment in the access regions improves the frequency response of the device (low dynamic  $R_{DS\text{-}ON}$  dispersion) [4]. We will demonstrate a reduction of the dynamic  $R_{DS\text{-}ON}$  dispersion

by using an *in-situ* MOCVD SiN capping layer in the access region in a device with a PEALD SiN gate dielectric.

#### 2. Experimental Details and Results

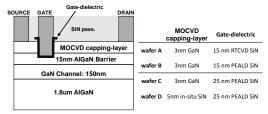

The first phase of the work focused on the study of the gate dielectric. For this purpose two wafers with identical epitaxial layers but different gate dielectrics were processed. The samples were grown on 200 mm <111> Si wafers. The top layers of the epi-stack consist of a 1.8 µm AlGaN buffer layer (8% Al content), a 150 nm GaN channel, a 15 nm Al<sub>0.25</sub>Ga<sub>0.75</sub>N barrier and a 3 nm GaN-cap layer. The surface was passivated with SiN deposited by means of RTCVD. Then the gate region was etched to leave 3.7 nm AlGaN and form the gate recess. For the gate dielectric, a 15 nm layer of SiN was deposited by means of RTCVD at 700°C on the first wafer. On the second wafer 15 nm SiN was deposited by means of PEALD in a "ASM Eagle® 12" deposition tool. Au-free metal contacts were used. A schematic cross-section of the device is reported in Fig.1 (wafers "A" and "B"). The devices measured had gate-drain distance  $L_{GD} = 5 \mu m$ , gate width  $W_{GD} = 100$  or 200  $\mu m$ , gate length  $L_G = 1.5 \mu m$ , gate-source distance  $L_{GS} = 0.75$

Fig. 1 Schematic cross-section of the samples used in this work. The table shows the process splits: wafers "A" and "B" were used for the  $1^{st}$  experiment ( $V_{th}$  shift); wafers "C" and "D" were used for the  $2^{nd}$  experiment ( $R_{DS-ON}$  dispersion).

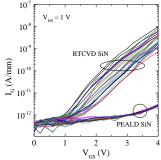

Fig. 2 Forward gate leakage of samples with RTCVD SiN as gate dielectric (wafer A) and samples with PEALD SiN as gate dielectric (wafer B).

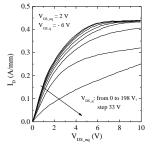

μm, a gate field-plate and two levels of source field-plate (extending respectively 1 µm, 2 µm and 3 µm beyond the drain edge of the gate). On these devices leakage measurements and pulse I<sub>D</sub>-V<sub>GS</sub> measurements were performed. The gate leakage in forward bias is reported in Fig. 2. Devices with PEALD SiN gate dielectric have lower gate leakage compared to the devices with RTCVD SiN gate dielectric. Pulsed I<sub>DS</sub>-V<sub>GS</sub> measurements were performed by pulsing the device from a quiescent state  $(V_{GS q}, V_{DS q})$  to a non-quiescent state ( $V_{GS\_nq}$ ,  $V_{DS\_nq}$ ). The frequency and the duty-cycle of the signal were f = 10 kHz and  $\delta = 10\%$ , respectively. The test equipment was an AURIGA AU4850. The same bias conditions were used to test both the RTCVD and the PEALD gate-dielectric samples. Example  $I_D\text{-}V_{GS}$  are reported in Fig. 3. The  $V_{\text{th}}$  is calculated as the intercept on the x axis of the linear interpolation of the  $I_D$ - $V_{GS}$  at maximum  $g_m$ . The  $V_{th}$  shifts ( $\Delta V_{th}$ ) are summarized in Fig. 4. The samples with PEALD SiN have lower V<sub>th</sub> shifts than the ones with RTCVD SiN.

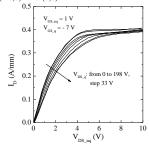

Once the process for the gate dielectric was established, our attention moved to improve the dynamic R<sub>DS-ON</sub> by improving the surface quality on the access region of the device. With this purpose in mind two other wafers were processed with the same epi-stack shown in Fig. 1. A split was introduced on the last layer: in one of the two wafers the 3 nm GaN-cap layer was substituted by a 5 nm in-situ SiN-cap layer (wafers "C" and "D" in Fig. 1). Both wafers were then passivated by RTCVD SiN as ex-situ passivation layer. The gate dielectric was 25 nm PEALD SiN; note that with this thicker gate dielectric a smaller  $\Delta V_{TH}$  and a lower gate leakage was found compared to the wafer with 15 nm PEALD SiN reported above. Pulsed I<sub>D</sub>-V<sub>DS</sub> measurements were performed with the same switching conditions as used for the  $I_D$ - $V_{GS}$ . The  $V_{DS\ q}$  was swept from 0 V to 198 V in 33 V steps, while the V<sub>GS\_q</sub> was kept constant. A comparison between a device with GaN-cap layer and one with in-situ SiN-cap layer is reported in Fig. 5. The I<sub>D</sub> of the device with GaN-cap layer drops; whereas the I<sub>D</sub> of the device with in-situ SiN-cap layer remains high up to pulsing from 198 V quiescent bias condition. To quantitatively evaluate the current collapse the dynamic R<sub>DS-ON</sub> was calculated from the slope of the I<sub>D</sub>-V<sub>DS</sub> in the linear region. Results are reported in Fig. 6. The average increase of the R<sub>DS-ON</sub> for the samples with *in-situ* SiN is 50%, moreover devices have a good uniformity over the wafer. On the other hand samples with GaN cap show an increase of R<sub>DS-ON</sub> that varies from 50% in the best case up to 10 times the initial value in the worst case, with low uniformity over the wafer. We conclude that the *in-situ* SiN-cap gives a better and more uniform passivation of the surface trap states in the gate-to-drain access region.

## 3. Conclusions

In this work gate leakage and dynamic *I-V* measurements were used to compare different gate dielectrics and different MOCVD cap-layers. It has been shown that PEALD SiN as gate dielectric gives better performance in

terms of leakage and threshold voltage shift. It has also been shown that the *in-situ* deposited SiN cap-layer on the access region improves the dynamic response of the device with PEALD SiN gate dielectric.

Fig. 3 Pulsed I<sub>D</sub>-V<sub>GS</sub> characteristics for a device with 15 nm RTCVD SiN gate-dielectric (left, wafer A) and a 15 nm PEALD SiN gate dielectric (right, wafer B).

Fig. 4 Shift of the threshold voltage from the pulsed  $I_D$ - $V_{GS}$  measurements.  $\Delta V_{th}$  is calculated as  $V_{th(-10,0)}$ - $V_{th(0,0)}$

Fig. 5 Pulsed I<sub>D</sub>-V<sub>DS</sub> characteristics at different drain quiescent biases (V<sub>DS\_q</sub>). On the left: wafer C - sample with 25 nm PEALD SiN gate dielectric and GaN cap; on the right: wafer D - sample with 25 nm PEALD SiN gate dielectric and *in-situ* SiN cap.

Fig. 6 Normalized  $R_{DS-ON}$  measured pulsing from  $V_{DS_q} = 198 \text{ V}$  quiescent bias condition.

### References

- [1] B. De Jaeger et al., Proc. of the 2012 24th Int. Symposium on Power Semiconductor Devices and ICs, (2012) 49.

- [2] M.F. Pas et al., Proc. of Advanced Semiconductor Manufacturing Conference and Workshop, (1996) 250.

- [3] D.H. Triyoso et al., Int. Conf. on IC Design & Tech., (2013) 29.

- [4] B.M. Green et al., IEEE Elec. Device Letters, 21 (2000) 268.