# A New Method to Effectively Separate PBTI-induced Shallow and Deep Energy Traps in a 28nm High-k Metal-Gate MOSFET

E. R. Hsieh<sup>1</sup>, P. C. Wu<sup>1</sup>, Steve S. Chung<sup>1</sup>, J. C. Ke<sup>2</sup>, C. W. Yang<sup>2</sup>, and C. T. Tsai<sup>2</sup>

Department of Electronics Engineering, National Chiao Tung University, Taiwan <sup>2</sup>United Microelectronics Corporation (UMC), Taiwan

Abstract- An experimental approach has been developed to separate the shallow and deep energy traps in a 28nm high-k and metal gate (HKMG) nMOSFET with Fluorine co-implant. This was achieved by the concept of thermal Frenkel-Poole emission and direct-tunneling. It was shown that, for a weaker PBTI stress, the shallow energy trap(SET) dominates the device degradation, but for a heavier PBTI stress, the deep energy trap(DET) dominates. Results showed that, although F ions can alleviate both types of traps, compared to DET, SET is difficult to be alleviated efficiently. Moreover, after the HC stress, not only the conventional hot electrons contribute to the generation of deep energy trap, but also the cold electrons contribute to shallow energy traps. These results provide us a new thinking about the significance of the mechanism of shallow trap in PBTI stressed HKMG CMOS devices.

#### 1. Introduction

With the further device scaling, the high-k metal gate (HKMG) have been launched beyond 28nm to replace the conventional SiON gate dielectric CMOS and to improve the driving current by aggressive reduction of EOT. However, it aroused more reliability issues by the using of new HK materials, such as HfO<sub>2</sub> [1-2]. Among those reliability issues, Bias temperature instability (BTI) is the dominant one to degrade the performance and lifetime of CMOS devices [3-4]. Most reported results claimed that the deep energy traps near the Fermi level are the main origin of the device degradation after the BTI stress [5-7]. However, rare has been discussed on the effect of shallow energy traps. In this paper, it raised our interest to develop an experimental method to separate the shallow energy traps (SET) and deep energy traps (DEP), such that different degradation mechanisms of PBTI stress can be identified. Moreover, this approach is further extended to the hot-carrier (HC) stress on HK nMOSFET, and the results will provide us better understanding on the reliabilities of HK CMOS devices.

## 2. Device Preparation

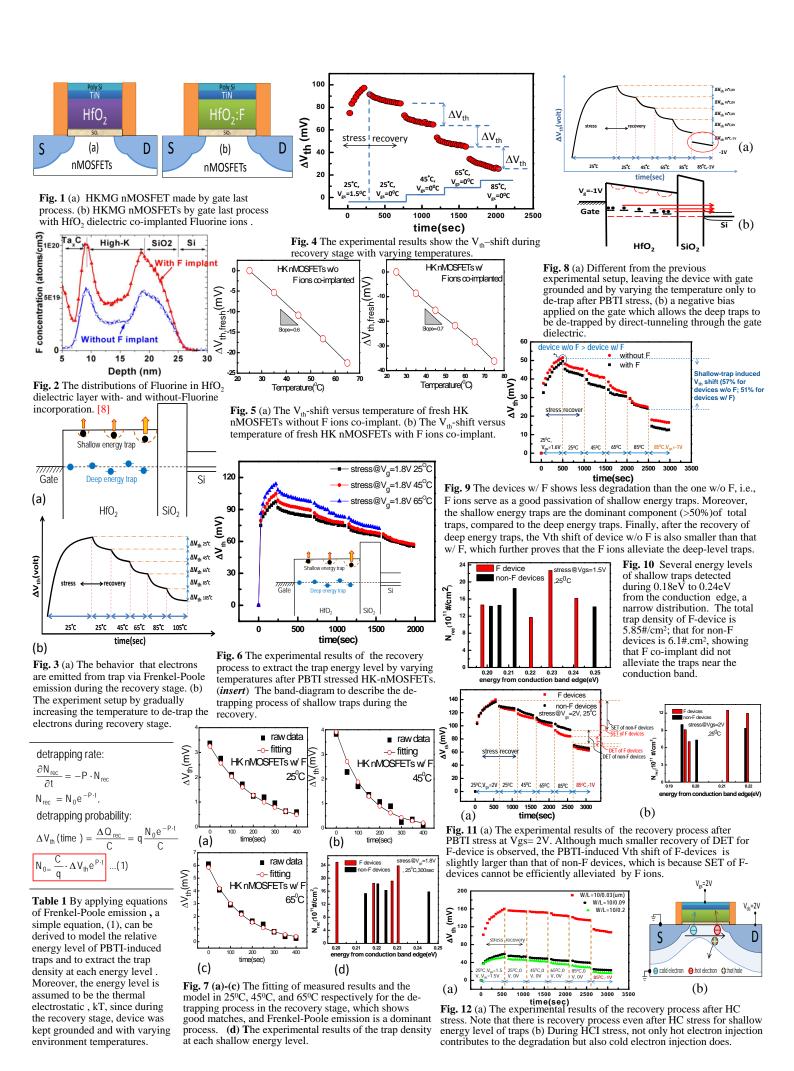

To improve the reliability, the standard CMOS process with fluorine(F) co-implanted in HK dielectric was used to passivate the interface traps (Fig. 1a), named as **F-devices.** The calculated EOT of stacked dielectrics is 10.5Å. CMOS devices with W/L= 10um/30nm were used in this work, and the control device without F co-implanted was served as a control sample, named as **non-F devices**, (Fig. 1b). Fig. 2 represents the distribution of F ions in HK and interfacial-layer(IL) [8]. Note that the F ions were accumulated at the interface, which are mainly used to passivate the interface traps.

#### 3. Results and Discussion

## A. Methodology in the Extraction of Shallow and Deep Energy Traps After the stress

Fig. 3 shows the design of the experiment to describe how to extract the shallow energy trap (SET) from PBTI-induced  $V_{th}$ -shift. Since the shallow trap is close to the conduction-band edge, i.e., those type of traps could be emitted easily by raising the environment temperature through the Frenkel-Poole(F-P) emission, the experiment is designed to gradually emit SET by ramping the temperature step by step during the recovery stage after the PBTI stress. Then, by applying the F-P equations, a simple formula can be derived, Table 1:

$$N_o = C\Delta V_{th}(t) e^{P(i)t}/q$$

(1)

where t is the recovery time, a function of temperature, and  $N_{\rm o}$  is trap density for each shallow energy level; P is the de-trapping probability representing the emission rate of F-P process, which can be fitted from

the experimental data. By utilizing this method, the results are exhibited in Fig. 4. After the PBTI stress, the  $V_{th}$  is ramped up to a higher value, i.e., 0.09V, then, during the following recovery process, electrons can be pulled out from the trap by the changes of temperature. In order to extract the deep level traps, it should be extracted from the fresh devices before any stress, Fig. 5. Also, Fig. 6 shows the comparison of the decreasing rate of  $V_{th}$  with different temperatures. By fitting the raw data in Fig. 6 with Eq. (1), the trap density of each shallow energy level can be determined, Fig. 7. Furthermore, to separate the SET and deep energy level (DET), in the last stage of the recovery process, a negative bias is applied to de-trap those DET's which are located close to the Fermi-level by the direct-tunneling. From the  $V_{th}$  shift after this step, the trap-density of DET can be determined as well, Fig. 8.

## B. The Impact of Shallow-energy-trap After the PBTI stress

Figure 9 shows the results of PBTI test at  $V_{gs} = 1.5V$  and the recovery process. It was found that F-device shows smaller deterioration than non-F one, which means F ions does passivate traps effectively. But what kind of trap is it? After SET recovery stage, F-devices show less amount recovered to non-F devices. On the other hand, during the final DET recovery stage, DET recovery of F-devices is larger than that of non-F devices, and thus F ions passivate mainly SET rather than DET. But, it is worthy to note that the component of SET is larger than that of DET, more than 50% in both device splits. Therefore, the V<sub>th</sub>-shift of F-devices shows better improvement. Fig. 10 shows a narrow distribution of SET near the conduction band edge from 0.18eV to 0.24eV extracted from Fig. 9. Since SET possesses larger than a half of total traps, the distribution of PBTI-induced traps is reasonably assumed as the peaks appears at the top and bottom; the valley happens in the middle along with the energy in the band-diagram. Fig. 11 shows the results of PBTI test at  $V_{gs}=2V$ . Although F-devices show smaller DET, the PBTI-induced V<sub>th</sub> shift of F-devices is still slightly higher than non-F devices, which is because SET of F-devices cannot be alleviated efficiently and degrades  $V_{th}$  in heavily stressed PBTI. Furthermore, in comparison to a weaker stress in Fig. 9, Fig. 12(a) shows the stress-recovery results under HC stress. It was found that, after HC, Vth of both devices recovers depending on the temperature, which is due to the cold electron injection from the source of channel into the SET position, Fig. 12(b). In short, for a weaker PBTI stress, the shallow energy trap dominates the device degradation, Fig. 9, but for a heavier PBTI stress, Fig. 11, the deep energy trap dominates.

In conclusion, a novel measurement technique has been developed to extract the shallow energy trap (SET) which can be separated from the deep energy trap (DET) after the PBTI stress. It was demonstrated on F-passivated devices. Results show that F can passivate DET efficiently, but not SET, i.e., the  $V_{th}$ -shift of F-passivation shows benefits at low  $V_{gs}$  (=1.5V) PBTI stress but ineffective at high  $V_{gs}$ (2V). It reveals that SET played an important role when BTI reliability is taken into account in HK CMOS devices.

Acknowledgments This work was support in part by the *National Science Council (NSC)*, *Taiwan*, under contract *NSC100-2221-E009-016-MY3*, and *NCTU-UCB 1-RiCE* program, under *MOST-103-2911-1-009-302*.

**References:** [1] S. Migita et al., *VLSI Tech.*, p. 152 (2008). [2] W. C. Wu et al., *IEDM*, p. 405 (2008). [3] K. Joshi et al, *IRPS* p.5A.3.1 (2012). [4] K. Joshi et al., *IRPS*, 4c.2.1 (2013). [5] T. Grasser et al., *IRPS*, p. 33 (2009). [6] S. Markov et al., *IEEE TED*, vol. 34, p. 689 (2013). [7] E. Simoen et al., *ESC*, vol. 39, p. 3 (2011) [8] H.-H. Tseng, et al., *IEDM*, p. 696 (2005).