## Stress Distribution Pattern in Cross-Sectional 3D-LSI Examined by µ-XRD

M. Murugesan, J.C. Bea, T. Fukushima, K.W. Lee, and M. Koyanagi

Global Integration Initiative (GINTI), NICHe, Tohoku University, 6-6-10 Aza-Aoba, Aramaki, Aoba-ku, Sendai 980-8579, Japan. Phone: + 81-22-795-4119, FAX: +81-22-795-4313, E-mail: murugesh@bmi.niche.tohoku.ac.jp

**Abstract:** We have investigated the strained structure in cross-sectional 3D-LSI Si due to the thermo- mechanical stress caused by the Cu-through silicon via (TSVs) in the chip system. It was found that Cu-TSV originated thermo-mechanical stress not only induces strain in the surface Si, but also caused strained Si structures across the thickness of the stacked LSI die/wafer.

## 1. Introduction and Experiment

It has been forecasted that the global mobile data traffic increases year by year exponentially, and the total amount of data exchanged via internet will soon touch few tens of exabytes in the following year. Again the amount of data exchanged through hand-held electronic gadgets outweighs the conventional data-transfer revealing that a considerable portion of the data-transfer is taking place via the mobile units. Among the data transferred, the video/web data is the mostly exchanged data type using the mobile electronic gadgets. Thus it is natural for one to expect the dramatic increase in the number of functional devices in the integrated circuit system of the future mobile gadgets. However, the main issue is, this has to be achieved in the smaller form factor and at lower cost. The one and only way to achieve it in a smaller from factor is the three dimensional (3D) integration of various LSIs (large scale integrated chip). By and large, in the 3D-LSI process, the conventional two-dimensional system on chip (2D-SoC) is segmented into several functional chips. These segmented chips were finally stacked together vertically and electrically connected across the LSI die/wafer, using through-silicon-via (TSV). 3D-integration technique involves the following several key processes such as (i) die/wafer thinning (ii) formation of metal-interconnects (TSV and  $\mu$ -bump), (iii) die/wafer alignment, and (iv) die/wafer stacking by injecting an organic underfill into the interlayer gap. The injected organic underfill between the stacked LSI dies helps to increase the for mechanical rigidity of the stacked 3D-LSI.

The advantages coming along with the 3D-LIS or 3D-SOC are the shortest possible interconnect with the minimum resistive-capacitive delay, and with significantly small parasitic capacitance. However the major advantages of 3D-LSIs apart from capacitance. However the major advantages of 3D-LSIs apart from the above mentioned are the smaller form-factor with enhanced device performance, which is a must criteria for the future generation integrated circuit design and packaging, and it is not possible to achieve either in 2D or 2.5D. The parasitic capacitance in 3D is about 0.7 pF, where is it is 6 and 20 pF for 2.5D and 2D. At the same time, the die/wafer thinning process either makes the ultra-thin die/wafer to suffer from the residual stress or eliminates the gentering layer for heavy metal atoms coming from BFOL. the gettering layer for heavy metal atoms coming from BEOL process. We have already demonstrated several reliability issues associated with the 3D-LSI process such as the stress-relief method dependent residual stress in 3D-LSIs [1], diffusion of Cu atom (from back metal contamination) into the active Si [1], the large CTE (co-efficient of thermal expansion) difference (between the metal (the CTE of Cu is  $\sim 17 \times 10^{-6}$ /K of the metal-filled TSVs and  $\mu$ -bumps is much greater than the CTE of Si  $\sim 2.6 \times 10^{-6}$ /K) induces severe themo-mechanical stress in the active Si[1-4]. Apart from the above mentioned reliability concerns, one may expect a reliability problem associated with the lattice mis-orientation caused by local deformation of the LSI die in 3D-LSIs. It was also shown by us that the mechanical properties of extremely thin 3D-LSI die/wafer are highly deteriorated, and they affect the DRAM retention characteristics [5].

In this paper, we focus our attention to analyze the locally strained Si structures formed around the Cu-TSVs, since Cu-TSVs and µ-bumps are in-alienable structures of the 3D-LSIs. In general, the thermo-mechanical stress induced in Si around TSV structures in 3D-LSIs are evaluated using micro-Raman spectroscopy (1-4, 6). However, owing to complex nature of strain tensors (exist almost in all directions), it is highly difficult to separate the strain components using micro-Raman technique. On the other, micro-XRD realizes not only the highest possible strain resolution. but also allows one to separate of strain components.(6-8) properties of the stacked die/wafer in 3D-LSIs. In this work, we report the cross-sectional strain distribution for the three-dimensionally stacked dies using 20  $\mu$ m-width Cu TSVs with 40  $\mu$ m TSV depth 20  $\mu$ m TSV spacing.

## 2. Experimental Results

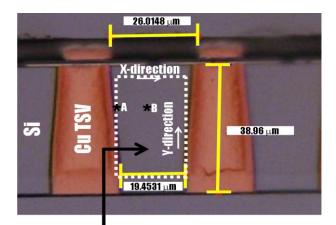

$\mu$ -XRD data was collected using hard-X-rays at BL13XU in Spring8. The incident light energy of 12.4 keV was monochromatized using Si (111) double-crystal monochormator was focused on the sample using zone-plate. The incident beam size was approximately 0.26  $\mu$ m x 0.30  $\mu$ m. The incident x-ray was scanned across the cross-sectional sample as shown in fig. 1. The scan steps are 2  $\mu$ m or 40 pixel in X-direction and 10  $\mu$ m or 200 pixel in Y-direction.

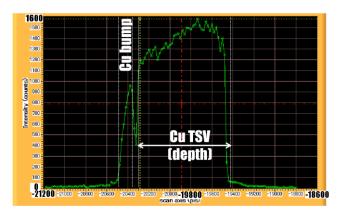

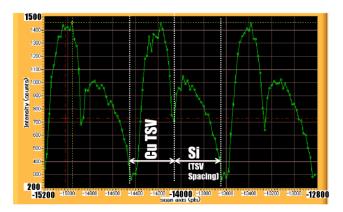

Shown in fig. 1 is the optical image obtained on the cross-sectional 3D-LSI sample stacked using 20  $\mu$ m Cu-TSVs and 15  $\mu$ m  $\mu$ -bump. The rectangular area shown by white dotted lines is the area used for 2D-reciprocal lattice image mapping (RLM) analysis Before carrying out the RLM analysis, the exact positions of the Cu-TSvs and micro-bumps were confirmed by the Cu-X-ray fluorescence spectra. Shown in fig. 2 and 3 are respectively the Cu-XRF spectra obtained along X and Y directions on the cross-sectional sample as shown in fig. 1. It can be found that the Cu-XRF line profile along X-direction in fig. 2 is not as sharp as the Cu^XRF spectra obtained along Y direction in fig. 3. It is owing to the expansion of the incident X-ray beam along the x-direction, which is unavoidable in the current experimental setup.

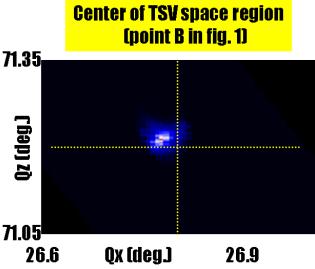

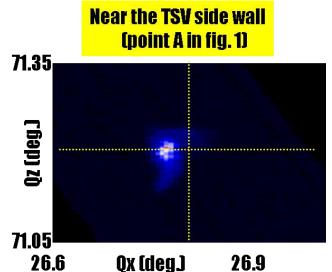

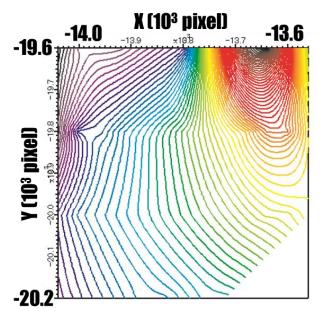

Fig. 4 and fig. 5 show the RLM image obtained for (620) asymmetric Brag reflection at points respectively near the TSV sidewall (point A in figure 1) and the TSV space region (point B in figure 1) As the can be clearly seen from the fig. 4 and 5 that the Si is severely distorted near the TSV sidewall as compared to the Si is severely distorted near the ISV sidewall as compared to the TSV space region. The Si distortion originating from both the lattice spacing change i.e. the spread in the Qz in RLM image and the lattice till i.e. the spread in the Qx in RLM image. The symmetric Bragg peak (440) on the cross-sectional sample also revealed that the Si lattices are highly distorted along the TSV side-wall as compared to the TSV space region. Shown in fig. 6 is the contour diagram of the Qz fitting data obtained from the PLM image 2D Gauss fit over the ractangular area in fig. 1 RLM image 2D-Gauss fit over the rectangular area in fig. 1. Similar to point RLM data, the RLM mapping also confirms the concentration of Si distortion around the TSV side-wall. 3. Summary

The strained-Si structures created around the Cu-TSV structures and in the TSV space region by the thermo-mechanical stress caused by the Cu-TSVs are investigated using µ-XRD. Both the (620) and (440) reciprocal lattice image respectively recorded for asymmetric and symmetric Bragg reflections revealed that the strained Si structure is formed in the vicinity of the TSV sidewall in the cross-sectional sample, which is otherwise difficult to observe by the micro-Raman spectroscopy.

Authors acknowledge Dr. Y. Imai, and Dr. S. Kimura of Japan Synchrotron Radiation Research Institute (JASRI) for their help in carrying out the microdiffraction measurement. The synchrotron radiation experiment was performed with the approval of JASRI Project (No. 2012B1808/BL13XU), Japan.

- References M. Murugesan *et al*, IEDM Tech. Dig., pp. 361 (2009).

- <sup>1</sup>M. Murugesan *et al.*, IEDM Tech. Dig., pp. 301 (2007). <sup>2</sup>M. Murugesan *et al.*, IEDM Tech. Dig., pp. 139 (2010). <sup>3</sup>M. Murugesan *et al.*, IEDM Tech. Dig., pp. 657 (2012). <sup>4</sup>M. Murugesan *et al.*, IEDM Tech. Dig., pp. 657 (2012). <sup>5</sup>M. Murugesan *et al.*, DOI 10.1109/TSM.2014.2316917, IEEE

- Transactions on Semiconductor Manufacturing, (2014). <sup>6</sup>M. Murugesan *et al*, IEDM Tech. Dig., pp. 657 (2013). <sup>7</sup>O. Nakatsuka et al, 3D-IC Tech. Dig., pp.9.3.1-9.3.4 (2011).

- <sup>8</sup>M. Murugesan et al, IEEE Transactions on Electron Devices, Vol. 61, NO. 2, pp.540-547, (2014).

Acknowledgment

## -Area where $\mu$ -XRD data were accumulated - Data accumulation step Along x 2 $\mu$ m/step (40 pixel/step) Along y 10 $\mu$ m/step (200 pixel/step)

Fig. 1: Cross-sectional optical microscopic image revealing the Cu-TSV dimensions and the over which  $\mu$ -XRD analysis was carried out in the high-density 3D-LSI chip.

Fig. 3: In-line Cu-XRF line profile data obtained along the y-direction over the cross-sectional sample as depicted in fig. 1 during  $\mu$ -XRD analysis.

Fig. 5: Reciprocal lattice image obtained at point B (the point at the middle of TSV space region) in fig. 1.

Fig. 2: In-line Cu-XRF line profile data obtained along the x-direction over the cross-sectional sample as shown in fig. 1 during  $\mu$ -XRD analysis.

Fig. 4: Reciprocal lattice image obtained at point A (the point adjacent to the Cu-TSV side wall) in fig. 1.

Fig. 6: Contour diagram revealing 3D distribution of Qz values obtained inside the area shown in dotted line in fig.  $1_\circ$