# Fabrication and Characterization of MoS<sub>2</sub> FET structure with Nano-Sheets Ca<sub>2</sub>Nb<sub>3</sub>O<sub>10</sub> Gate Insulator

Takuhei Kobayashi<sup>1\*</sup>, Soichiro Hirose<sup>1</sup>, Hiroshi Uchida<sup>2</sup>, Takeshi Kawae<sup>1</sup> and Akiharu Morimoto<sup>1</sup>

<sup>1</sup> Graduate School of Natural Science and Technology, Kanazawa Univ., Kakuma-machi, Kanazawa, Ishikawa 920-1155, Japan E-mail: refig@stu.kanazawa-u.ac.jp

<sup>2</sup> Department of Materials and Life Sciences, Sophia Univ., Chiyoda, Tokyo, 102-8554, Japan

# Abstract

Dielectric nano-sheets  $Ca_2Nb_3O_{10}$  (ns-CNO) was supported on several layers  $MoS_2$  transferred on  $SiO_2/p$ -Si substrate by dip-coating at room temperature. We have demonstrated the fabrication of  $MoS_2$  FET structure with ns-CNO gate insulator. The ns-CNO worked as a gate-insulator with good insulating property. Fabricated  $MoS_2$  FET structure indicated n-type FET behavior, and exhibited a current on/off ratio of approximately 1000 by applying the gate voltage of ±4.5 V.

# 1. Introduction

Two-dimensional layered semiconducting materials such as graphene, BN, and MoS<sub>2</sub>, have been extensively studied since thickness of these materials can be readily decreased to atomic length order, which is suitable to realize the nano-scale MOSFET device formation. Especially, single-layer MoS<sub>2</sub> works as a direct gap semiconductor with bandgap of 1.8 eV,<sup>[1]</sup> and Kis et al., reported the fabrication and characterization of single-layered MoS<sub>2</sub> FET structure.<sup>[2]</sup> However, for formation of ultra-thin semiconductor FET, the main problem is difficulty of deposition of gate insulator on the layered semiconducting materials due to their extreme vulnerability. In the device formation process, it causes the defects in the semiconductor/insulator interface, readily. In order to solve this problem, we propose the formation of gate insulator on the MoS<sub>2</sub> using dielectric nano-sheet Ca2Nb3O10 (ns-CNO) by soft-chemical process. The ns-CNO has a ultra-thin two-dimensional structure with a lateral size of several µm scale, and it can be supported on the various substrate materials by dip coating using an aqueous ns-CNO dispersion solution at room temperature.<sup>[3-6]</sup> In this study, we report the fabrication and characterization of MoS2 FET with ns-CNO gate insulator structure on the SiO<sub>2</sub>/Si substrate.

# 2. Experimental

Firstly, p-Si substrates were dipped in a diluted HF solution for removing the native oxide layer. After the HF dipping, thermal oxide layer with thickness of 240 nm was prepared by thermal annealing at 1100 °C for 210 min in  $O_2$ gas flow.

In this study, a natural bulk crystal of MoS<sub>2</sub> was used,

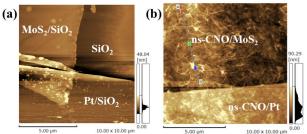

Figure 1 AFM images for (a)  $MoS_2$  on the SiO<sub>2</sub>/p-Si substrate, and (b) ns-CNO on the  $MoS_2$ .

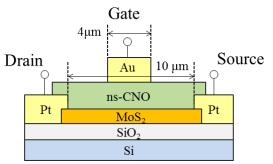

Figure 2 Schematic illustration of  $MoS_2$  FET with ns-CNO gate insulator.

and it was transferred to the SiO<sub>2</sub>/p-Si substrate by conventional tape-casting method. After the several times of tape-casting treatment, in the atomic force microscopy (AFM) observation, MoS<sub>2</sub> with 12.7 nm (equal to 20 layers) were obtained on the substrate as shown in Fig. 1 (a). Pt source and drain electrodes were prepared on the MoS<sub>2</sub> by conventional pulsed laser deposition method and photolithography technique.

After the formation of source and drain electrode, ns-CNO layers were supported on the specimen by dip-coating using an aqueous ns-CNO dispersion solution.<sup>[3,4]</sup> Figure 1 (b) shows the AFM image of ns-CNO supported on the MoS<sub>2</sub>. Observed result indicates all of surface was covered with ns-CNO flakes with 1-2  $\mu$ m size. Also, thickness of ns-CNO was 11.7 nm (equal to 8 layers) from *z*-axis height profile analysis. Finally, Au gate electrode with 4  $\mu$ m width was deposited on the ns-CNO gate insulator by conventional thermal evaporation. A schematic depiction of the fabricated FET device structure is shown in

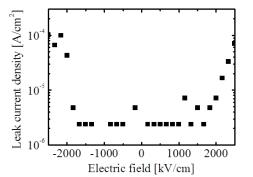

Figure 3 J-E property of Au/ns-CNO/MoS<sub>2</sub> hetero-layered structure.

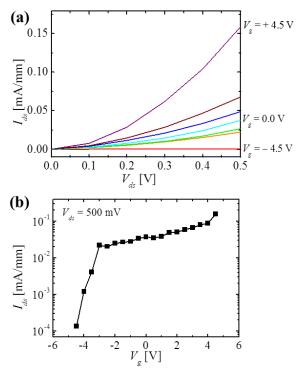

Figure 4 (a)  $I_{ds}$ - $V_{ds}$  curves and (b)  $I_{ds}$ - $V_{g}$  curve of MoS<sub>2</sub> FET with ns-CNO gate insulator.

# Fig. 2.

We performed electrical measurement of specimen by using pA-meter (Agilent HP4140B) with gate voltage source at room temperature.

### 3. Results and Discussion

Figure 3 shows the leakage current density versus electric field (J-E) curve of Au/ns-CNO/MoS<sub>2</sub> gate structure. In the range of applied electric field less than 2000 kV/cm, the ns-CNO indicates excellent insulating property without any conducting pass in the boundary even though ns-CNO was a flake-like and ultra-thin layered structure.

Figure 4 (a) is drain current versus drain voltage  $(I_{ds}-V_{ds})$  curves of MoS<sub>2</sub> FET with ns-CNO gate structure with changing the applied gate voltage  $V_g$  in the range from -4.5 V to +4.5 V. As shown in the figure, the specimen shows a typical behavior of FET with n-type channels.

These results indicate the new type of FET structure using nano-sheet materials can be prepared by present soft-chemical method.

Figure 4 (b) shows  $I_{ds}$ - $V_g$  curve of specimen. Here, measurement was carried out at the fixed  $V_{ds}$  of 0.5 V. A current on/off behavior was clearly observed, and highest on/off current ratio was approximately 1000 by applying the gate voltage in the range from -4.5 V to +4.5 V. Observed on/off current ratio is higher than that of ALD-Al<sub>2</sub>O<sub>3</sub> top gate MoS<sub>2</sub> FET structure (about several hundred).<sup>[7]</sup> This means that the present ns-CNO soft-chemical supporting process can reduce the degradation of insulator/MoS<sub>2</sub> interface compared to conventional film deposition process.

#### 3. Conclusions

We have demonstrated the fabrication of  $MoS_2$  FET with ns-CNO gate insulator structure on the SiO<sub>2</sub>/Si substrate. The ns-CNO worked as a gate-insulator with good insulating property. Fabricated  $MoS_2$  FET structure indicates n-type FET behavior, and exhibits a current on/off ratio of approximately 1000 by applying the gate voltage of ±4.5 V.

#### Acknowledgements

This work was partly supported by a research grant from the Hokuriku bank young scientist foundation. The authors would like to thank Professor H. Okudera of Kanazawa University for his considerable help and technical assistance.

## References

- [1] K. F. Mak, C. Lee, J. Hone, J. Shan, and T. F. Heinz, Phys. Rev. Lett. **105** (2010) 136805.

- [2] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nature Nanotech. 6 (2011) 147.

- [3] M. Osada, and T. Sasaki, J. Mater. Chem. 19 (2009) 2503.

- [4] M. Osada, K. Akatsuka, Y. Ebina, H. Funakubo, K. Ono, K.

- Takada, and T. Sasaki, ACS Nano 4 (2010) 5225.

- [5] Y. Kondo, K. Sasajima, M. Hayashi, J. Kimura, I. Takuwa, Y. Ehara, H. Funakubo, and H. Uchida, Jpn. J. Appl. Phys. 50 (2011) 09NA04.

- [6] Y. Minemura, K. Nagasaka, T. Kiguchi, T. J. Konno, H. Funakubo, and H. Uchida, Jpn. J. Appl. Phys. 52 (2013) 09KA04.

- [7] H. Liu, and P. D. Ye, IEEE Electr. Dev. Lett. 33 (2011) 546.