## Strained Si<sub>0.1</sub>Ge<sub>0.9</sub> on Strained-Si-on-Insulator (sSOI) pMOSFETs for Low-Power sSOI based CMOS

Keiji Ikeda\*, Yoshihiko Moriyama, Toshifumi Irisawa, Mizuki Ono, Yuuichi Kamimuta, Minoru Oda, Tomonori Miyaki, Etsuo Kurosawa and Tsutomu Tezuka Collaborative Research Team Green Nanoelectronics Center (GNC),

National Institute of Advanced Industrial Science and Technology (AIST), Onogawa 16-1, Tsukuba, Ibaraki 305-8569, Japan. Present address: Toshiba Corporation E-mail: keiji.ikeda@toshiba.co.jp

## Abstract

We demonstrate a high hole mobility ( $\mu_{\rm eff} = 475~{\rm cm}^2/{\rm Vs}$  at  $N_{\rm s} = 5.0{\rm x}10^{12}{\rm cm}^2$ ) of an anisotropically strained Si<sub>0.1</sub>Ge<sub>0.9</sub> pMOSFET of which channel was directly grown on a strained-Si on insulator (sSOI) substrate for the first time. The best subthreshold slope value (S.S. = 78 mV/dec.) among strained-Ge or Ge-rich SiGe channel pMOSFETs was obtained. The use of an alloy channel rather than pure Ge one is a key to realize such excellent mobility and S.S. values simultaneously because of the suppression of dislocation introduction and hole generation in the channel in spite of the large misfit strain. Introduction

High mobility channel materials are widely explored to replace Si in MOSFET devices to suppress the power consumption by lowering supply voltages,  $V_{\rm dd}$ , without degrading circuit performance. strained-Ge[1-6] and strained-SiGe[7-10] is promising option for p-channel FETs due to its significantly high promising option for p-channel FE1s due to its significantly high hole-mobility and compatibility with Si-CMOS process. On the other hands, FD-SOI devices such as ETSOI and UTBB have been extensively investigated as a 22nm node and beyond[7-10]. Excellent performance is achieved for low-power application owing to better short channel control. However, several key challenge is remain to achieve high-performance because of the probability of the test of the probability of the performance because the performance because the performance because the performance because the perfor embedded stressor is less effective to these devices[8]. Although, introducing of strained-Si on insulator (sSOI) channel is a promising solution as a performance booster for nFET, tensile strain of sSOI channel degrades hole-mobility in pFET. To improve the pFET performance, strained-SiGe channel which formed by local Ge condensation have been demonstrated[7-10]. However, Ge content in SiGe channel is less than 35% and much higher Ge content is required for further mobility enhancement. Here, direct epitaxial growth of Ge on sSOI on the pFETs regions is a promising and simpler way to obtain higher mobility p-channels. In general, however, it is difficult to eliminate dislocation introduction in such high misfit-strain system. Actually, Si-core/Ge-shell nanowire pMOSFET have been demonstrated by Hashemi *et. al.* with CMOS compatible top-down approach using selective epitaxial growth of pure-Ge on SOI fin structure[11]. But its hole mobility was severely deteriorated to less than ~80 cm<sup>2</sup>/Vs caused by dislocation introduction into Ge shell. In this paper, we demonstrate that a strained Ge-rich SiGe alloy channel on sSOI is more beneficial to avoid dislocation introduction and to realize higher mobility than a Ge channel on the substrate. Pseudomorphically strained Ge-rich SiGe alloy  $(Si_{0.1}Ge_{0.9})$  channel MOSFETs on sSOI substrate having a TaN / Si passivation / HfO<sub>2</sub> gate stacks were fabricated and a high effective hole mobility ( $\mu_{\rm eff}$  = 475 cm<sup>2</sup>/Vs at  $N_{\rm s}$  = 5.0x10<sup>12</sup>cm<sup>2</sup>) and excellent subthreshold slope value (S.S. = 78 mV/dec.) were achieved simultaneously.

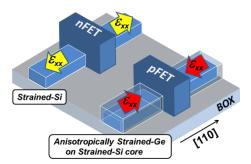

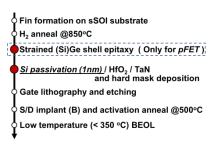

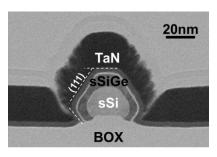

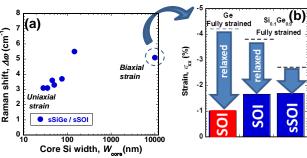

Device fabrication Figure 1 shows a concept of proposed CMOS, featuring sSOI channel for nFET and strained (Si)Ge channel on sSOI for pFET. This architecture can enjoy the high mobility channels by simple process steps compared with local Ge condensation. Key fabrication steps of strained-(Si)Ge channel on sSOI MOSFETs are summarized in Fig. 2. Firstly, strained-Si channel was formed by mesa etching of sSOI (~1% biaxial tensile strain) substrates. Here, priestropic strain relevation of strained Si, mose induced uniaviel. anisotropic strain relaxation of strained-Si mesa induced uniaxial stress along the channel direction to narrow fins. Then, hydrogen annealing at 850°C was carried out to improve channel surface roughness and shrinkage of fin width. After that, strained-(Si)Ge channel and 1-nm thick Si passivation were grown by RPCVD at 380°C only for pFETs. A 4 nm- HfO<sub>2</sub> layer was then grown by using an atomic layer deposition system. Figure 3 shows a xTEM of the narrowest channel with a core-Si width ( $W_{\text{core}}$ ) of 28nm. It is clearly seen that smooth and circular shape of strained-Si core due to the effect of hydrogen annealing. Moreover, sidewalls of SiGe channel was mainly formed on the (111) facets. Figure 4 shows the comparison of xTÉM between pure-Ge on sSOI and  $Si_{0.1}Ge_{0.9}$  on sSOI. In pure-Ge on sSOI, dislocation which formed by strain relaxation was observed. On the other hands, dislocation formation is effectively suppressed in  $Si_{0.1}Ge_{0.9}$  on sSOI by alleviation of lattice mismatch between shell and core materials. The  $W_{\rm core}$  dependence of measured Raman peak shift,  $\Delta \omega$  is shown in

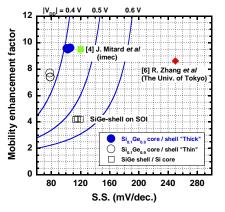

Fig.5(a). Extremely high (over -2.7%) compressive strain, which is almost identical with the misfit strain between Si<sub>0.1</sub>Ge<sub>0.9</sub> and sSOI core, was evaluated at  $W_{\rm core} = 145$  nm. And comparison of remaining strain in channel direction,  $\varepsilon_{\rm xx}$  in pure-Ge and Si<sub>0.1</sub>Ge<sub>0.9</sub> channels  $\varepsilon_{\rm xx}$  at biaxially strained wide  $W_{\rm core}$ , is shown in Fig.5(b). The Si<sub>0.1</sub>Ge<sub>0.9</sub> channel has larger  $\varepsilon_{\rm xx}$  than that for pure-Ge because of suppression of dislocation formation by alloy effect[12].

Hole-mobility characterization

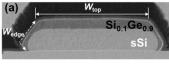

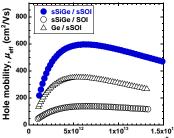

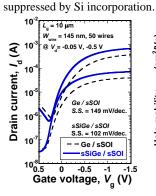

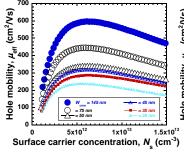

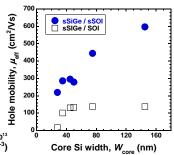

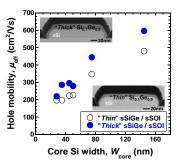

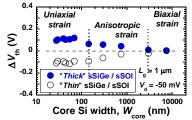

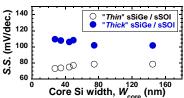

Hole mobility was extracted by a split CV method for long-channel and multi-wire devices.  $N_s$  is the average surface carrier density defined by  $N_s = N_1 / (W_{\text{top}} + 2 W_{\text{edge}})$ , where  $N_1$  is the line inversion carrier density obtained from CV measurement.  $W_{\text{top}}$  and  $W_{\text{edge}}$  represent the wire width on top surface and length of faceted wedge represent the with the first top surface and religin of faceted edges, respectively as shown in Fig. 4(a). Figure 6 shows the comparison of hole-mobility of the fabricated multi-wire MOSFETs. Here, Si<sub>0.1</sub>Ge<sub>0.9</sub> on sSOI, Si<sub>0.1</sub>Ge<sub>0.9</sub> on SOI and pure Ge on sSOI were used for comparative evaluation. Thanks to high on sSOI were used for comparative evaluation. Thanks to fight compressive strain along the channel and less defective condition by avoiding strain relaxation, the  $Si_{0.1}Ge_{0.9}$  on sSOI device show the highest mobility of 597 cm<sup>2</sup>/Vs at  $N_s = 6.0 \times 10^{12}$  cm<sup>2</sup> even though the mobility of pure Ge on sSOI was less than 360 cm<sup>2</sup>/Vs. This result suggests that the advantage of  $Si_{0.1}Ge_{0.9}$  in terms of the suppression of dislocation formation. Not only the current drive but suppression of dislocation formation. Not only the current drive but the S.S. value was also improved as shown in Fig. 7. Figure 8 shows the effective hole mobility,  $\mu_{\rm eff}$  of anisotropically strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI MOSFETs with different core width,  $W_{\rm core}$ . The mobility was decreased by shrinking  $W_{\rm core}$ . Figure 9 shows the comparison of  $W_{\rm core}$  dependence of peak mobility between strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI and  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI was increased with increasing  $W_{\rm core}$  even though the mobility of strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on SOI core was almost unchanged. This mobility improvement can be explainable by the effect of anisotropic strain applied in  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI. On the other hands, at narrow  $W_{\rm core}$  region, mobility was severely degraded at both devices. This effect might be due to the increased contribution of (111) sidewalls. To solitive was severely degraded at both devices. This effect might be due to the increased contribution of (111) sidewalls. To understand this strain and sidewall effect, "thin" strained  $Si_{0.1}Ge_{0.9}$  on sSOI core pMOSFETs was evaluated. Figure 10 shows the comparison of  $W_{\rm core}$  dependence of peak mobility,  $\mu_{\rm eff}$  for "thick ( $t_{\rm SiGe} = 4 \sim 8$  nm)" and "thin ( $t_{\rm SiGe} = 2 \sim 6$  nm)" anisotropically strained  $Si_{0.1}Ge_{0.9}$  on sSOI pMOSFETs. The mobility enhancement by "thin" strained  $Si_{0.1}Ge_{0.9}$  channel was also achieved. And almost same  $W_{\rm core}$  dependency was observed. Figure.11 shows the comparison of  $W_{\rm core}$  dependence of threshold voltage shift,  $\Delta V_{\rm th}$  between "thick" and "thin" strained- $Si_{0.1}Ge_{0.9}$  on sSOI. The  $V_{\rm th}$  of "thin" strained  $Si_{0.1}Ge_{0.9}$  was negatively shifted by decreasing  $W_{\rm core}$ . This negative  $V_{\rm th}$  shift can be attributable to the valence band energy modulation by changing the strain from biaxial to uniaxial. On the other hands, the  $V_{\rm th}$  of "thick" strained  $Si_{0.1}Ge_{0.9}$  was positively shifted by decreasing  $W_{\rm core}$ . Moreover, subthreshold slope S.S. of "thick" strained  $Si_{0.1}Ge_{0.9}$  was also degraded by decreasing  $W_{\rm core}$  even though that for "thin" strained  $Si_{0.1}Ge_{0.9}$  was improved (Fig. 12). These results suggest that the  $D_{\rm it}$  at 111 indicated and the size of the Section of the strain that the  $D_{\rm it}$  and  $D_{\rm it}$  is the strain of the strain of the strain of  $D_{\rm it}$  is the strain of the strain of  $D_{\rm it}$  and  $D_{\rm it}$  is the strain of  $D_{\rm it}$  and  $D_{\rm it}$  is the strain of  $D_{\rm it}$  and  $D_{\rm it}$  and  $D_{\rm it}$  is the strain of  $D_{\rm it}$  and  $D_{\rm i$ improved (Fig. 12). These results suggest that the  $D_{\rm it}$  at (111) sidewalls and/or hole generation in the channel deteriorate the S.S. values. And it might be suppressed by thinning the strained Si<sub>0.1</sub>Ge<sub>0.9</sub> channel. In order to benchmark the performance for low-SI<sub>0.1</sub>Ge<sub>0.9</sub> channel. In order to benchmark the performance for low-power operation, Fig. 13 shows a metrics of hole mobility enhancement factor against Si at  $N_s = 5 \times 10^{12} \text{cm}^2$  [13] versus subthreshold slope, S.S. value. The obtained combination of hole mobility enhancement factor of 7.7 against that of a Si counterpart and S.S. value of 78mV/dec. exhibits a potential to reduce the  $|V_{dd}|$  lower than 0.5V with keeping a comparable intrinsic gate delay.

Conclusions

Anisotropically strained Si<sub>0.1</sub>Ge<sub>0.9</sub> on sSOI pMOSFETs with high hole mobility and excellent *S.S.* values were demonstrated. The alloy channel was shown to be beneficial to prevent the lattice andy chainfel was shown to be beneficial to prevent the lattice relaxation in spite of the high misfit strain. The obtained combination of hole mobility enhancement factor of 7.7 against that of a Si counterpart and S.S. value of 78mV/dec. exhibits a potential to reduce the  $|V_{dd}|$  lower than 0.5V with keeping a comparable intrinsic gate delay. The result indicates that strained Ge-rich SiGe on sSOI pMOSFETs are promising for low-power sSOI-CMOS LSIs.

**Fig. 1** Concept of proposed CMOS featuring sSOI nFET and strained-(Si)Ge / strained-Si channel pFET.

Fig. 2 Fabrication process of strained-Si core/ strained-(Si)Ge shell MOSFETs with Si passivation/HfO<sub>2</sub> gate stack.

**Fig. 3** Cross-sectional TEM image of strained Si<sub>0.1</sub>Ge<sub>0.9</sub>-shell on sSOI core with the narrowest core-Si width of 28nm.

**20nm Fig. 4** Cross-sectional TEM images of (a) Ge on sSOI and (b) Si<sub>0.1</sub>Ge<sub>0.9</sub> on sSOI after full processing. Dislocation

formation in shell channel is effectively

**Fig. 5** (a) Measured Raman peak shift,  $\Delta \omega$  of Ge-Ge peak and (b) Comparison of remaining strain in channel direction,  $\varepsilon_{xx}$  in pure-Ge and  $Si_{0.1}Ge_{0.9}$  channels  $\varepsilon_{xx}$  at biaxial strained wide  $W_{core.}$

Surface carrier concentration,  $N_{\rm s}$  (cm<sup>-3</sup>) Fig. 6 Comparison of effective hole mobility,  $\mu_{\rm eff}$  of anisotropically strained (Si)Ge pMOSFETs ( $W_{\rm core} = 145 \, \rm nm$ ) with different cores.

**Fig. 7** Comparison of  $I_{\rm d}$ - $V_{\rm g}$  characteristics of strained Si<sub>0.1</sub>Ge<sub>0.9</sub> on sSOI and pure Ge on sSOI pMOSFETs.

**Fig. 8** Effective hole mobility,  $\mu_{\rm eff}$  of anisotropically strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI pMOSFETs with different core width,  $W_{\rm core}$ .

**Fig. 9** Comparison of  $W_{\rm core}$  dependence of peak mobility,  $\mu_{\rm eff}$  for strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on sSOI and strained  ${\rm Si}_{0.1}{\rm Ge}_{0.9}$  on SOI pMOSFETs.

**Fig. 10** Comparison of  $W_{\rm core}$  dependence of peak mobility,  $\mu_{\rm eff}$  for "Thick ( $t_{\rm SiGe} = 4{\sim}8$  nm)" and "Thin ( $t_{\rm SiGe} = 2{\sim}6$  nm)" anisotropically strained Si<sub>0.1</sub>Ge<sub>0.9</sub> on sSOI pMOSFETs.

**Fig.11** Core width,  $W_{\text{core}}$  dependence of linear threshold voltage shift,  $\Delta V_{\text{th}}$ .

**Fig.12** Core width,  $W_{\text{core}}$  dependence of subthreshold slope S.S.

**Fig.13** Benchmark of hole mobility enhancement factor with respect to MG/HK Si counterpart [13] vs S.S. Lines show required mobility enhancement at each  $|V_{\rm dd}|$ . Larger mobility enhancement with lower S.S. can reduce  $|V_{\rm dd}|$  under the constant CV/I.

## References

- [1] R. Pillarisetty et al., IEDM p.150(2010).

- [2] K. Ikeda et al., VLSI Symp. p.165(2012).

- [3] W. Chern et al., IEDM p.387(2012).

- [4] J. Mitard et al., VLSI Symp. p.T20 (2013).

- [5] K. Ikeda et al., VLSI Symp. p.T31(2013).

- [6] R. Zhang et al., IEDM p.663(2013).

- [7] K. Chang et al., IEDM p.419(2012).

- [8] A. Khakifirooz et al., VLSI Symp. p.117(2012).

- [9] P. Hashemi et al., VLSI Symp. p.T19 (2013).

- [10] Q. Liu et al., IEDM p.228 (2013).

- [11] P. Hashemi et al., Appl. Phys. Lett. 96, 063109 (2010).

- [12] I. Yonenaga, J. Mater. Sci: Mater. Electron. 10, 329 (1999).

- [13] M. Chudzik et al., VLSI Symp. p.194(2007). Acknowledgement

## The authors would like to thank Drs. N. Yokoyama, T. Kanayama, A. Nishiyama, J. Koga, and K. Muraoka for their support throughout this work. This work was granted by JSPS through FIRST Program initiated by the Council for Science and Technology Policy (CSTP).