# Experiment Study on Random Telegraph Signal Noise in (110) pMOSFETS with 1nm EOT

Jiezhi Chen and Yuichiro Mitani

Advanced LSI Technology Laboratory, Corporate Research & Development Center, Toshiba Corporation 1 Komukai Toshiba-cho, Saiwai-ku, Kawasaki 210-8582, Japan

Tel: +81-44-549-2188, Fax: +81-44-520-1804, Email: chen.jiezhi@toshiba.co.jp

#### Abstract

In this work, random telegraph signal (RTS) noise are investigated in (110)-orientated pFETs with 1nm thick  $SiO_2$  and various channel doping concentrations, with main focus on properties of traps that locate besides the interface of  $SiO_2$  and the substrate. Carrier trapping time constants, couplings and carrier trapping induced channel current fluctuations are systematically measured for comprehensive understandings. On the one side, although degradations of drain current fluctuations and threshold voltage shifts are observed in pFETs with stronger channel doping, this cannot be well explained by trap number differences that used to explain RTS noise in nFETs. On the other side, in pFETs with thinner  $SiO_2$ , unexpected stronger time constants. Possible underlying mechanisms are also discussed.

#### Introduction

Along with device scaling techniques, device area turns to be smaller and smaller, while this brings many challenges on reliabilities of devices and circuits. As an example, random telegraph signal (RTS) noise turns to be a big problem because one single trap can trigger larger current fluctuations in smaller devices. Considering its serious impacts on logic circuits [1] and memories [2], studies on RTS noise have been intensively reported recently. However, understandings on RTS noise related traps are still not enough due to large variations and trap diversities. Though RTS noise in devices with thick dielectrics has been investigated in previous work [3-5], it is still unclear whether we are talking about traps in the dielectric or traps just besides the interface, while this is important for our understandings on RTS noise mechanisms.

Systematical studies on RTS noise in pFETs with 1nm thick SiO<sub>2</sub> are done in this work, aiming at understandings on impacts and properties of traps that locate just besides the interface between the substrate and gate dielectrics. On the one hand, (110) pFETs are characterized because RTS noise in (110) pFETs is much more serious than that in (100) pFETs, and this could be a key problem for 3D device with multiple surface orientations. On the one hand, RTS traps induced current fluctuations ( $\Delta I_d/I_d$ ) and threshold voltage shifts ( $\Delta V_{th}$ ) are compared in pFETs with various channel doping concentrations (N<sub>ch</sub>). To understand trapping and de-trapping processes of RTS traps that locate just besides the interface, time constants and couplings to the applied gate bias (V<sub>g</sub>) of each single trap are also summarized and discussed.

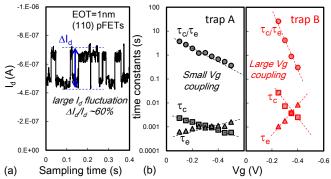

Fig.1 (a) Observation of large  $I_d$  fluctuations in pFETs with 1 nm SiO<sub>2</sub>; (b) time constant ( $\tau_c, \, \tau_e, \, \tau_c/\tau_e)$  dependences on  $V_g$ , here two traps with large and small  $V_g$  couplings are illustrated.

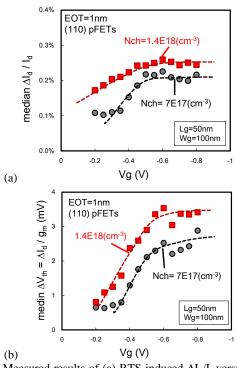

Fig.2 Measured results of (a) RTS induced  $\Delta I_d/I_d$  versus  $V_g$  and (b)  $\Delta V_{th}$  versus  $V_g$ , in (110) pFETs. Dotted lines are used for eye guide.

## **Experimental Results and Discussions**

RTS noise is studied in (110) pFETs with 1nm SiO<sub>2</sub> gate oxide and various channel doping concentrations, ranging from 7E17cm<sup>-3</sup> to 1.4E18cm<sup>-3</sup>, by using Agilent B1530 RTS noise characterization system. Though SiO<sub>2</sub> is ultrathin, large current fluctuations  $\Delta I_d/I_d$  can be clearly observed (Fig. 1(a)). In Fig. 1(b), two different traps with large V<sub>g</sub> couplings and small V<sub>g</sub> couplings are illustrated. For multiple traps, histogram graph of drain currents or time lag plot (PLT) [6] can be utilized to estimate trap numbers, as well as  $\Delta I_d/I_d$  and  $\Delta V_{th}$ . For a single trap, time constants, such as time to capture ( $\tau_c$ ), time to emission ( $\tau_e$ ), and time constant couplings on the applied gate bias V<sub>g</sub> ( $\alpha_{\tau e}$ ,  $\alpha_{\tau e}$ ,  $\alpha_{\tau e/\tau c}$ ), can be estimated.

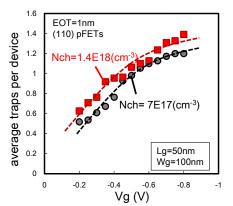

Firstly, both single trap and multiple traps are evaluated for statistical analysis on RTS noise. Here,  $\Delta V_{th}$  is estimated by using  $\Delta V_{th} = \Delta I_d(V_g)/g_m(V_g)$ , with measured  $g_m$  from  $I_d - V_g$ curves and  $\Delta I_d$  from  $I_d$  sampling. As shown in Fig. 2, similar to our previous work in nFETs and pFETs with 2nm SiO<sub>2</sub> [4, 5], large degradations of both  $\Delta I_d/I_d$  and  $\Delta V_{th}$  can be observed in pFETs with larger N<sub>ch</sub>, especially in the sub-threshold voltage region at low Vg. Interesting thing is that, as observed in [5],  $\Delta I_d / I_d$  turns to be larger at higher  $V_g$  in pFETs, while it has weak dependences on  $V_g$  in nFETs. Also,  $\Delta V_{th}$  saturation region at higher Vg cannot be found in nFETs [4] but can be observed in pFETs. Then, from estimated RTS trap densities shown in Fig.3, it is found that N<sub>ch</sub> impacts on RTS traps observation are small. In other words, number fluctuation model that used to explain RTS noise in nFETs [4] cannot be used in pFETs, and the mobility fluctuation model could be the dominant mechanism for observed large RTS noise degradations in pFETs with heavily doped channel. With a hypothesis that  $\Delta \mu_{eff}$  is identical, carrier mobility ( $\mu_{eff}$ ) degradations in heavily doped pFETs could result in enhanced mobility fluctuations ( $\Delta \mu_{eff}/\mu_{eff}$ ) [8].

Fig.3  $V_g$  dependences of average trap numbers per device, which are estimated from  $I_d$  fluctuation levels [5, 6].

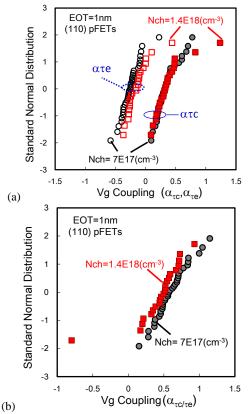

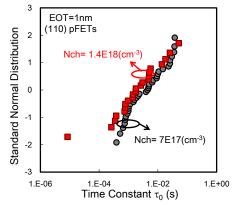

Fig.4 Channel doping dose dependences of (a) time constant  $\tau_0$ , and (b) time constant couplings to  $V_g$ ,  $\alpha_{\tau c}$  and  $\alpha_{\tau e}$ .

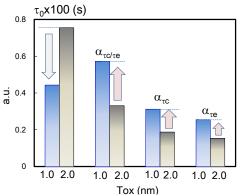

For understandings on mechanisms of RTS related traps, time constant couplings of  $\alpha_{\tau c},\,\alpha_{\tau e}$  and  $\alpha_{\tau c/\tau e}$  are summarized in Fig.4, by measuring  $V_g$  dependence of  $\tau_c$  and  $\tau_e$  of each single trap. On the one side, identical distributions of  $\alpha_{re}(\alpha_{rc})$ in pFETs with various channel doping are observed, which is similar to our previous work in (110) and (100) pFETs with 2nm SiO<sub>2</sub> [4, 5], except enhanced  $\alpha_{\tau c}$  in (100) pFETs with heavier channel doping. On the other side, it is found that  $\alpha_{\tau c/\tau e}$  were not be enhanced by stronger channel doping, which is similar to 2nm SiO<sub>2</sub> pFETs but different from nFETs [5]. In other words, impacts of random dopant fluctuations (RDF) on  $\alpha_{\tau c/\tau e}$  [9] in pFETs are kind of weak in comparison to that in nFETs. On the contrary,  $\alpha_{\tau c/\tau e}$  turns to be smaller in pFETs with heavily doped channels. Actually, definitions of trap depth (X<sub>T</sub>) and  $\alpha_{\tau c/\tau e}$  are same [6],  $\alpha_{\tau c/\tau e} \sim X_T/T_{ox}$ . In the carrier transport channel, carriers in the inversion layer distribute in subbands with discrete energy levels and a distance from the interface. Supposing that  $z_{inv}$  is the average distance from the surface to electrons in the inversion layer,  $\alpha_{\tau c/\tau e}$  expression should be  $(X_T+z_{inv})/T_{ox}$ , which can be modulated by different channel doping. Similarly, in Fig.5, faster  $\tau_0$  in heavily doped pFETs are observed, which could also come from different inversion carrier distributions if trap distributions are identical. Next, time constants and couplings in pFETs with different SiO<sub>2</sub> thickness are compared in Fig. 6. Faster  $\tau_0$  in thinner SiO<sub>2</sub> can be understood since observed traps are limited within 1nm depth from the interface. The interesting thing is that time constant couplings turn to be enhanced in thinner SiO<sub>2</sub>. In traditional RTS noise model [6], V<sub>g</sub> couplings should be suppressed if traps locate closer to the interface. Though further study is required to understand this, it might be related to the low trap activation energies (E<sub>c</sub>) by taking the band-gap narrowing effects at Si/SiO<sub>2</sub> interface into account [7].

Fig.5 Distributions of time constant couplings  $\alpha_{\tau c/\tau e}$ , in devices with various channel doping dose  $N_{ch}$ .

Fig.6 Comparisons between (110) pFETs of different  $SiO_2$  thickness, a part of data in 2nm  $SiO_2$  (110) pFETs is cited from ref. [7].

### Conclusions

A systematically study on RTS noise in (110) pFETs with 1nm SiO<sub>2</sub> are described in this work. On the one side, it is observed that channel doping concentration does not largely affect observed RTS trap densities, time constants and couplings. On the other side, larger degradations of current fluctuations and threshold voltage shifts are still observed in heavily doped pFETs. With further discussions, it is believed that the mobility fluctuation model is adoptable in pFETs with ultrathin SiO<sub>2</sub>. Also, in comparison to RTS noise in pFETs with thick SiO<sub>2</sub>, unexpected stronger time constant couplings are observed together with faster time constants. Underlying mechanisms are discussed for understandings.

(The authors would like to thank Dr. M. Saitoh for the sample provision, Dr. Higashi and Dr. Kato for helpful discussions)

**Reference:** [1] M. Gonthier *et al.*, IEDM 2011, p.183; [2] D. Kang *et al.*, VLSI2011, p.206; [3] H. Miki *et al.*, VLSI 2011, p.148; [4] J. Chen et al., SSDM2013, p.724; [5] J. Chen et al., VLSI2013, p.184; [6] T. Nagumo *et al.*, IEDM 2009, p.759; [7] J. Chen et al., to be presenated in VLSI2014; [8] K. K. Hung *et al.*, TED, 37(3), p.654; [9] C. M. Compagnoni *et al.* TED, 59(9), p.2459.