# Impact of Gate Coupling and Misalignment on Performance of Double-gate Organic Thin Film Transistors

Jing-Wen Han, Lei Sun\*, Yu-Qian Xia, Hao Xu, Yi-Bo Zhang, Sheng-Dong Zhang and Yi Wang

Institute of Microelectronics, Peking University, Beijing 100871, P. R. China \*Email: sunl@pku.edu.cn, Fax: (+) 86-10-62751789

#### Abstract

We propose the numerical simulation of the electrically separable dual-gate organic thin film transistors (DG-OTFTs). It is revealed that double-gate architecture is able to dynamically control the threshold voltage by the coupling of the two gates. We also observe that the device characteristics are sensitive to the misalignment, a significant change to the driving ability and threshold voltage when misalignment exists.

## 1. Introduction

Organic thin film transistors (OTFTs) have received intensive studies on the application of flexible displays, sensors, and power transmission devices, etc., in recent years. OTFT have the advantages of easy processing, low production costs, and compatibility with flexible substrates. The increase of OTFT's carrier mobility is in the speed of ten orders per two years on average, which has reached the level of the overall performance of amorphous silicon TFT<sup>[1]</sup>. Currently, the maximum hole-transport mobility has reached 35cm<sup>2</sup>/Vs by using the single crystal pentacene <sup>[2]</sup>. In recent years, OTFTs with two electrically separated gates (DG-OTFTs), have been proposed for the applications, such as the dynamic threshold voltage control to maximize on-current and minimize off-current. Furthermore, DG-OTFTs can also refrain from short channel effect for extremely scaled CMOS technology generations.

In this paper, a simulation of DG-OTFTs is conducted by Silvaco ATLAS TCAD tools, and the effect of dynamic coupling of the top and bottom gates of the DG-OTFTs and the impact of misalignment on the threshold voltage modulation is characterized and discussed.

## 2. Device simulation and material parameters

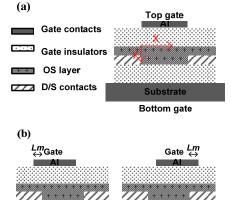

*Fig.*1 shows the sketche of the DG-OTFTs, *Lm* represents the misalignment between top and bottom gates. We define *Lm* is positive when the mismatch is moved to drain, and to source is negative. The devices are assumed to be p-type with gate insulator thickness of 50 nm for both top gate and bottom gate. The channel material is pentacene with thickness of 50nm and the channel length for DG-OTFTs is varied from 1um to 20um. Since many organic materials can be purified at a high degree, the channel is considered without any doping. The material properties of metal contact and pentacene are listed in Table 1<sup>[3]</sup>. Unlike the traditional inorganic semiconductors, pentacene normally shows the increasing of carrier mobility as electric field increase <sup>[4]</sup>. The implemented mobility is given by  $\mu = \mu_0 exp(E/E_0)^{1/2}$ , where  $\mu_0$  is the zero field mobility and E<sub>0</sub> is a critical field.

## 3. Results and discussion

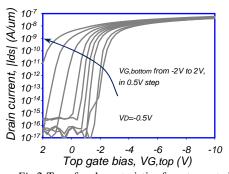

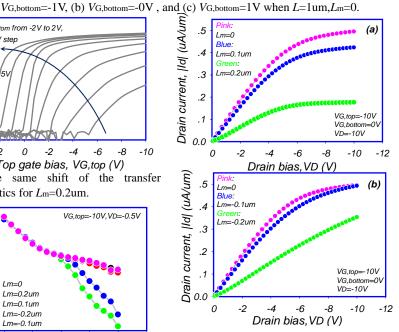

From *Fig.*2, we can see the bottom gate bias,  $V_{G,bottom}$  results in a change in the transfer characteristics of a top gated OTFT (channel length *L*=1um). While bottom bias  $V_{G,bottom}$ =0V, there is no significant charge accumulated in the bottom channel, shown as the middle transfer curve in *Fig.*2.

The effect of the bottom gate bias on the transistor is negligible, and the DG-OTFT acts as a conventional single-gate transistor. With positive bottom bias, the accumulated charges in the bottom channel are depleted <sup>[5]</sup>, the *I-V* curves move to the right side. With negative bottom bias, the second channel is forming and the channel opens earlier, therefore the threshold voltage reduces as the *I-V* curves move to the left side.

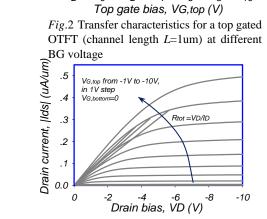

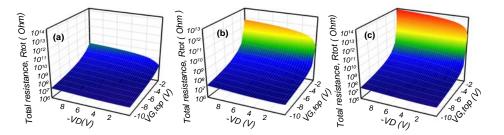

*Fig.*3 shows the resulting output characteristics with a fixed bottom gate voltage, the total resistance ( $R_{tot}$ ) is obtained as  $R_{tot}=V_D/I_D$ , with corresponding drain voltage ( $V_D$ ) and current ( $I_D$ ), respectively. The reciprocal of the straight lines' slope represents the total resistance. *Fig.*4 plots the overall resistance with three different  $V_{G,bottom}$ . Significant decrease of  $R_{tot}$  is observed, as  $V_{G,bottom}$  changes to be negative. In a word, the second gate can electrically modify the charge carrier distribution in the channel which is accumulated by the first gate modification, and dynamically control the threshold voltage.

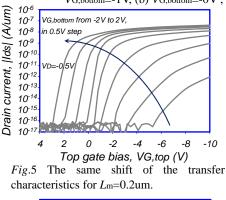

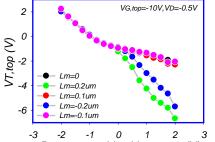

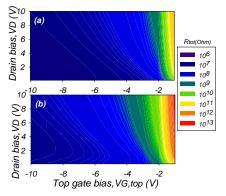

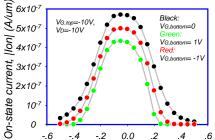

Fig.5 exhibits the shift of the transfer characteristics when the misalignment exists, which is described in Fig.1b. Compared with the case in Fig.2, obvious difference of the threshold voltage shift for the top gate can be easily found with positive bottom bias. The extracted  $V_{T,top}$  results are shown in Fig.6.  $V_{T,top}$  increases with larger  $L_m$  and changes a lot under more positive bottom gate bias. Fig.7 plots  $R_{tot}$ results when  $L_m$  exists or not, and  $R_{tot}$  increases obviously with small  $V_{G,top}$ .

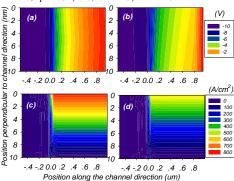

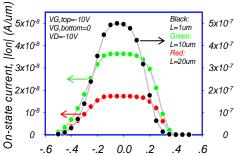

Fig.8 (a)-(d) show the 2D distributions of potential and hole current density along the channel direction with various  $L_m$  respectively. There exists a large variation in potential and hole current density distributions when  $L_m$  exists. And the distributions are reduced, comparing with  $L_m=0$  case. It is because that partial port of the channel is unable to accumulate, thus increase  $R_{tot}$ , and the driving ability is scaled down. Fig.9 plots the output characteristics with various  $L_m$ . The driving-ability is reduced with larger  $L_m$  and the results are different when the mismatch direction is moved to source or drain. The extracted ON-state current with the  $L_m$  is shown in Fig.10. At  $L_m=0.2$ um, the driving-current decreases 64.4%, 18.8% and 14.0% for L=1um, L=10um, L=20um respectively. And the decrement is corresponding 28.7%, 13.0% and 11.0% while  $L_m$ =-0.2um as shown in Fig.11, the degradation is weakened for large channel devices.

#### 4. Conclusions

We have discussed the performance of DG-OTFTs with device simulations. The effects of the dynamic coupling and the misalignment of the top and bottom gate of the DG-OTFTs on the threshold voltage modulation have been analyzed. The variations of driving current and threshold voltage increase with lager  $L_m$ , and are sensitive to the moving direction between top gate and source/drain contact. The degradation is severe when mismatch moving to drain contact side, and is relaxed for large channel devices. The impact of misalignment can be controlled with selecting suitable channel length.

#### Reference

[1] Klauk H., Chem. Soc. Rev., 39.7 (2010): 2643-2666.

- [2] Jurchescu D., et al, Adv. Mater., 19.5 (2007): 688-692.

- [3] Berliocchi M., et al., Semicond. Sci. Technol., 19.4 (2004): S354.

- [4] Bolognesi A, et al., Appl. Phys. Lett., 81.24 (2002): 4646-4648.

- [5] Xu Y., et al., Org. Electron., 12 (2011): 1583-1588.

Table 1 Material property parameters used for simulations

| Material property parameter  | Value                        |

|------------------------------|------------------------------|

| Metal work function          | 5.1eV                        |

| Pentacene Electron Affinity  | 2.6eV                        |

| Pentacene Band gap           | 2.5eV                        |

| Pentacene (Nv Nc, Density of | $2x10^{21}$ cm <sup>-3</sup> |

| states)                      |                              |

| Pentacene Permittivity       | 4.0                          |

|                              |                              |

Fig.1(a) the sketche of the DG-OTFT. (b) Different schematics when Lm exists.

Drain

Source

Source

Fig.2 Transfer characteristics for a top gated OTFT (channel length L=1um) at different

Fig.3 Output characteristics measured at a fixed BG voltage. The total resistance Rtot is calculated from the reciprocal of the slope of the straight lines at different drain voltages.

Fig.4 Overall total resistance (Rtot) with different bottom gate voltages: (a)

Bottom gate bias, VG, bottom (V) Fig.6 The comparative extracted values of VT,top with different Lm.

Fig.7 The compared overall total resistance  $(R_{tot});(a) \quad L_{m=0}, \quad (b)L_{m=0.2um}$ at the VG.top=-10v, VG.bottom=0, VD=-10V.

Fig.8 2D distributions of potential for (a) Lm=0, (b) Lm=0.2um; distributions of hole current density for (c) Lm=0, (d) Lm=0.2um at the VG,top=-10v, VG,bottom=0, VD=-10V.

Fig.9 Driving-current with different misalignment Lm and direction: (a) mismatch to drain, (b) mismatch to sourceat. Herein, VG,top= -10V, VG,bottom= 0V, VD= 1V respectively.

Misalignment between top and bottom gates, Lm (um)

*Fig.*10 with different Driving-current  $V_{G,bottom}=-1V$  $L_{\rm m}$ misalignment at VG,bottom=0V, VG,bottom=1V respectively.

Misalianment between top and bottom gates. Lm (um)

Fig.11 Driving-current with different misalignment Lm with channel length L=1um, L=10um, L=20um respectively.