# Characteristics of Submicron Indium-Tin-Oxide Thin-Film Transistors Fabricated by Film Profile Engineering

Yu-An Huang<sup>1</sup>, and H. C. Lin<sup>1,2</sup>\* and T. Y. Huang<sup>1</sup>

<sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University,

1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

<sup>2</sup>National Nano Device Labs., 26 Prosperity Road I, Hsinchu Science Park, Hsinchu 30078, Taiwan

Phone: +886-3-5712121 Fax: +886-3-5724241 \*email: hclin@faculty.nctu.edu.tw

### Abstract

The first sub-micron (0.4  $\mu$ m) indium-tin-oxide (ITO) thin film transistor (TFT) fabricated with film profile engineering (FPE) is reported in this work. The devices show very low off-state leakage (<10<sup>-13</sup> A), extremely high on/off current ratio (>10<sup>10</sup>), and low subthreshold swing (84 mV/dec). However, severe hysteresis characteristics are also recorded. A model considering the trapping/de-trapping of the induced electrons in the channel is adopted to explain the observation.

## 1. Introduction

Oxide-based transparent electrodes and thin-film transistors (TFTs) have been widely studied and used in the manufacturing of flat-panel displays, in large part due to the low process temperature in preparing the thin films [1]. Nowadays, thin-film transistors using ZnO or amorphous IGZO have achieved remarkable results, with mobility over 10  $\text{cm}^2/\text{Vs}$ , good on/off current ratio, and steep subthreshold slope [2]-[4]. However, all these devices are plagued with a mediocre on-current, which is important for driving devices contained in flat-panel displays or high speed circuits [5].

To raise the on-current, indium-tin-oxide (ITO) appears to be a promising channel material. Actually, with its low resistivity and high transparency, ITO has been widely adopted as a transparent electrode in displays and LEDs. Nevertheless, ITO transistors have seldom been reported. Miyasako et al. first reported an ITO TFT using ferroelectric-gate in 2005, reaching a high on-current of 2.5 mA [6]. Dasgupta et al. fabricated a nanoparticulate ITO transistor in 2008 with an on-current of 0.2 mA but with a mediocre subthreshold slope [7]. In 2009, Kim et al. fabricated an ITO FET by solution-based process, reaching a high on/off current ratio of  $10^5$  but with a mobility of less than 5 cm<sup>2</sup>/Vs [8]. In 2010, Lu et al. reported a homojunction ITO TFT with one-shadow-mask process. The TFT had a good on/off current ratio of 10<sup>6</sup>, with an on-current close to 0.5 mA and good subthreshold slope of 120 mV/dec [9]. The above devices all have significant on-current but suffer from high off current. Also, sub-micron-scale devices have not been reported yet.

In 2013, *Lyu et al.* developed a novel method dubbed "film profile engineering (FPE)" [10] to fabricate ZnO TFTs with sub-micron channel length. In this work, we report on the device performance of ITO TFTs by employing an improved FPE method to fabricate the devices.

# 2. Experimental Details

A. Device Fabrication

Fig. 1 shows the key process flow used to fabricate the ITO

devices. First, SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> were sequentially deposited on a Si wafer to serve as the isolation layers. Then a TiN layer was deposited and patterned to form the bottom metal gate. Next, a SiO<sub>2</sub> sacrificial layer was deposited. After depositing a TiN hard-mask layer, source/drain (S/D) regions were defined with an i-line-based lithographic step. The sacrificial layer was then etched off by selectively wet etching to construct a suspending hard-mask bridge hanging over the bottom gate. The following two deposition steps were the key to realize the FPE concept: (1)  $SiO_2$  with nominal thickness of 50 nm was deposited by plasma-enhanced chemical vapor deposition (PECVD) to serve as the gate dielectric. (2) ITO channel was subsequently deposited by radio-frequency sputtering, under the pressure of 5 mTorr. In the previous FPE study [10], an Al layer was deposited to form S/D contacts in order to improve the device characteristics of ZnO (or a-IGZO) TFTs. Since ITO is a material with sufficiently low resistivity, here we skipped the Al deposition step to simplify the fabrication process. After the SiO<sub>2</sub> passivation layer was deposited, S/D and gate contact holes were opened by inductively-coupled plasma (ICP) etching. From the cross-sectional TEM image (not shown) of an ITO TFT, the sputtered ITO formed an ultra-thin-film of about 15 nm at the central channel.

# **B.** Device Characteristics

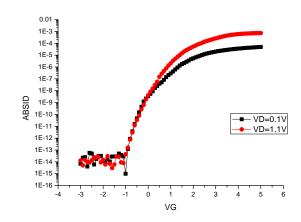

Figure 3 shows the transfer curves of a fabricated ITO TFT with channel width/length of 1 $\mu$ m/0.4 $\mu$ m at V<sub>D</sub>=0.1 V and 1.1V, respectively. We can clearly see that the off current is less than 10<sup>-13</sup> A. The on-current is 0.73 mA at V<sub>D</sub>=1.1 V and V<sub>G</sub>=5 V. The on/off current ratio is over 10<sup>10</sup>. The threshold voltage defined by G<sub>m</sub> method is 1.77V, suggesting an enhancement-mode operation. The field-effect mobility extracted by conventional G<sub>m</sub> method [ref?] is anomalously high (> 450 cm<sup>2</sup>/V-s) and not reasonable (to be discussed latter). Table I gives a brief summary of the characteristics of the reported ITO TFTs and the results obtained in this study. Our sub-micron TFTs show the best sub-threshold swing and on/ off current ratio among the reported results.

TABLE I

A comparison between reported ITO-based TFTs and this study

| (NA: Not available) |           |         |          |                      |                     |

|---------------------|-----------|---------|----------|----------------------|---------------------|

| Year                | Reference | W/L     | SS       | On/off               | V <sub>th</sub> (V) |

|                     |           | (µm/µm) | (mV/dec) | ratio                |                     |

| 2005                | [6]       | 120/40  | NA       | $10^{4}$             | 0                   |

| 2008                | [7]       | 40/5    | 230~425  | $2x10^{3}$           | *                   |

| 2009                | [8]       | 500/100 | NA       | $10^{5}$             | 2                   |

| 2010                | [9]       | 1000/80 | 120      | $10^{6}$             | -0.42               |

| This study          |           | 1/0.4   | 84       | 4.9x10 <sup>10</sup> | 1.77                |

### C. Discussion

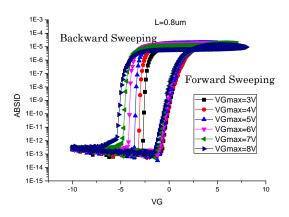

A serious counterclockwise hysteresis phenomenon is observed in the I<sub>D</sub>-V<sub>G</sub> transfer curves (Fig. 3). The hysteresis becomes more severe as the maximum sweeping voltage (V<sub>G.max</sub>) increases. The hysteresis phenomenon can be explained by the trapping/de-trapping model proposed in 2009 by Lin et al. [11]. The model suggests that a portion of the induced electrons during the forward V<sub>G</sub> sweeping would be trapped by the defects sites located in the grain boundaries of the fully-depleted intrinsic polycrystalline channel. The trapping processes offer an additional (charging) current component in the forward sweeping. This is postulated to be the reason responsible for the anomalously high mobility measured in this study. During the backward sweeping, these trapped electrons stay in the channel until the V<sub>G</sub> reaches a sufficiently negative voltage. Higher V<sub>G,max</sub> would charge more electrons in the channel, thus demanding a more negative gate voltage to release the trapped electrons.

#### 3. Conclusion

ITO TFTs fabricated by a process employing the novel FPE concept are shown to exhibit very high on/off current ratio  $(>10^{10})$ , low off current, and steep subthreshold slope. Severe hysteresis phenomenon has been observed and explained by a trapping/de-trapping model. Charging of the traps in the channel is postulated to be responsible for the observation of anomalously high field-effect mobility.

This work was sponsored in part by the Ministry of Science and Technology, Taiwan, under Grant NSC-102-2221-E-009-097-MY3, and NCTU-UCB I-RiCE program, under Grant MOST-103-2911-I-009-302, and the Ministry of Education in

Taiwan under ATU Program.

TiN patterned bottom gate on Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub>. > ≻ Deposition of sacrificial SiO2 and TiN hard mask. ≻ Hard mask patterned and sacrificial layer etched to form suspended bridge. 50nm SiO<sub>2</sub> deposited as gate insulator by PECVD (350°C, 500mTorr). ۶ 50nm ITO channel ۶ deposited by RF sputter (RT, 5mTorr) Deposition of SiO<sub>2</sub> as ≻ passivation layer and contace hole etching.

Fig. 1 Key process flow for the fabrication of ITO thin-film transistors. The framed steps denote the FPE steps.

#### References

- [1] T. Kamiya et al., J. Disp., Technol., Vol. 5, No. 12, pp. 468-482, 2009.

- [2] J. Nishii et al., Jap. J. Appl. Phys., Vol. 44, No. 38, pp. L1193-L1195, 2005

- [3] A. Sato et al., Appl. Phys. Lett., 94, 133502, 2009

- [4] A. Suresh et al., IEEE Electron Device Lett., Vol. 31, No. 4, pp. 317-319, 2010

- [5] T. Kamiya et al., Sci. Technol. Adv. Mater., 11, 044305 (pp?), 2010

- [6] T. Miyasako et al., Appl. Phys. Lett., 86, 16290, 2005

- [7] S. Dasgupta et al., Nanotechnology, 19, 435203, 2008

- [8] H. S. Kim et al., J. Am. Chem. Soc., 131, 10826, 2009

- [9] A. Lu et al., IEEE Electron Device Lett., Vol. 31, No. 10, pp. 1137-1137, 2010

- [10] R. J. Lyu et al., IEDM, pp. 288-291. 2013

- [11] H. C. Lin et al., J. Appl. Phys., 105, 054502, 2009

Fig. 2 Transfer curves of an ITO TFT at V<sub>D</sub>=0.1V and 1.1V

Fig. 3 Transfer curves showing a severe hysteresis effect of the ITO TFT.