# InGaSb Buried-Channel pMOSFET Fabricated by Using Digital Etch Technique

Bing Sun<sup>1</sup>, Zhen-Hua Zeng<sup>1, 3</sup>, Hu-Dong Chang<sup>1</sup>, Qing-Ling Sun<sup>2</sup>,

Sheng-Kai Wang<sup>1</sup>, Wen-Xin Wang<sup>2</sup>, Hong-Gang Liu<sup>1\*</sup>

<sup>1</sup>Microwave Device and IC Department, Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China \* E-mail: liuhonggang@ime.ac.cn <sup>2</sup>Institute of Physics, Chinese Academy of Sciences,

Beijing 100190, China

<sup>3</sup>Advanced Photonics Center, School of Electronic Science and Engineering,

Southeast University, Nanjing 210096, China

# Abstract

In this paper, an InGaSb buried-channel pMOSFET has been fabricated by using digital etch technique for active area definition and gate recess etching. The exposed n<sup>+</sup> InAs cap was etched by UV ozone exposure and dilute HCl dip, while the mesa isolation was obtained by using  $H_2O_2$  and HCl: $H_2O=1:1$  solutions. For a 1 um gate length InGaSb buried-channel pMOSFET, a maximum drain current of about 26.1 mA/mm, a peak transconductance of 9.9 mS/mm, an  $I_{on}/I_{off}$  of about 80, and a SS of about 330 mV/decade has been achieved.

### **1. Introduction**

Due to their superior hole mobilities, antimonide-based compound semiconductors such as GaSb and InGaSb have attracted extensive attentions for next generation CMOS integration [1-5]. Hole mobility as high as  $1500 \text{ cm}^2/\text{V}\cdot\text{s}$  in strained  $In_xGa_{1-x}Sb$  channel has been reported [6], which is much higher than silicon and most of other III-V materials. Recent progress in strained InGaSb channel MOSFET makes InGaSb a good competitor in particular for deeply scaled pMOSFET devices. However, future CMOS requires ultra-scaled device architectures such as multigate or nanowire MOSFETs. A method to precisely etch III-Vs heterostructures containing InAs, InGaAs et al. is highly desirable to realize these structures. Recently, record extrinsic transconductance (2.45 mS/um at  $V_{\text{ds}}$  = 0.5 V) In-As/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOSFETs by using digital etch technique to remove the exposed n<sup>+</sup> InGaAs cap and upper InGaAs cladding layer [7], and it is reported that digital etch technique is a promising etch technique for ultra-scaled device fabrication [8, 9]. In this paper, an InGaSb buried-channel pMOSFET by using digital etch technique for active area definition and gate recess etching has been fabricated and studied.

## 2. Experimental

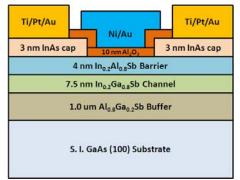

Fig.1 shows the schematic cross-sectional view of the fabricated InGaSb pMOSFET. The starting substrate consists of a 1 um unintentionally doped (UID)  $Al_{0.8}Ga_{0.2}Sb$  buffer, a 7.5 nm UID  $In_{0.2}Ga_{0.8}Sb$  channel, a 4 nm UID  $In_{0.2}Al_{0.8}Sb$  barrier layer, and a 3 nm Si-doped n+ InAs cap sequentially grown on a semi-insulting GaAs (100) substrate by MBE technology. As shown in Fig. 2, after degreased in acetone and IPA, five cycles of digital etch were performed for the active area definition to selectively re-

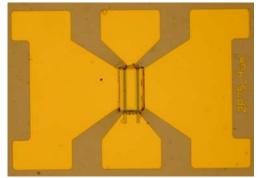

move InAs cap, InAlSb barrier, and InGaSb channel, and a part of AlGaSb buffer, H2O2 for 1 min was used for oxidation and a HCl:H<sub>2</sub>O<sub>2</sub>=1:1 solution for 20 sec was used for oxidation removal, then the n<sup>+</sup> InAs cap layer was selectively removed through two cycles of UV ozone exposure and dilute HCl dip, UV ozone exposure for 10 min was used for oxidation of the  $n^+$  InAs cap, a HCl:H<sub>2</sub>O=1:10 solution for 30 sec was used for oxidation removal. After an additionally HCl:H<sub>2</sub>O<sub>2</sub>=1:10 solution for 30 sec, the sample was immediately transferred into the Beneg TFS200 ALD chamber, 10 nm Al<sub>2</sub>O<sub>3</sub> was deposited at 300 °C as gate dielectric by using TMA and H<sub>2</sub>O as precursors. Ni/Au gate electrode was then e-beam evaporated, followed by a lift-off process. After that, Ti/Pt/Au source and drain (S/D) electrode was e-beam evaporated, followed by lift-off process, Al<sub>2</sub>O<sub>3</sub> is selectively etched by BOE prior to metal evaporation. Finally, Ti/Au electrode was e-beam evaporated, followed by lift-off process, for device performance characterization. Fig. 3 shows the microphotograph of the fabricated InGaSb buried-channel MOSFET

Fig.1 Schematic cross-sectional view of the fabricated MOSFETs

| MBI | epitaxial wafer                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------|

| Φ   | Degreased in acetone and IPA.                                                                                                |

| Q   | Active area definition                                                                                                       |

| \$  | Gate recess pattern and InAs cap removal by digital<br>etch                                                                  |

| 4   | Al <sub>2</sub> O <sub>3</sub> , deposition by ALD (TMA-H <sub>2</sub> O)                                                    |

| ¢   | Ni/Au gate electrode deposition by lift-off process                                                                          |

| ¢   | Ti/Pt/Au S/D electrode deposition by lift-off process, $\rm Al_2O_3$ is selectively etched by BOE prior to metal evaporation |

| Ø   | M1 electrode deposition by lift-off process                                                                                  |

| Me  | asurement                                                                                                                    |

Fig.2 Key process flow for InGaSb pMOSFET

Fig. 3 Microphotograph of the fabricated MOSFET

# 3. Results and Discussion

The etch rate per cycle of digital etch was measured with Park x-70 atomic force microscope in non-contact mode after multiple cycles of digital etch were performed. For active area definition, after five cycles of digital etch by using  $H_2O_2$  and HCI: $H_2O=1:1$  solution, the mesa height was about 52 nm, indicating the InAs cap, InAlSb barrier, and InGaSb channel, and a part of AlGaSb buffer were selectively removed. For gate recess pattern and InAs cap removal, after two cycles of digital etch by using UV ozone exposure and dilute HCl dip, about 2.5 nm thick InAs cap layer was selectively removed. The residual InAs cap over the channel region was used to protect InAlSb barrier from been oxidized by air, and the additionally dilute HCl dip was used to etch the residual InAs cap that oxidized by air.

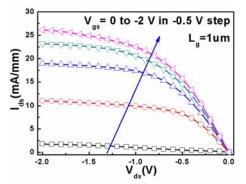

The device performance of the fabricated InGaSb buried channel pMOSFET was characterized by using HP 4155A semiconductor parameter analyzer. Fig. 4 shows the DC output characteristic of a 1 um gate length ( $L_g$ ) InGaSb pMOSFET with a gate bias ( $V_{gs}$ ) from 0 to -2 V in steps of -0.5 V, a maximum drain current of about 26.1 mA/mm is obtained at a  $V_{gs}$  of -2 V and a drain bias ( $V_{ds}$ ) of -2 V.

Fig. 4 I<sub>d</sub>-V<sub>d</sub> characteristics of the fabricated MOSFET.

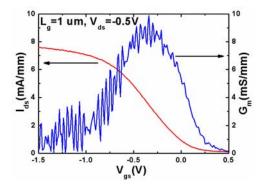

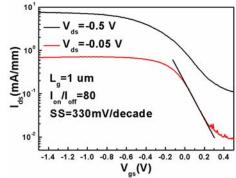

As shown in Fig. 5, the drain current and extrinsic transconductance vs. gate bias of the same device was measured and calculated with a  $V_{ds}$  of -0.5 V, a peak transconductance ( $G_m$ ) of 9.9 mS/mm is obtained at a  $V_{gs}$  of -0.34 V. Fig. 6 exhibits the transfer characteristics of the same device with  $V_{ds}$  at -0.5 V and -0.05 V, respectively, the on-current to off-current ratio ( $I_{on}/I_{off}$ ) is 80, and the sub-threshold swing is 330 mV/decade, the  $I_{on}/I_{off}$  and SS are largely limited by the large leakage current of the Al-

GaSb buffer layer.

Fig. 5 The drain current and extrinsic transconductance vs. gate bias for the fabricated MOSFET with 1 um gate length at  $V_{ds} = -0.5$  V.

Fig. 6  $I_D$ - $V_G$  characteristic of the fabricated InGaSb channel pMOSFET.

## 4. Conclusion

In this paper, an InGaSb buried-channel pMOSFET has been fabricated by using digital etch technique for active area definition and gate recess etching. The exposed n<sup>+</sup> InAs cap was etched by UV ozone exposure and dilute HCl dip, while the mesa isolation was obtained by using H<sub>2</sub>O<sub>2</sub> and HCl:H<sub>2</sub>O=1:1 solutions. For a 1 um gate length InGaSb buried-channel pMOSFET, a maximum drain current of about 26.1 mA/mm, a peak transconductance of 9.9 mS/mm, an I<sub>on</sub>/I<sub>off</sub> of about 80, and a SS of about 330 mV/decade has been achieved.

#### Acknowledgment

This work is supported by the National Basic Research Program of China under Grant No. 2010CB327501 and the National Natural Science Foundation of China under Grant No. 61106095.

### References

- [1] Z. Yuan et al., Appl. Phys. Lett., 100, 143503 (2012).

- [2] A. Ali et al., Appl. Phys. Lett., 97, 143502 (2010).

- [3] A. Nainani et al., IEDM Tech. Dig., 2010, p.138.

- [4] L. Xia et al., Appl. Phys. Lett., 98, 053505 (2011).

- [5] M. Xu et al., IEEE EDL, 32(7), 2011, p.883.

- [6] B. R. Bennett et al., Appl. Phys.Lett., 91,042104 (2007).

- [7] S. Lee et al., in Proc. VLSI Symp., 2013, p.T246.

- [8] J. Q. Lin et al., IEEE EDL, 35(4), 2014, p.440.

- [9] A. Alian et al., ECS Journal of Solid State Science and Technology, 1 (6), 2012, p.310